- 1回目: 開発環境の準備

- 2回目: Hello Worldプロジェクト

- 3回目: PSのGPIOでLチカ

- 4回目: PLのAXI GPIOでPSからLチカ

- 5回目: PLだけでLチカ <--- 今回の内容

- 6回目: 自作IPでLチカ

- 7回目: ブートイメージを作る

- 8回目: Linux起動する

- 9回目: Linuxカーネルを少しカスタマイズする

- 10回目: LinuxのRootFSをカスタマイズする / PythonでHello World

- 11回目: LinuxユーザアプリケーションでLチカ

- 12回目: LinuxカーネルモジュールでLチカ

- 13回目: LAN(Ethernet 0)を使う

- 14回目: Linuxユーザアプリをデバッグする / RootFSに取り込む

- 15回目: Linux起動時にアプリケーションを自動実行させる

- 16回目: Linuxから自作IPをUIOで制御する

- 17回目: Linuxで自作IPのデバイスドライバを作る

- 18回目: IoT化してスマホからLチカ

この記事の内容を4分で見る ( https://www.youtube.com/watch?v=H5Qb428D7Sg )

環境

- 開発用PC: Windows 10 64-bit

- Vivado 2017.4 WebPACKライセンス

- Xilinx SDK 2017.4

- ターゲットボード: ZYBO (Z7-20)

Windows環境は1回目を参照。

PLだけでLチカ

今回は、PLだけでLEDチカチカを実装します。PSは一切使いません。つまり、Zynqを通常のFPGAのように使います。

まずは、verilogコードからシンプルにLチカさせてみます。その後に、作ったverilogコードをIPとして使用して、IP Integratorから使ってみようと思います。(IP化については次回ちゃんとやろうと思います。)

Vivadoプロジェクトの準備

今回は、新しくプロジェクトを作ろうと思います。2回目の内容を参考に、ZYBOボードを指定してVivadoプロジェクトを作成してください。

Verilogコードを書く

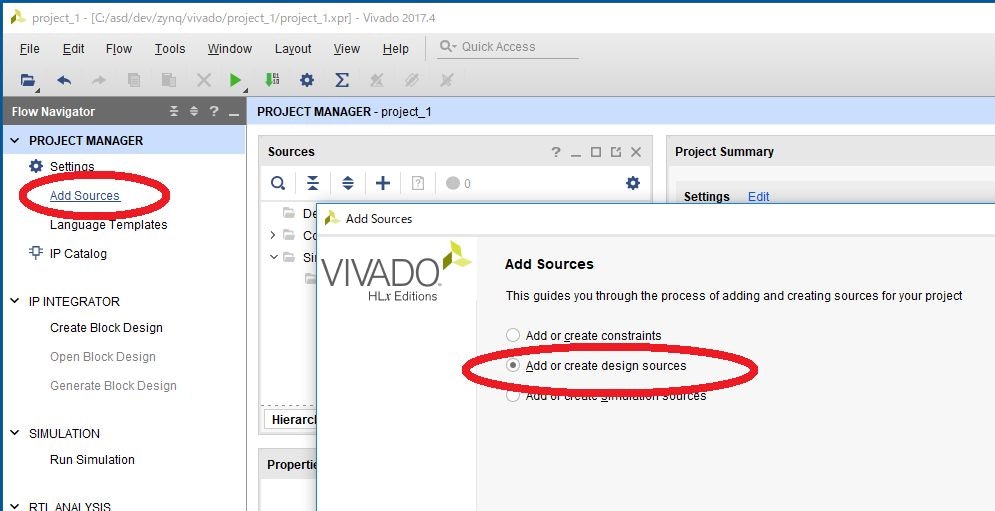

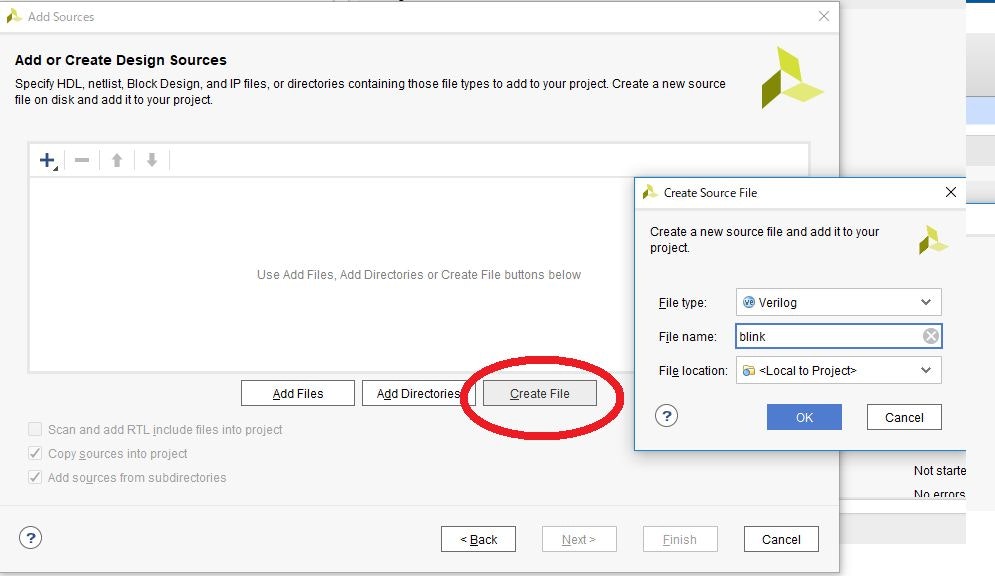

Verilogコードを追加します。左側のFlow Navigator -> PROJECT MANAGER -> Add Sourcesをクリックして、「Add or create design sources」を選びます。次の画面で、「Create File」を選び、ファイル名を"blink"とします。その後、モジュール名やIOポート定義を追加できますが、コードで書くので何もせずにOKします。

Sourcesタブから、今作成したblink.vをダブルクリックして、以下のように実装します。このモジュールは入力としてCLKを持ちます。このクロックは125MHzを想定します(理由は後述)。そして、4bitのOUTに出力します。OUTは全ビット同じ値で、1秒ごとにOn/Offします。

記事を書いた後に気付いたのですが、OUTという名前は予約語なのでよろしくないです。別の名前を使うようにしてください。

module blink(

input CLK,

output [3:0] OUT

);

parameter CNT_1SEC = 27'd124999999; // 125MHz clk for 1sec

reg [26:0] cnt = 27'd0;

reg onoff = 1'd0;

always @(posedge CLK) begin

if (cnt == CNT_1SEC) begin

cnt <= 27'd0;

onoff <= ~onoff;

end

else begin

cnt <= cnt + 27'd1;

end

end

assign OUT = {onoff, onoff, onoff, onoff};

endmodule

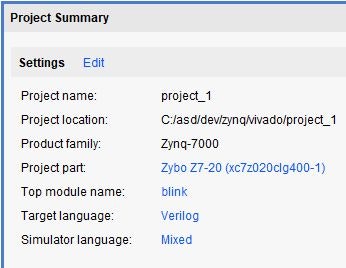

このblink.vがTop moduleとして自動的に設定されます。

ピンアサインをする

ピンアサインの決め方

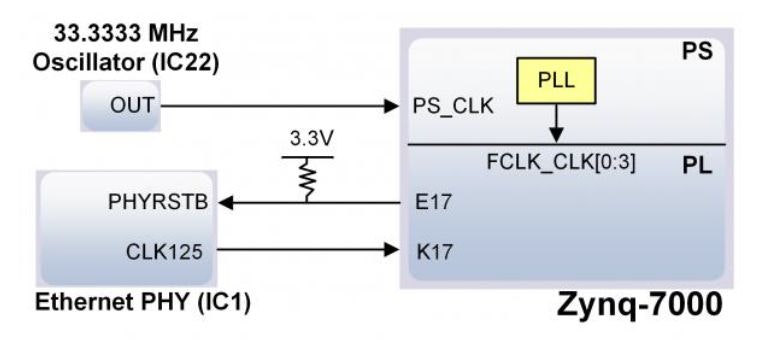

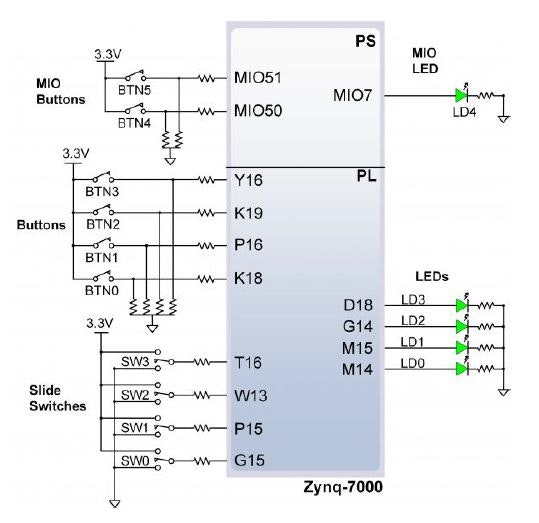

先ほど実装したモジュールは、CLK入力と、4本の出力を持ちます。ZYBOボード上で適切なピンを探します。ZYBO-Z7のリファレンスマニュアルを確認します。すると、クロックとしては、125MHzがK17に入っていることが分かります。また、LEDはM14、M15、G14、D18に接続していることが分かります。(LEDに関してはボード上のシルクでも確認できますし、前回使ったのと同じです。) ちなみに、前回まではFCLK_CLK0というクロックがありました。これは、PSが内部のPLLを使って作り出しているものです。今回はPLのみなので、これは使えません。

制約ファイルを作る

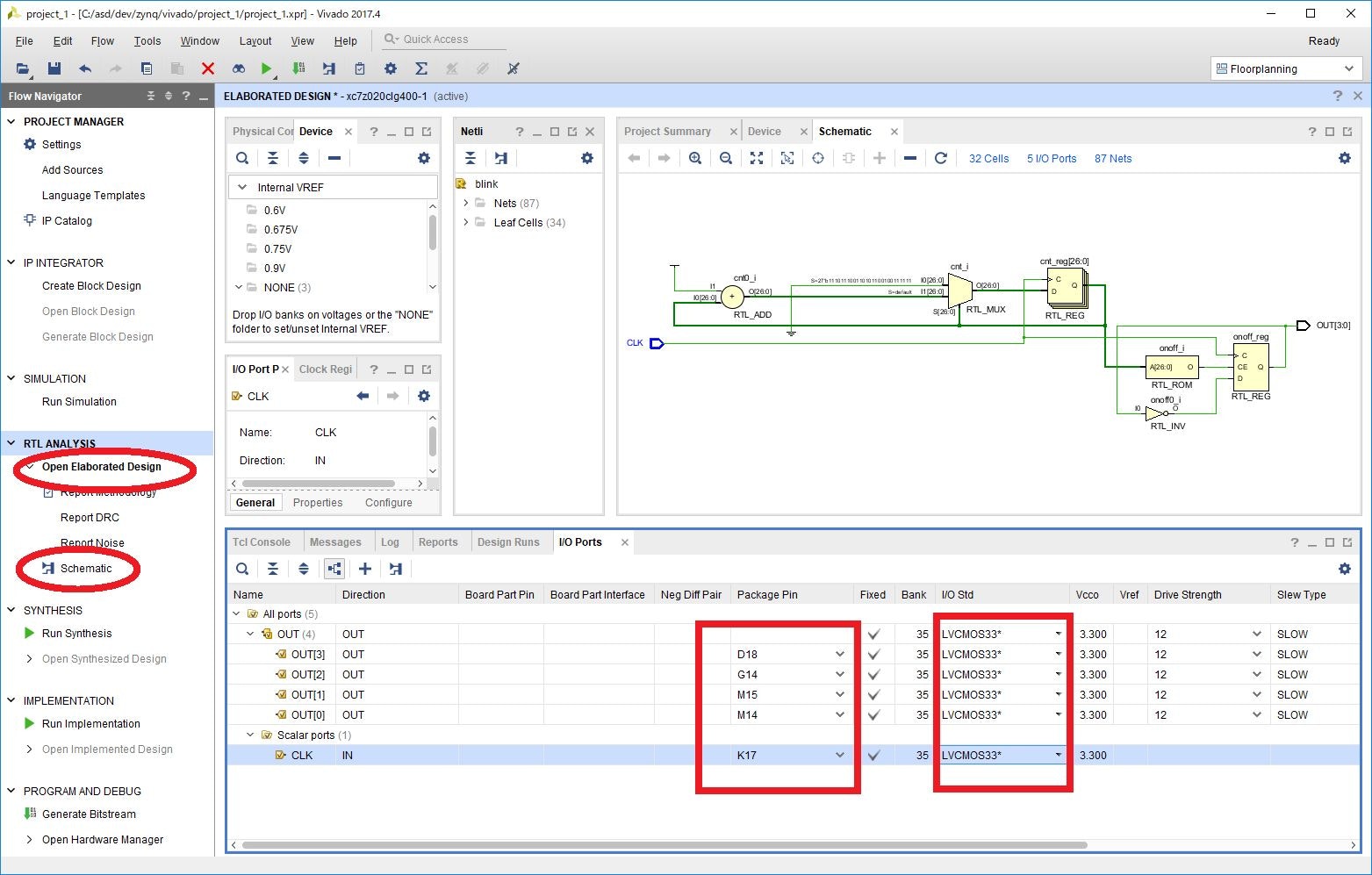

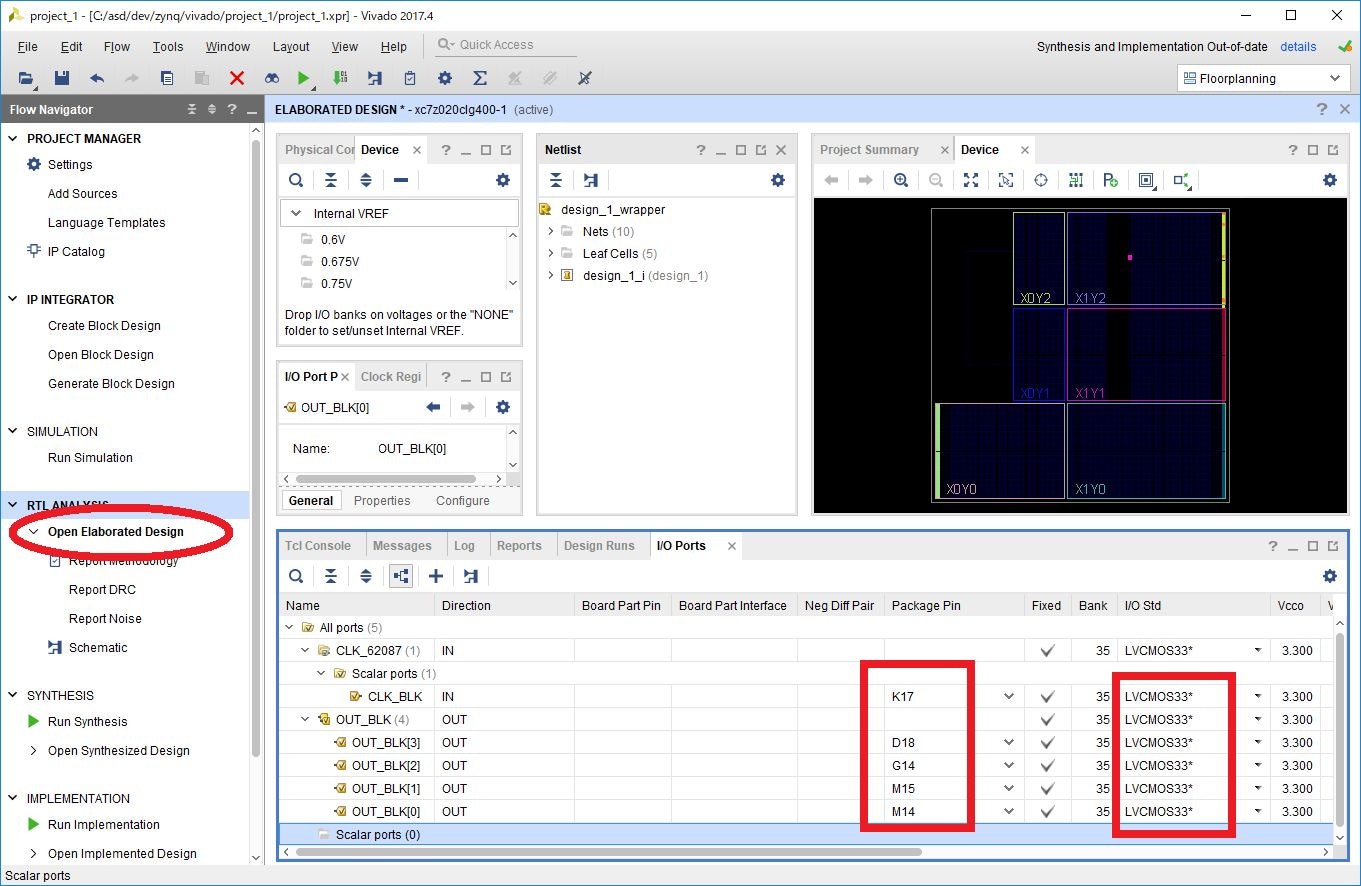

ピンアサインするというのは、配置配線ツールにとっては、「アサインされたピンに接続しなくてはいけない」という制約になります。ピンアサイン(制約)を定義する制約ファイル(xdcファイル)を作ります。Flow Navigator -> RTL ANALYSIS -> Open Elaborated Designをクリックします。その後、Schematicを開くと、下記のようにRTLレベルでのブロック図を確認できます。現在、blink.vがTop moduleとして使われているので、blink.vで定義したIOポートであるCLK, OUTがそのまま外部とのIOとなります。これらのIOポートに実際にピンを割り当てます。Schematicを開くと自動的に画面下部にI/O Portsという画面が表示されているはずなので、ここを以下のように設定します。(IOレベルはLVCMOS33じゃないとエラーになりました)

設定したら、Ctrl-sでこの制約を保存します。ファイル名は適当にblink.xdcとしておきます。

実行する

Flow Navigator -> PROGRAM AND DEBUG -> Genate Bitstreamをクリックして、論理合成、配置配線、ビットストリームの作成までまとめて実行します。

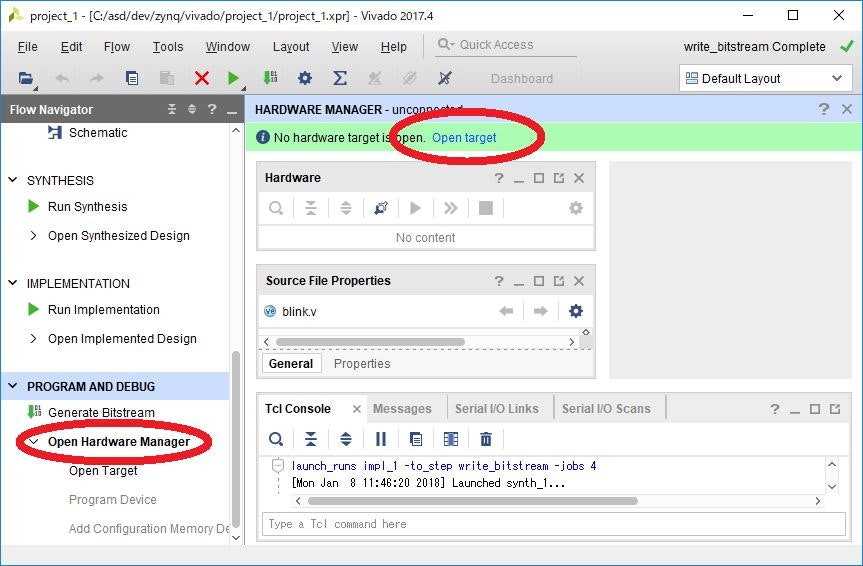

完了後、Open Hardware Managerします。HARDWARE MANAGERでOpen Target (Auto Connect)し、Zynqに接続します。その後、Program deviceで、今作成したビットストリームファイルを書き込みます。 すると、1秒間隔で4つのLEDが同時にチカチカ点滅するはずです。

blink.vをIP(モジュール)として使う (簡易版)

そこそこの規模になると、複数のIPを組み合わせてシステムを作るというのが一般的だと思います。先ほど作ったblink.vをモジュールとして取り込むということをやってみようと思います。Vivado上でIP INTEGRATORを使うことで、簡単に行うことが出来ます。(IP INTEGRATOR自体は前回までも、PSを搭載するために使っていました。)

補足

ここで紹介する方法は、いわゆる「IP化」ではありません。IPとしてパッケージにする方法については次回説明します。

ここで紹介する方法は「モジュール化」と表現するのが正しいと思うのですが、「RTLモジュールをモジュール化」という分かりづらい表現になってしまうので、あえて「IP化(簡易版)」と記載しています。

ベースとなるブロックデザインを用意する

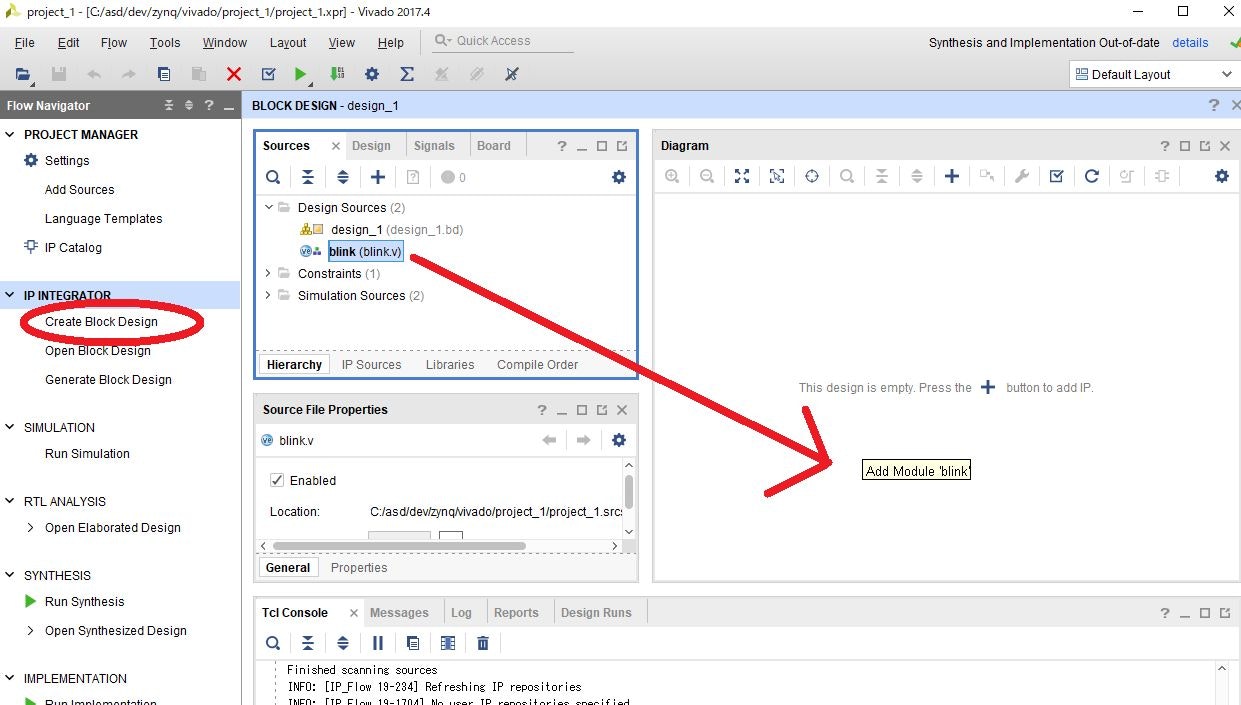

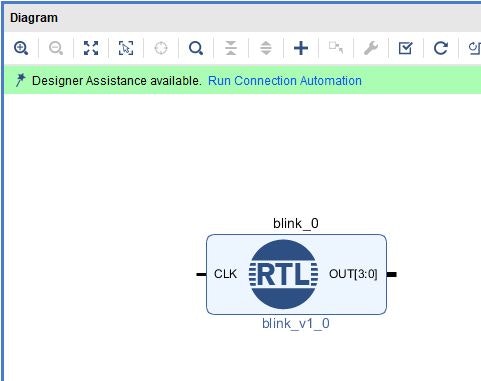

Flow Navigator -> IP INTEGRATOR -> Create Block Designをクリックして、新しいブロックデザインを作ります。名前は適当にdesign_1としておきます。Diagramビューを見ると、最初は何もない空っぽです。そこに、Sourcesからblinkをドラッグ&ドロップします。

ブロックデザインのIOポートを用意する

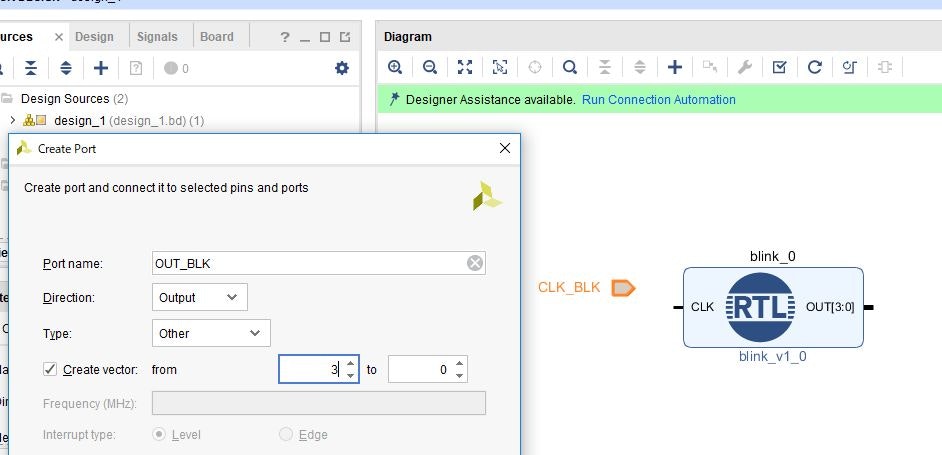

最終的には、今作成したブロックデザインを外部のピンに接続したいのですが、現状、このブロックデザイン(design_1)はIOを持っていません。CLKとOUTはdesign_1内部のblinkIPのIOになります。このブロックデザイン(design_1)としてのIOを用意して、それにCLKとOUTを接続します。それぞれ、CLK_BLKとOUT_BLKとします。(名前は同じでもいいですが、接続関係を理解するために別の名前にしました)。

ポートを追加するためには、Diagramビュー上で右クリックして、Create Portを選びます。OUTは4bitなので、Create vectorにチェックをします。また、向きもOutputにします。その後、Diagramビュー上でマウスをドラッグ&ドラッグして接続します。

(または、blinkモジュールの端子上で右クリックして、「Make External」を選択でもOKです)

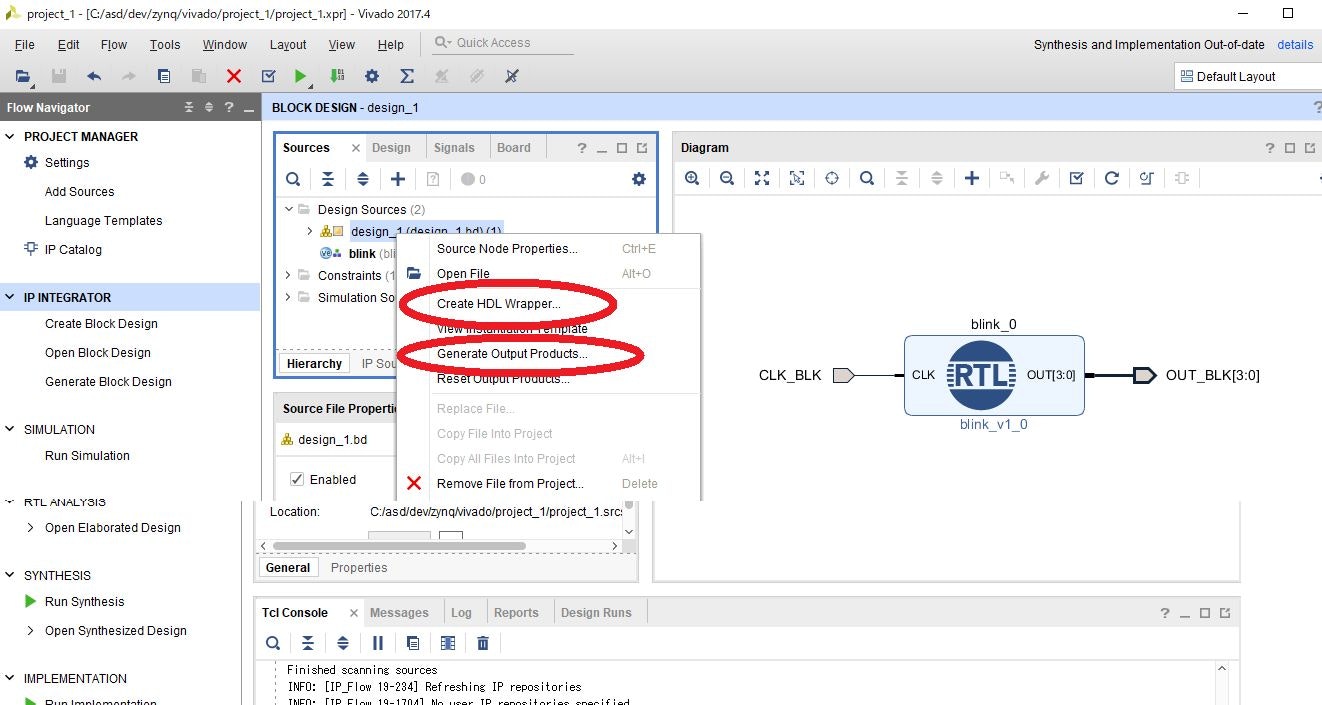

ブロックデザインのコードとWrapperを作る

前回までのPSと同様の手順です。Sourcesタブ上のdesign_1で右クリックして、Generate Output ProductsとCreate HDL Wrapperします。

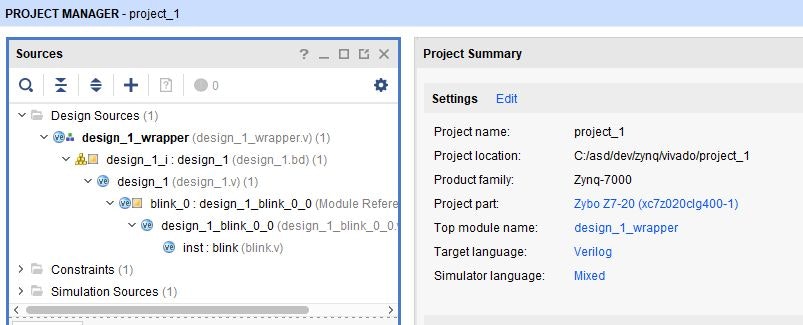

すると、階層構造が以下のように変わります。また、Top moduleが自動的にdesign_1_wrapperになります。

ピンアサインをする

先ほどと同様に、Open Elaborated Designを選びます。デザインを作り直しますか? みたいなことを聞かれるので、OKをして、以下のように設定して、Ctrl-sで保存します。

ノート

今回のように、後からboard.xdcを編集すると、xdcファイルには制約(ピン配置)がどんどん追加されていきます。先ほど設定したピン配置設定も残ったままです。今回は害はありませんが、気になる場合は直接xdcファイルを編集して削除してください。(他に方法はあるかもしれませんが。)

また、ZYBO用の制約ファイルがDigilentから配布されています(https://github.com/Digilent/ZYBO/tree/master/Resources/XDC )。これをベースに自分が使うピンだけ編集して使うというのもありだと思います。しかし、配布されている制約ファイルは初代ZYBO用です。僕が今使っているZ7-20とは異なるので、自分で作ることにしました。

(追記: https://github.com/Digilent/digilent-xdc/blob/master/Arty-Z7-20-Master.xdc にあった)

実行する

先ほどと同様に、ビットストリームを作成して書き込むことで、LEDがチカチカするはずです。ちなみに、書き込むビットストリームのファイル名は、先ほどはblink.bitでしたが今回はdesign_1_wrapper.bitに代わっているはずです。

参考資料