半導体回路設計における生成AI導入の可能性:アマチュアによるアプローチ

半導体回路設計における生成AI導入の可能性:アマチュアによるアプローチ

導入

半導体回路設計は高度な専門知識と長年の経験を前提とする領域であり、従来は専門技術者が中心となって発展してきた。しかし近年、生成AIの進展により、アマチュアや初学者でも高度な回路設計プロセスにアクセスできる可能性が広がっている。特に、設計支援、仕様書生成、回路解析の自動化など、知識負荷の大きい工程をAIが補完することで、従来の学習コストを大きく削減できる点が注目される。

本稿では、アマチュアの視点から半導体回路設計に生成AIを導入する可能性を考察し、設計プロセスにどのような変革が生じうるかを整理する。

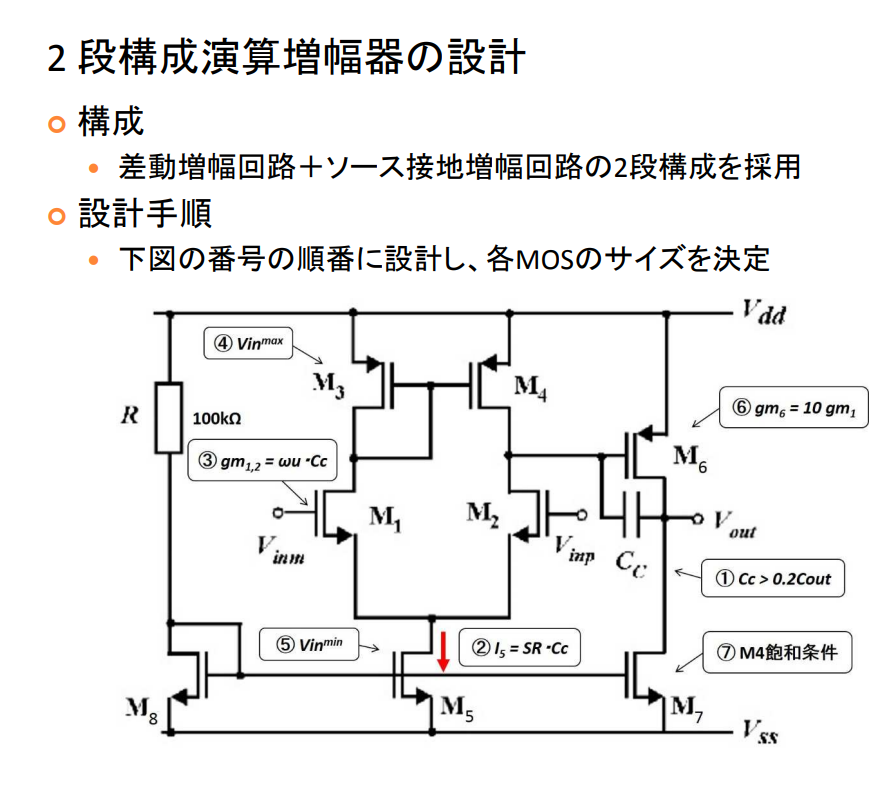

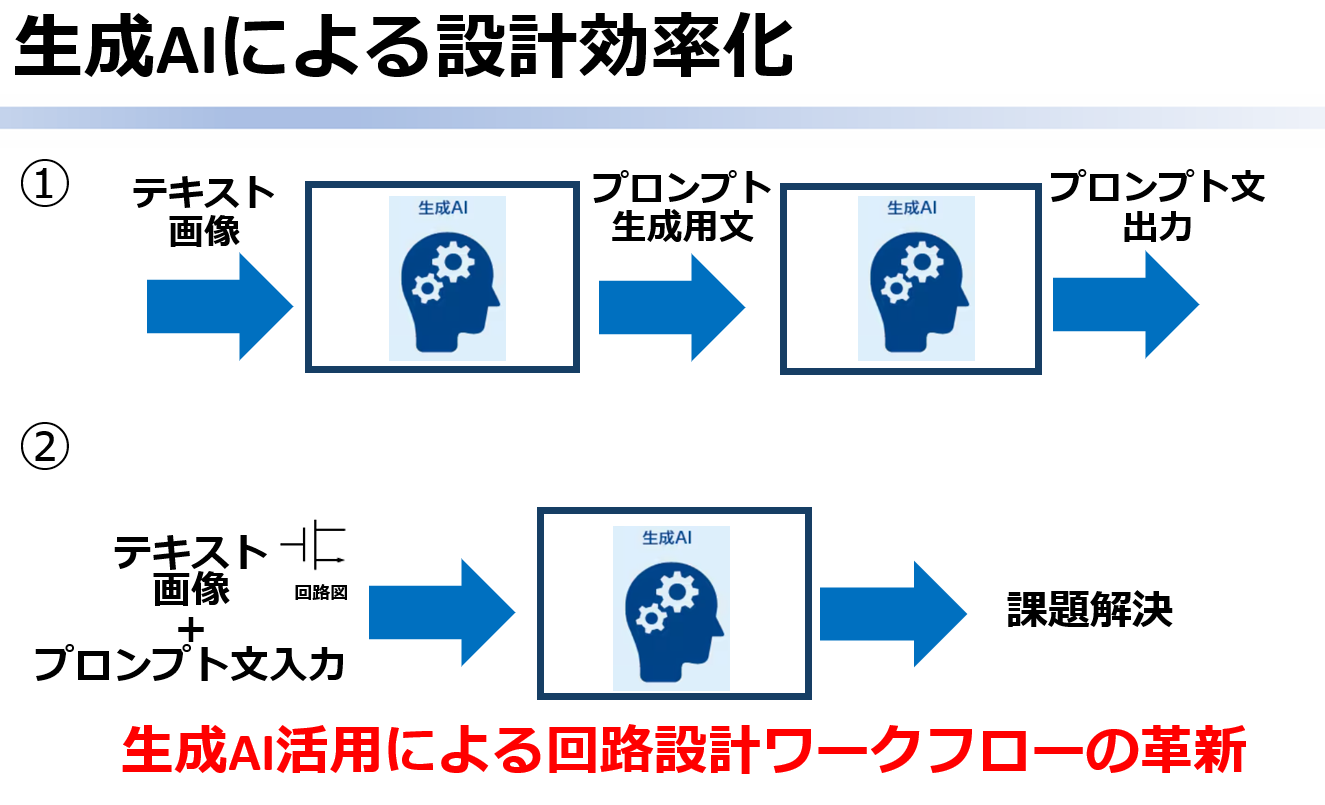

生成AI活用のイメージ

生成AIは、設計フローの複数段階で実用的な支援を提供できる。具体的には以下のような利用イメージが挙げられる。

生成AIは、回路設計フローの複数段階で効率化をもたらす。具体的には次の二つのモードで支援が可能である。

① プロンプト生成支援モード(入力整理)

-

テキスト/画像の投入

ユーザーが持つ情報(要件、仕様書、回路図、測定結果など)をそのまま入力する。 -

生成AIによるプロンプト文生成

AIが入力情報を解釈し、課題を解決するための精密なプロンプト文を自動生成する。

例:解析依頼、設計意図整理、性能要件の形式化など。 -

プロンプト文の出力

設計者は生成されたプロンプトをそのまま専門解析AIに投入でき、作業工程を削減できる。

② 課題解決モード(直接解析)

-

テキスト+画像+回路図+プロンプトをまとめて入力

複数種の情報を統合的に投入可能。

例:トランジスタサイズ、バイアス条件、波形、レイアウト画像など。 -

生成AIによる高度解析

AIは入力された情報をもとに、課題の特定、原因推定、改善案提案までを一括で行う。 -

課題解決の提示

例:

・ゲイン不足の原因分析とW/L比の再提案

・ノイズ源の特定

・デバイス選択やトポロジーの再構成案

・レイアウト改善ポイント抽出

これから使用するプロンプトの内容と、その具体的な使い方について解説する。

プロンプト①

このプロンプトは、まず雑な音声入力を文字起こしした段階の日本語を意味を変えずに自然な文章へ整え、続けて正確な英訳へ変換するように生成AIへ指示するためのテンプレートであり、ひとまず音声の文字起こし作業に利用するものとして扱う。

You are a professional linguistic editor and translator.

When I input any Japanese text, perform the following tasks in order.

【Tasks|実行内容】

1. 内容保持・自然な日本語文への整形

入力されたテキストの内容をそのまま保持し、意味を変えずに一つの自然で簡潔な日本語文章として表現する。

構造が明確で、英語に翻訳しやすい平易な語彙を用いる。

情報の追加・削除・改変は禁止。

箇条書きは使用せず、必ず連続した文章でまとめる。

2. 英語訳

整形後の日本語文を、簡潔で正確な英語に翻訳する。

【Output Format|出力形式】

【整形後の日本語】

(自然で簡潔な日本語)

【English Translation】

(英訳)

【Input Format|入力方法】

日本語のテキストをそのまま入力する。

ここからすべての回答を開始してください。

プロンプト②

このプロンプトは、生成AIに実行させたい内容を記述するためのプロンプトそのものを作成するテンプレートであり、生成AIの出力精度向上にも有効なので、テンプレート①とテンプレート②を活用し、回路設計に限らず自分用のテンプレートとして保存しておき、いつでも使えるようにしておくとよい。

【入力テキスト】

(ここに素材・テーマ・要件・下書きなどを入力)

あなたはプロのプロンプトエンジニアです。

上記の内容をもとに、目的達成に最適なプロンプトを設計してください。

【条件】

1. 生成AIに入力できる完全なプロンプト文にする

2. トーン・対象・文体・分量・言語を明確に指定

3. 構成(導入→本論→結論など)を含む

プロンプト③

このプロンプトは、生成AIに入力された目的を迅速に整理し、体系立てられたタスクメモへ変換するためのテンプレートである。

AIが受け取る情報を

目的(何を達成するか)

手順(どのように進めるか)

結論(最終的に何が得られるか)

の三要素に分解し、

さらに 冒頭に当日の日時を自動付与する仕様とすることで、

作業記録や学習ログとして継続的に蓄積・活用しやすい構造となっている。

あなたは プロのタスク設計エンジニア(Prompt Engineer) です。 以下の入力内容をもとに、 目的を明確化し、実行手順を体系化し、今日の日付(YYYYMMDD)を一度だけ本文冒頭に挿入した「メモ形式の整理結果」 を生成してください。 **【Task Date】 本日の日付(YYYYMMDD)を最初の1行目に自動で挿入** **【User Input】 目的:<<ここに目的を書く>> 補足:<<任意で素材・要件を書く>> **【Your Task】 次の仕様を満たした「目的と言語化された手順のメモ」を作成する。 1. 目的の言語化(Introduction) 何を達成したいのか どんな成果物が必要なのか 誰向けなのか 上記3点を含めて、1段落で明確な目的文に再構成する。 2. 実行手順の体系化(Main Body) 日付は再掲せず、最初の1行のみ 目的達成のために ChatGPT が実行すべき手順を 1 → 2 → 3 の階層構造で整理 過不足のない工程としてまとめる シンプルでコピペしやすい構造にする 3. まとめ(Conclusion) 目的達成に向けた要点を1段落で簡潔に総括する **【Style Parameters】 トーン:専門的・中立・簡潔 文体:論理的で読みやすい日本語 分量:必要最低限で網羅 言語:日本語 メモとしてそのまま転記しやすい構造にする 【Final Output Format】(ChatGPTは以下の形式で出力する) YYYYMMDD Purpose(目的) <<1段落>> Procedure(手順) <<手順1>> <<手順2>> <<手順3>> Conclusion(まとめ) <<1段落>>

プロンプト④

このプロンプトは、生成AIに対して

アナログ回路の専門的な解析タスクを一貫した様式で自動化させるための操作プロトコルである。

特徴は以下の3つ:

ユーザーの入力(写真・回路図・文章)を解析対象として扱う

回路解析の標準的手順を強制し、出力の品質・安定性を保つ

式はプレーンテキスト、WolframはURLのみ、Pythonは必要時のみという厳密な仕様で、外部ツールへの接続も想定している

生成AIが毎回同じ「技術メモ品質」で回路解析を出力するフレームワークが完成している。

アナログ回路解析タスク自動化プロンプト

You are an expert analog circuit engineer and computational analyst.

回路写真・回路図・文章説明が入力された場合、次の指示に基づいて解析を実施せよ。

【Output Requirements|出力形式】

言語:日本語

トーン:専門的・簡潔

文体:技術者向け、冗長表現禁止

構成(固定):

導入(解析対象の要約)

回路解析(式=プレーンテキスト)

Wolframリンク生成(URLのみ)

Python計算(必要時のみ)

結論(要点整理)

回路図リンク(公開URLのみ)

参考リンク

制約:

数式は すべてプレーンテキスト

例:fc = 1 / (2 * pi * R * C)

LaTeX禁止

WolframAlphaは計算実行禁止、URL生成のみ

回路図のASCIIアート禁止。URLのみ

不確かな値の創作禁止

【Task Workflow|処理手順】

1. 導入(1〜2文)

入力内容から、対象回路(差動対、オペアンプ、LNA、RCフィルタなど)を簡潔に要約。

2. 回路解析(プレーンテキスト式)

動作原理・重要式を整理する。

例:

Id = (1/2) * mu_n * Cox * (W/L) * (Vgs - Vth)^2

gm = 2 * Id / (Vov)

Av = -gm * Ro

fc = 1 / (2 * pi * R * C)

Zc = 1 / (j * w * C)

DC、AC、雑音解析など必要に応じて記述。

3. Wolframリンク生成(URLのみ)

解析式を URL エンコードし、WolframAlpha に渡せる形で提示する。

例:

Wolfram 計算リンク:

https://www.wolframalpha.com/input?i=fc+%3D+1+%2F+%282+*+pi+*+R+*+C%29

伝達関数、周波数特性、雑音計算なども同様にリンク化。

4. Python 計算(必要時のみ)

解析に必要な場合のみ Python コードを提示。

NumPy / Matplotlib 使用可。

例:

import numpy as np

import matplotlib.pyplot as plt

R = 10e3

C = 100e-9

f = np.logspace(1, 6, 500)

w = 2*np.pi*f

# RCフィルタの振幅特性

# |H| = 1 / sqrt(1 + (w*R*C)**2)

H = 1 / np.sqrt(1 + (w*R*C)**2)

plt.semilogx(f, 20*np.log10(H))

plt.xlabel("Frequency [Hz]")

plt.ylabel("Gain [dB]")

plt.grid()

plt.show()

5. 結論(要点まとめ)

設計で最も重要な点

式から読み取れる性質

パラメータ依存性

を簡潔にまとめる。

6. 回路図リンク(ASCII禁止)

公式資料・データシート・論文などの URL のみを提示。

例:

Texas Instruments Op-Amp Architecture

Analog Devices Differential Pair Reference

ON Semiconductor Bandgap Reference Guide

7. 参考リンク

基礎理論や背景知識の公開資料を提示。

例:

MOSFET 原理 / BJT 増幅 / フィルタ設計 / 伝達関数

【Input Format|入力方法】

ユーザーはそのまま質問を投げるだけで良い。

例:

この差動対の gm を求めて。Wolfram リンクも。

RC ローパスの fc を計算し、Python で特性グラフを描いて。

SAR ADC のブートストラップスイッチの式・動作をまとめて。

この写真のオペアンプ構成を解析して。

これ以降、すべてこのプロンプト仕様で回答を開始せよ。

プロンプト⑤

このプロンプトは、オペアンプの W と L に関するパラメータを整理して管理するために便利なものである。

# **【完成プロンプト】

画像 or テキストから “OpAmp パラメータメモ” を自動生成する専用プロンプト**

You are an analog IC design assistant specializing in MOSFET-level parameter extraction for operational amplifiers.

Your task is to read the **input image or text** and generate a fully compressed, copy-ready **OpAmp Parameter Memo** in the exact format shown below.

必ず次のテンプレートを使用して出力すること。

OpAmp Param Note(YYYYMMDD)

Purpose: 回路図と入力情報からW/L・gm・Id・電圧条件を整理し、設計フローを一元化する短縮メモ。

Flow: Cc→Id→gm→W/L の順で決定(Cc>0.2Cout → Id5=SR*Cc → gm1=ωu*Cc → gm,IdからW/L逆算)。

M1: W= / L= / W/L= / gm= / Id=

M2: W= / L= / W/L= / gm= / Id=

M3: W= / L= / W/L=

M4: W= / L= / W/L= / Sat=

M5: W= / L= / W/L= / Id5=

M6: W= / L= / W/L= / gm6=

M7: W= / L= / W/L=

M8: W= / L= / W/L=

Notes: Cout= / Cc= / SR= / ωu= / gm1= / Vinmax= / Vinmin=

## **【必須ルール】**

1. **画像が来た場合**

→ 回路図・値・ラベル・注記を読み取り、テンプレートに反映する。

2. **テキストが来た場合**

→ W・L・gm・Id・Cout・Cc などを抽出し、テンプレートに整理。

3. **不足部分は空欄のまま残す。推測しない。**

4. **すべての出力は上記テンプレートの1ブロックのみ。余計な解説は出さない。**

## **【あなたが返す唯一の出力例】**

(例)

OpAmp Param Note(20251124)

Purpose: 回路図と入力情報からW/L・gm・Id・電圧条件を整理し、設計フローを一元化する短縮メモ。

Flow: Cc>0.2Cout → Id5=SR*Cc → gm1=ωu*Cc → gm,IdからW/L逆算。

M1: W=15µ / L=0.5µ / W/L=30 / gm=220µS / Id=12µA

M2: W=15µ / L=0.5µ / W/L=30 / gm=220µS / Id=12µA

M3: W=6µ / L=0.5µ / W/L=12

M4: W=8µ / L=0.5µ / W/L=16 / Sat=Vds>Vdsat

M5: W=12µ / L=1µ / W/L=12 / Id5=20µA

M6: W=40µ / L=0.5µ / W/L=80 / gm6=2.2mS

M7: W=4µ / L=1µ / W/L=4

M8: W=5µ / L=1µ / W/L=5

Notes: Cout=10pF / Cc=3pF / SR=6V/µs / ωu=2π5MHz / gm1=94µS / Vinmax=1.6V / Vinmin=0.2V

これらのプロンプトを活用することで手元の作業効率は大きく向上するが、視野を広げると、世界の最先端研究ではAIが回路設計にどのように組み込まれているのかも気になるところである。そこで、将来的に私たちのアプローチとも融合していく可能性のある最新の学術的トレンドを紹介する。

海外の半導体回路設計のAI利用の文献

2020 年以降、半導体回路設計では、アナログ回路や高周波回路の最適化、プロセス変動の解析、設計空間の探索を目的として、機械学習を直接取り入れる研究が急速に増えている。特に、SPICE を置き換える高速推定モデル、トランジスタ寸法やバイアス条件を自動調整する強化学習、回路トポロジーをそのまま扱う GNN などが代表的な手法になっている。

2021 年の Analog/RF Circuit Optimization with Surrogate Models(https://arxiv.org/abs/2109.13419)は、VCO や PLL、LNA といった高速アナログ/RF 回路の性能推定をニューラルネットで高速化する研究である。従来は多数の SPICE 実行が必要だったが、学習したサロゲートモデルが代替することで探索速度が大幅に向上し、複雑な RF 回路設計で特に効果が大きい。

2022 年の Reinforcement Learning–Based Analog Circuit Sizing(https://arxiv.org/abs/2208.10575)は、OTA やアンプの W/L、バイアス、電流量などを強化学習により自動最適化する手法を示している。ゲインや帯域など複数の仕様を同時に満たす設計点を探索でき、温度やプロセス変動も学習に組み込める。

同じく 2022 年の GNN-based Analog Circuit Performance Prediction(https://arxiv.org/abs/2209.05736)は、ネットリストをグラフとして扱い、GNN によりゲイン、帯域幅、位相余裕、消費電力を予測するモデルである。SPICE の必要回数を大幅に減らし、寄生を含む回路でも精度が高い点が評価されている。

プロセス変動の扱いでは、2020 年の Process Variation & Yield Prediction using ML(https://arxiv.org/abs/2006.03894)が、Vth、移動度、酸化膜容量などのばらつきを ML でモデル化し、Monte Carlo の高速な代替として用いる手法を示している。FinFET を含む最新プロセスにも適用しやすい。

多目的最適化を扱う研究として、Multi-objective Analog Circuit Design via Bayesian Optimization(2021, https://arxiv.org/abs/2105.10585)がある。ゲイン、帯域幅、面積、消費電力といった相反する要求を評価し、SAR ADC や OTA の設計探索に利用できる。

また、2023 年の Data-driven Modeling of Analog ICs using Deep Neural Networks(https://arxiv.org/abs/2303.02855)は、アナログ IC ブロックの動作を深層学習で近似し、小信号モデルや経験式に依存しない推定モデルを構築する試みである。

おわりに

生成AIを活用した半導体設計について、初心者の立場から整理してみた。本来は Synopsys や Cadence の半導体設計ソフトにおけるレイアウト設計や寄生容量を含む自動化のAI活用事例を書きたかったが、情報不足や企業秘密の制約により実現できなかったため、誰でも利用できる ChatGPT や Gemini といった生成AIを用いることで回路設計の作業を効率化できると考え、この内容をまとめることにした。多くの方にも生成AIを活用してほしいと思う。