これは何か

PYNQ-Z1 を使って遊んでみます。

今回は、下記ができるようになる事を目指します。

- Verilog HDL のコードを書いてみる

- Verilog HDL でモジュールを作って IP に接続する

関連記事:

する事

- CLK を数えるカウンタを verilog HDL で書く

- カウンタを使って分周して、LED を点滅させる

役に立ちそうなリンク

...

2-1. プロジェクトの作成

-

PYNQ や Vivado のセットアップがまだな場合

- 手順 1-2. 開発の準備 を参考に済ませておきます

-

手順 1-3. プロジェクトの作成 を参考に、新規プロジェクトを作成します

- Project name : asobu02

- Project location : ~/vivado/asobu

- にしました。

-

手順 1-4-1. ZYNQ の IP を配置する を参考に、Block Design を作ります

- 名前は design_1 のままにしました

2-2. Verilog HDL でモジュールを作る

2-2-1. Verilog HDL のファイルを追加します。

Sources の Design Sources を右クリックし、Add Sources をクリック

design sources が選択されている事を確認して Next

Create file をクリックし、File name を指定。led_blink にしました。

Finish をクリックして完了

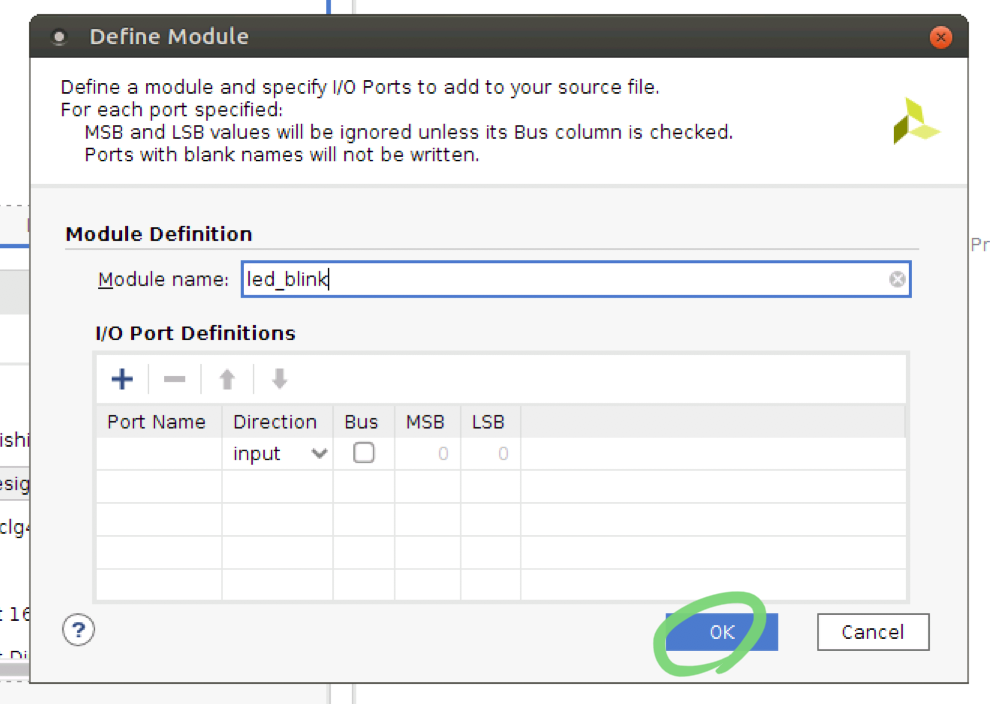

I/O Port は後で設定するので、とりあえず OK します。警告が出ますが yes

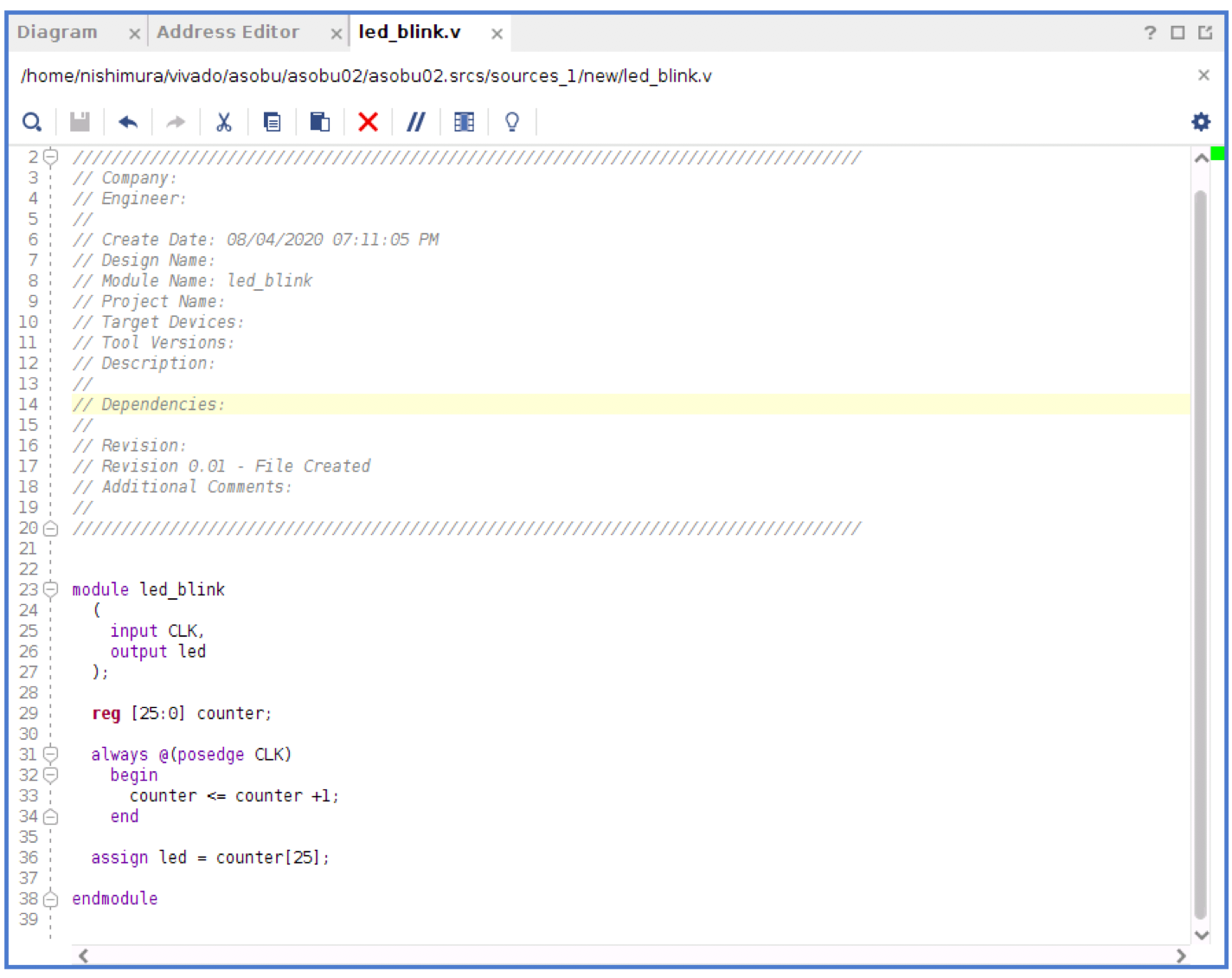

2-2-2. Verilog HDL のファイルを編集します

- 新しくできた led_blink をダブルクリック

- 右に、エディタが開きます

- 100 MHz でクロックが来ます

- そのクロックを 26 bit カウントします

- LED への出力を、カウンタの 26 bit 目と同期させて点滅させてみましょう

- 0.335 秒くらいで ON/OFF が切り替わるはずです

module led_blink

(

input CLK, // 入力 CLK を定義します

output led // 出力 led を定義します

); // 最後の行には , がいらないので注意

reg [25:0] counter; // 26 bit のカウンタを定義します

always @(posedge CLK) // CLK が立ち上がるたびに、この中が実行されます

begin

counter <= counter +1;

end // counter を 1 追加するだけです。 +=, ++ は使えません

// 桁が溢れると、0 に戻ります

assign led = counter[25]; // counter の 26 bit 目を led に接続します

endmodule

エディタの編集が終わったら、Ctrl+S を押すか save ボタンを押して保存しておきます。

2-3. IP Integrator で IP を配置する

大まかな手順は下記です:

- led_blink.v を配置する

- ZYNQ (CPU) の IP を配置する

- 配線する

2-3-1. 自作モジュールを配置する

- Diagram をクリックしておきます

- led_blink.v を右クリックし、Add Module to Block Design をクリック

led_blink.v モジュールが設置されます

2-3-2. ZYNQ を配置する

手順 1-4-1. ZYNQ の IP を配置する を参考に、ZYNQ の IP を設置します。

2-3-3. 配線する

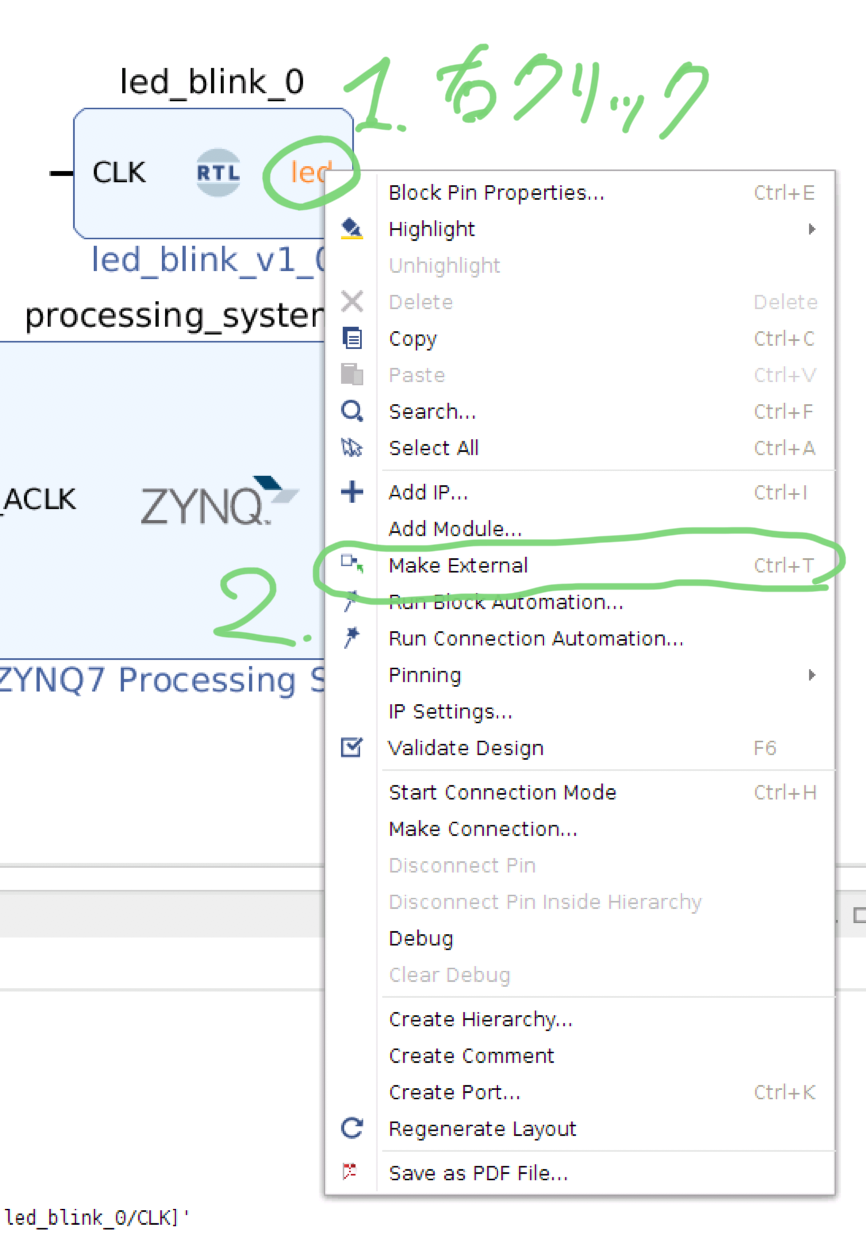

led_blink_0 の led 端子を右クリックし、Make External をクリックします

生成された led_0 ポートをクリックし、External Port Properties ボックス内の Name: を LED に変更します

- Run Connection Automation と Run Block Automation をクリックして実行します

- ZYNQ7 Processing System の FCLK_CLK0 と M_AXI_GP0_ACLK が自動で配線されなかったので、手動でつなげます

- デザインはこうなりました

2-4. 後仕上げ

2-4-1. HDL Wrapper を生成する

手順 1-5. HDL Wrapper を生成する と同様の手順です

2-4-2. 制約ファイルを設定する

手順 1-6. 制約ファイルを設定する と同様の手順です

2-4-3. 生成する

手順 1-7. 生成する と同様の手順です

こんな実装になりました。AXI を使ってないので、とてもシンプルですね。

2-5. PYNQ で実行する

2-5-1. ファイルのアップロード

- 手順 1-8-1. ファイルのアップロード を参考に PYNQ へアップロードします

- 例えばこんなコマンドになります

scp ~/vivado/asobu/asobu02/asobu02.runs/impl_1/design_1_wrapper.bit xilinx@192.168.2.99:pynq/overlays/asobu02/asobu02.bit

scp ~/vivado/asobu/asobu02/asobu02.srcs/sources_1/bd/design_1/hw_handoff/design_1.hwh xilinx@192.168.2.99:pynq/overlays/asobu02/asobu02.hwh

2-5-2. jupyter で実行

- 手順 1-8-2. jupyter で実行 を参考に実行します

import pynq

fpga = pynq.Overlay('asobu02.bit')

# コンフィグレーション完了後、LED が点滅し始めるはずです