はじめに

UltraZed-EG スターターキットに Debian GNU/Linux (v2017.3版) を構築する方法について、具体的な方法をいくつかに分けて説明します。

この記事では、ZynqMP の Boot Loader で使うための Sample FPGA Design の構築について説明をします。

Sample FPGA Design を構築する目的

Vivado SDK では FSBL(First Stage Boot Loader) および PMUFW(Platform Manager Unit Firmware) をビルドするのにハードウェア情報が必要になります。ただしハードウェア情報のうち ZynqMP の PS(Processing System)の設定のみが必要なだけで、実は PL(Programmable Logic) の情報は必要ありません。ということは、PL 側のデザインは何でも良くて、ちゃんと PS 側の設定がされているハードウェア情報でありさえすれば良いのです。

U-Boot のビルドでもハードウェア情報に含まれるファイルが必要です。ただし、U-Boot でハードウェア情報に含まれるファイルが必要になるのは u-boot.spl をビルドする場合です。今回は u-boot.spl は使いませんので、一度作っておいたファイルを使いまわしても問題ありません。

Sample FPGA Design の構成

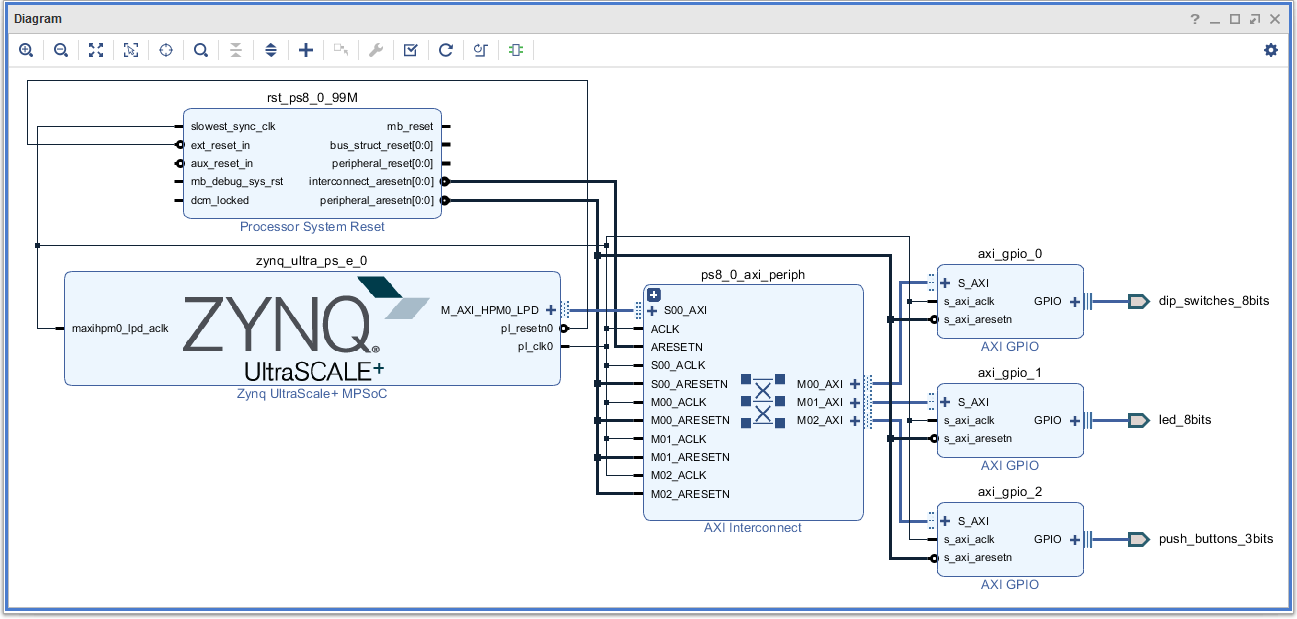

PS 側の情報が出来れば事足りるので、ここでは以下のような単純な FPGA デザインを作ります。

Fig.1 ZynqMP Sample Design

必要な環境

- Vivado 2017.2

- Vivado SDK 2017.2

Sample FPGA Design の構築

次の URL から git clone でリポジトリをダウンロードして v2017.3.0 をチェックアウトします。

shell$ git clone git://github.com/ikwzm/ZynqMP-FPGA-Linux

shell$ cd ZynqMP-FPGA-Linux

shell$ git checkout v2017.3.0

ここでは Vivado の XST(Xilinx Software Command Line Tool) を使って構築する方法を示します。GUI を使って手で入力するのは面倒なので Tcl スクリプトファイルを用意しています。

- target/UltraZed-EG-IOCC/build/

- fpga/

- create_project.tcl

- design_1_bd.tcl

- implementation.tcl

- export_hardware.tcl

- fpga/

Project を作る

create_projet.tcl を Vivado で実行してプロジェクトを作ります。

vivado% cd target/UltraZed-EG-IOCC/build/fpga/

vivado% vivado -mode batch -source create_project.tcl

なお、この FPGA デザインは次の記事で説明している SD1 の WP(Write Protection) の設定も済ませてあります。

ビットストリームの生成

implementation.tcl を Vivado で実行して、デザインの論理合成、配置配線、ビットストリームの生成を行います。

vivado% cd target/UltraZed-EG-IOCC/build/fpga/

vivado% vivado -mode batch -source implementation.tcl

ハードウェア情報の生成

export_hardware.tcl を Vivado で実行してハードウェア情報を生成します。

vivado% cd target/UltraZed-EG-IOCC/build/fpga/

vivado% vivado -mode batch -source export_hardware.tcl

このスクリプトを実行することにより、target/UltraZed-EG-IOCC/build/fpga/project.sdk/design_1_wrapper.hdf が生成されます。