Windows 10 Pro (v1909)

PYNQ-Z1 (Digilent) (以下、PYNQと表記)

PYNQ v2.5 Image

Vivado v2019.1 (64-bit)

Akafugu FTDIアダプター

NonSoft様 RS232Cテストツール

概要

- Verilog-HDLにてrx受信したものをtx送信する実装

- Akafugu FTDIアダプタでPCと接続

- RS232Cテストツールにてエコーバックを確認した

Block Design

UARTのrxに対して、Make Externalしたrx_0を接続。

同時に、自作のUartLoopBack_v1_0のrxに接続した。

Address Editor

UartLiteのアドレスはデフォルトのまま。

UartLoopBack_v1_0 (Verilog-HDL)

UartLoopBack_v1_0はrxしたものをtxするだけの実装。

`timescale 1ns / 1ps

module UartLoopBack(

input rx,

output tx,

input clk

);

reg buffer; // rxをtxに渡すためのバッファ

always @(posedge clk)

begin

buffer <= rx;

end

assign tx = buffer;

endmodule

制約ファイル

set_property PACKAGE_PIN Y18 [get_ports rx_0]

set_property IOSTANDARD LVCMOS33 [get_ports rx_0]

set_property IOSTANDARD LVCMOS33 [get_ports tx_1]

set_property PACKAGE_PIN Y19 [get_ports tx_1]

set_property IOSTANDARD LVCMOS33 [get_ports reset_rtl]

set_property PACKAGE_PIN W6 [get_ports reset_rtl]

reset_rtlの設定はしっかりとは考えてない。

FTDIアダプタ (3.3V使用)

今回は3.3Vとして使用。

上記の制約ファイルでもLVCMOS33を設定している。

COM3としてパソコンでは認識した。

接続

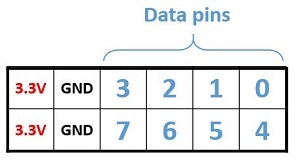

PMOD

https://pynq.readthedocs.io/en/v2.4/pynq_libraries/pmod.html

- PYNQ <-> FTDIアダプター

- PMODA 0ピン(RX) <-> FTDI (TX)

- PMODA 1ピン(TX) <-> FTDI (RX)

- PMODA (GND) <-> FTDI (GND)

ブレッドボード用のケーブル3本で接続した。

Vivado生成ファイル

下記のファイルをPYNQの「\\pynq\xilinx\jupyter_notebooks\base」に配置する。

(Explorerでコピーした)。

- UARTloopback_200814.bit

- UARTloopback_200814.tcl

Pythonスクリプト

from pynq import Overlay

ol = Overlay("/home/xilinx/jupyter_notebooks/base/UARTloopback_200814.bit")

動作確認

NonSoft様の以下を使用させていただきました。

ソフト提供ありがとうございます。

下記が実行した結果。

loopbackのVerilog HDL実装が有効となり、送信した文字列がそのまま受信できている。

9600 bpsでない動作

19200bpsでも試してみた。

文字化けはない。

![]()

そもそもUartLiteの初期化もしてない。

このあたりは将来もう少し理解を深めて使うことになるかな。

rxで受けたものをtxへループバックしながら、rxのコマンドをPSで解析、みたいなこと。それをするための今回のBlock Design (未検証)。

はまった点

UartLiteのtxを別のIPに接続しようとしたが、Make Externalするとそれはできないようだ。

シリアル通信モニターのようなことをするには工夫が必要になるだろう。

XSDK > Loopback機能

下記は広告などがある。見たくない人は開かないこと

XUartPs_SetOperMode(Uart_Ps, XUARTPS_OPER_MODE_LOCAL_LOOP); //Local loopback mode

XUARTPS_OPER_MODE_LOCAL_LOOPで指定する(ローカル)ループバック機能があるとのこと。

PYNQのシステムでXSDKを使わない場合、この機能を使うLibraryが見つからなかった。

その他、参考情報

この作業をする過程で見つけたいくつかのWebページ。

- verilog~UART通信受信機(RX)編~

-

verilog~UART通信送信機(TX)編~

- これらを使おうとしたけれど、AXIとの接続でうまい方法を見つけられなかった

-

PYNQ で遊ぶ : 2. Verilog HDL を使ってみる

- Verilog-HDLの実装をBlock Designに追加する「Add Module to Block Design」はよい情報でした

- その他の部分もわかりやすかったです

- 情報感謝です

-

デザイン向け(論理合成可能)SystemVerilog記述

- VivadoではSystem VerilogがBlock Design用には使いにくいのですが、今後それを工夫してSystem Verilogを使うかもしれない

- 上記のページはうまくまとめられています

- 情報感謝です

-

Vivado IP Integratorでよく使う便利なIPコア16選

- concat含めて、いろいろ便利そうなIPの紹介

- 情報感謝です

-

AXI UART 16550 standalone driver

- UART Liteとは別のIP

- Test casesにXSDKの実装例がある

- Vivado 合成 - サポートされない SystemVerilog 構文

-

uart cycle project based on Xilinx zynq-7020 Z-turn board

- 二つのUART LiteのIPのtx,rxを相互接続

- これで何をするかまでは追えていない