はじめに

Vivado IP Integrator では非常に多くのIPコアが無料で使えます。

その中でも私が頻繁に使う、簡単に扱えて便利なものだけをまとめて紹介したいと思います。

ワイヤ接続系

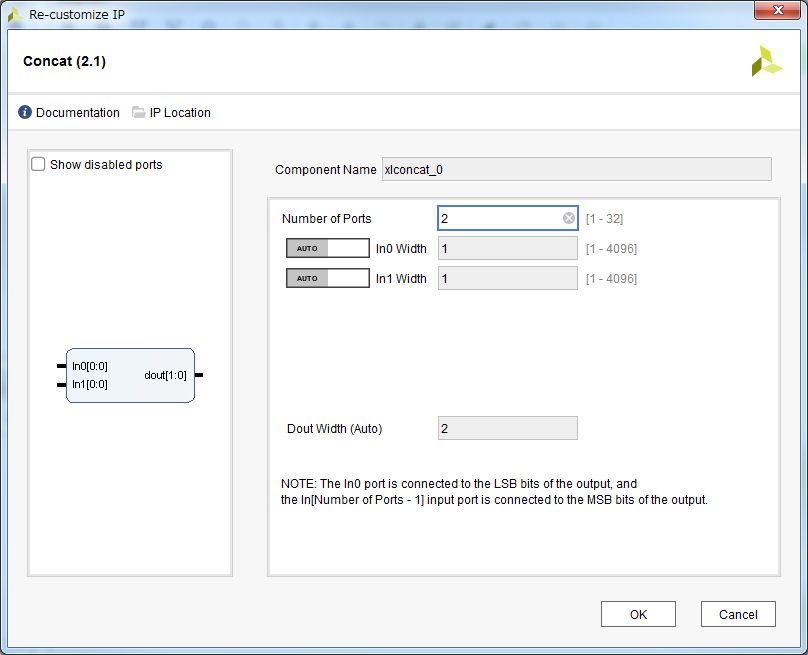

Concat

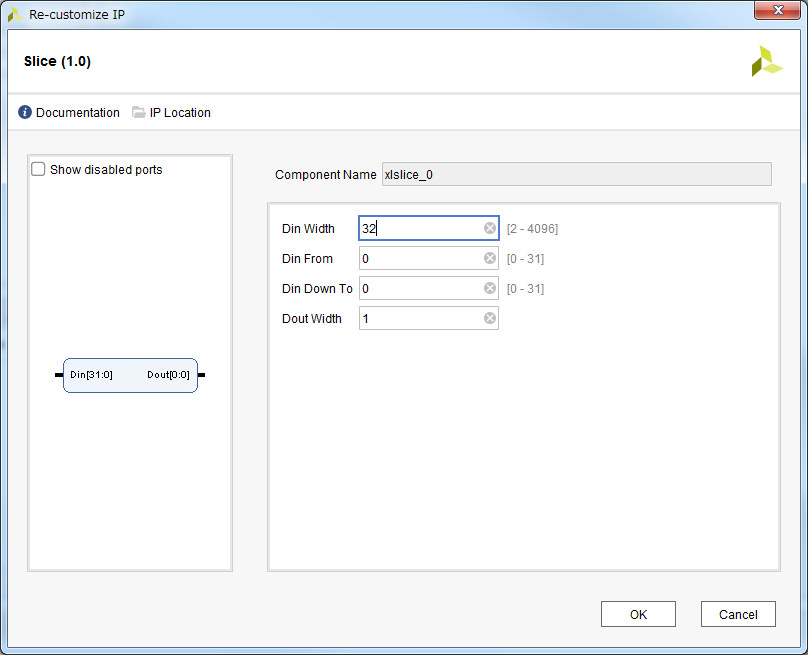

Slice

1本のバスのうち、指定した範囲だけを取り出すことができます。

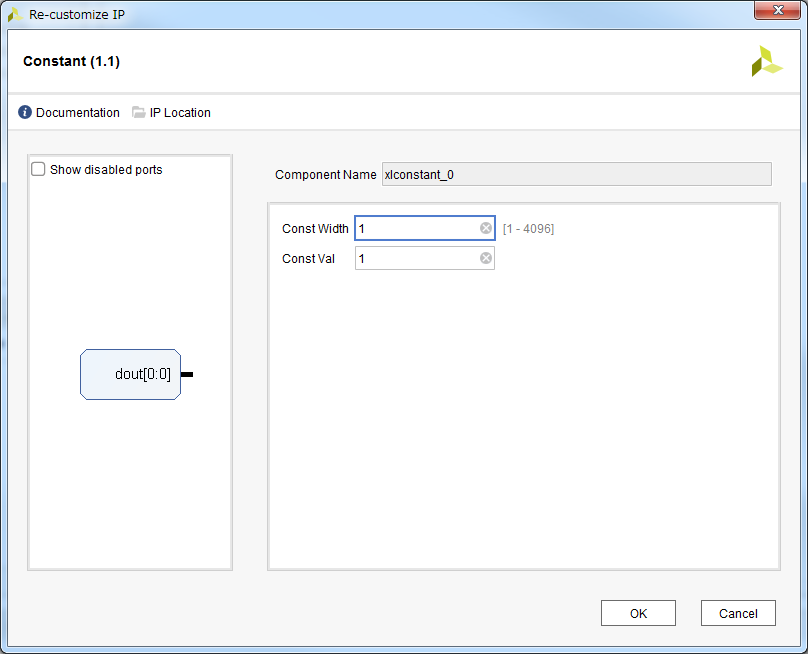

Constant

論理演算系

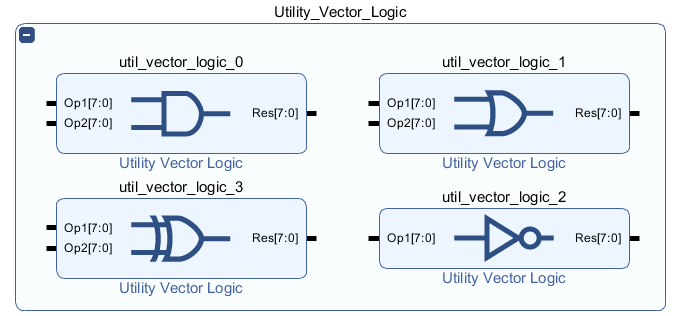

Utility Vector Logic

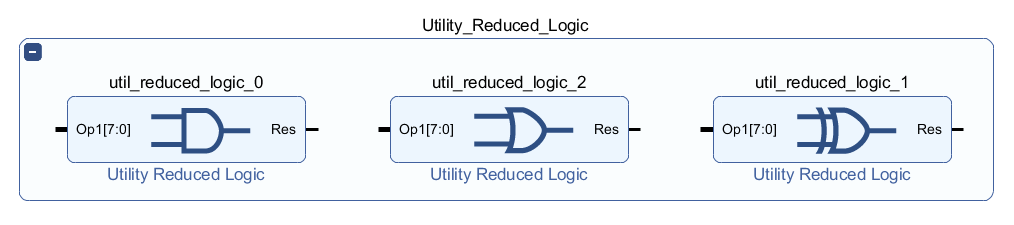

Utility Reduced Logic

算術演算系

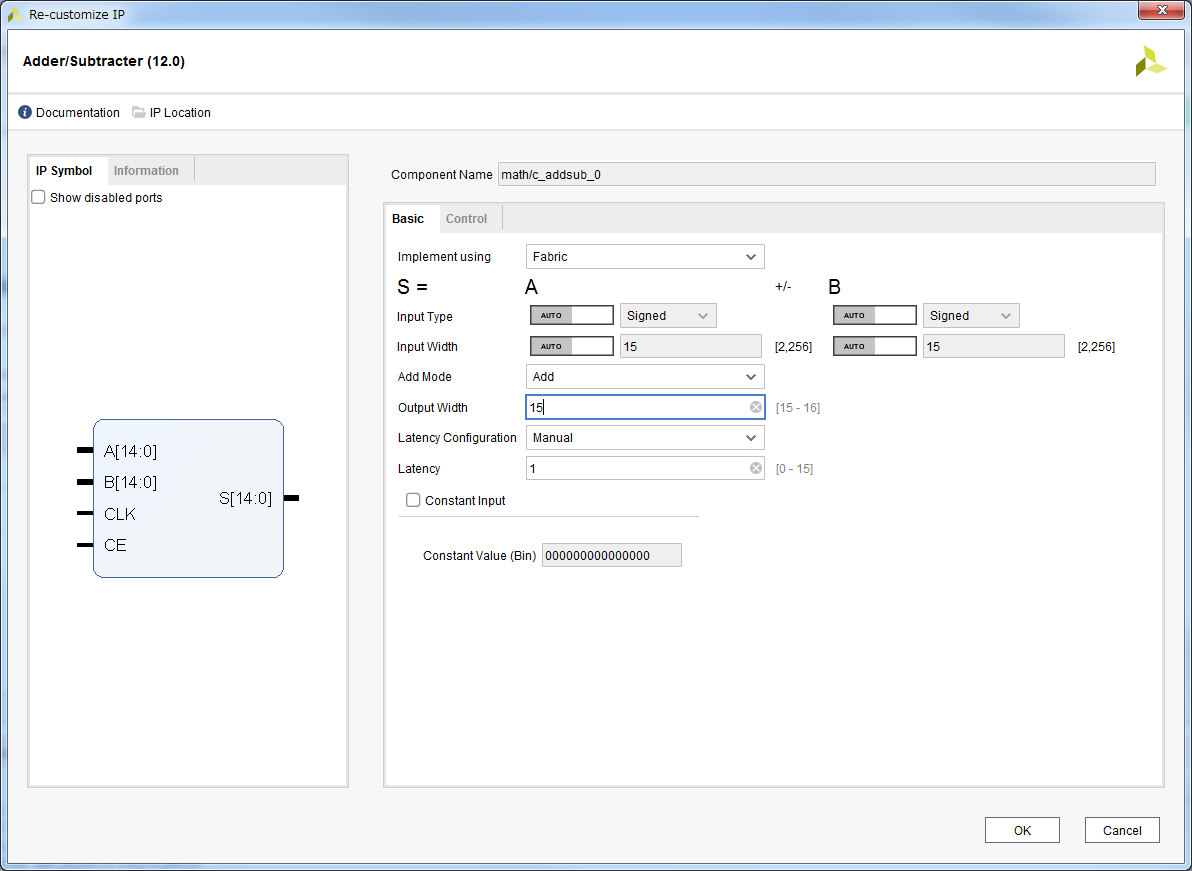

Adder/Subtracter

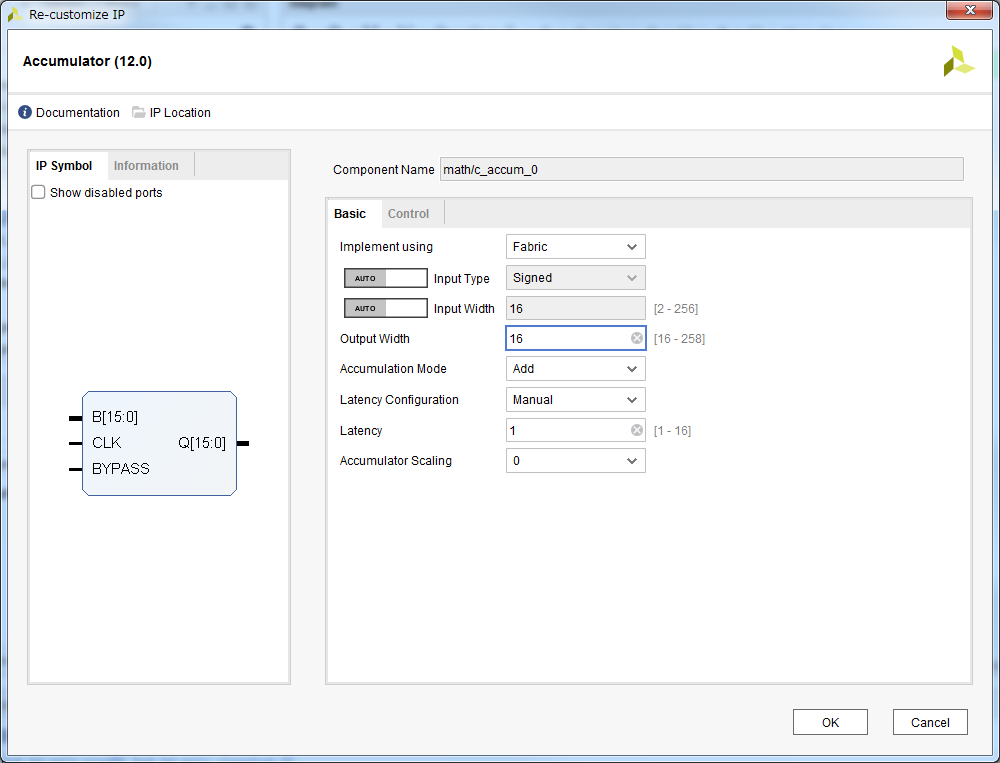

Accumulator

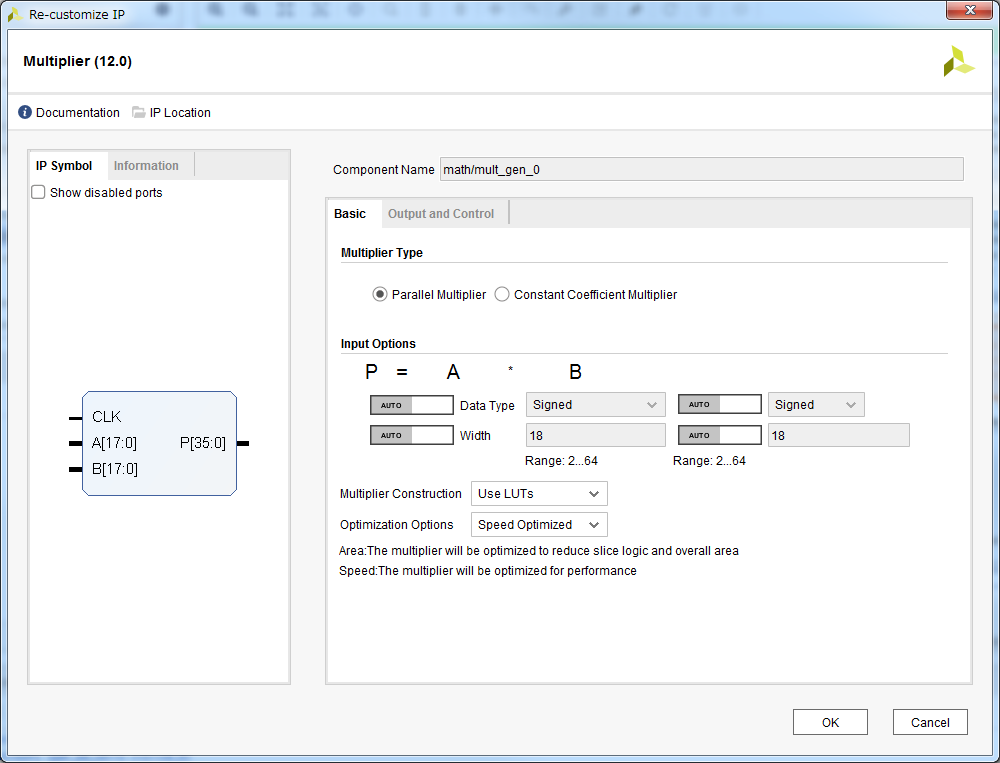

Multiplier

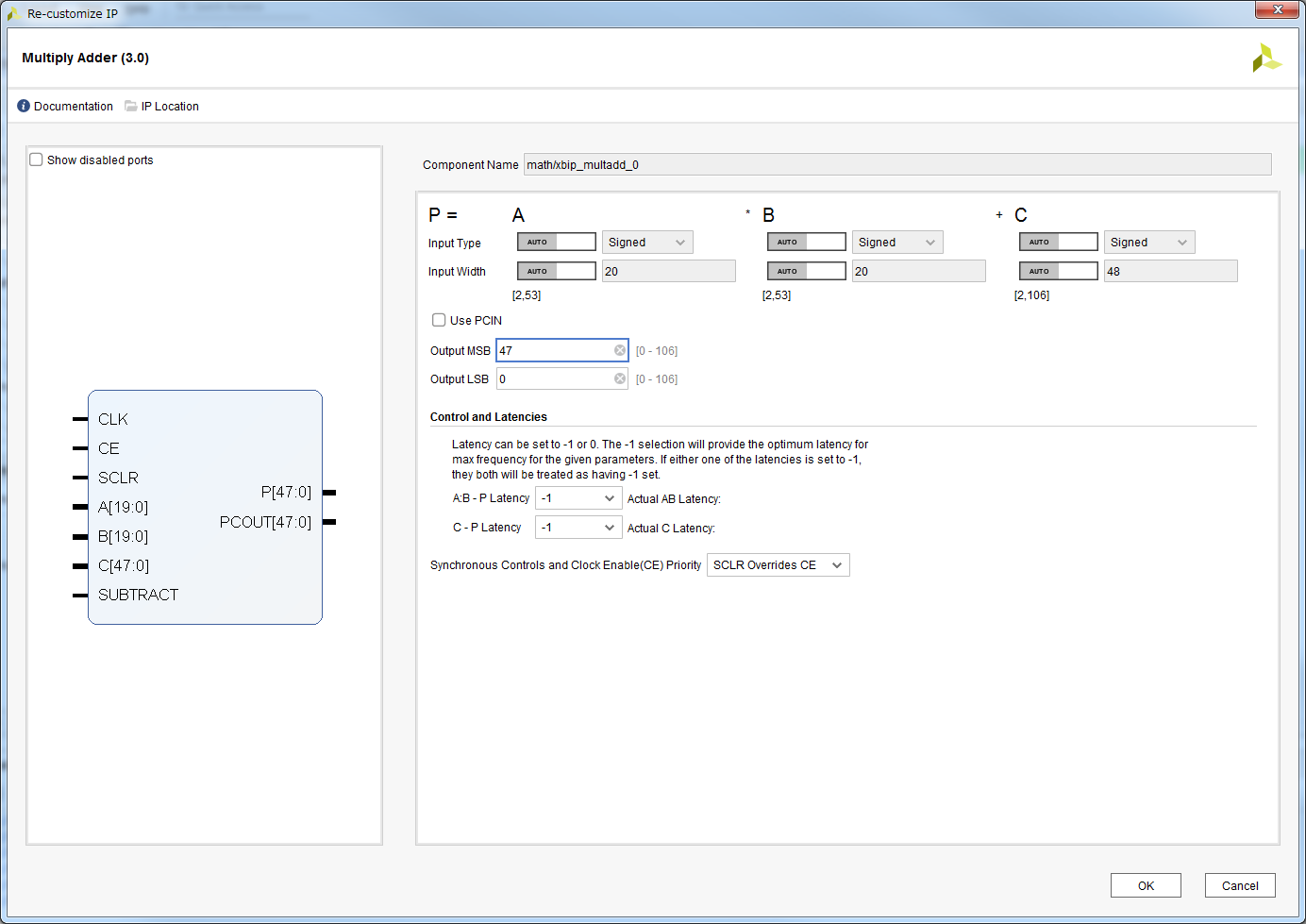

Multiply Adder

クロック系

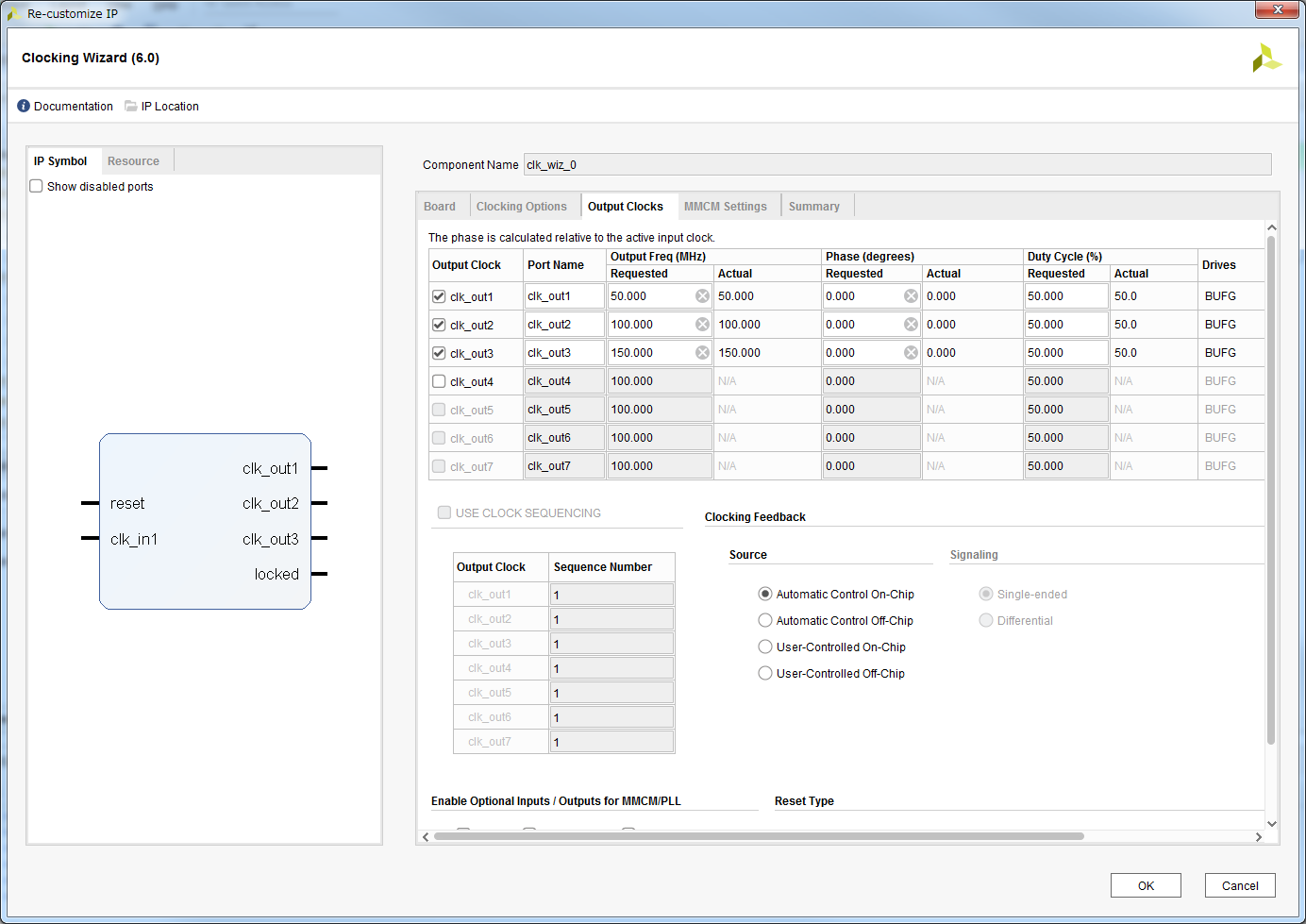

Clocking Wizard

1つのクロック入力から、複数種類のクロックを生成することができます。

例えば、100MHzのクロックを入力して、50MHzのクロック、100MHzで位相が90°ずれたクロック、150MHzのクロックなど

任意に周波数と位相を指定して生成することが可能です。

バッファ系

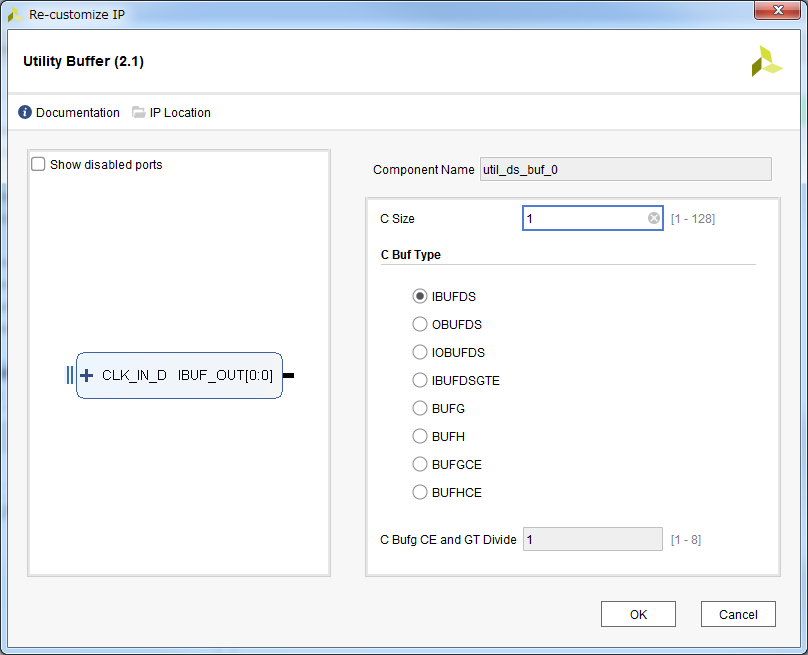

Utility Buffer

差動入出力バッファやクロック用バッファなどを指定して使うことができます。

差動のクロックを外部から入力したりするときに便利です。

参考: https://japan.xilinx.com/support/documentation/user_guides/j_ug471_7Series_SelectIO.pdf

デバッグコア系

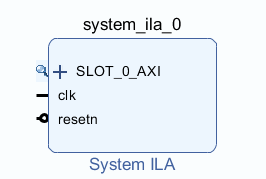

System ILA / ILA

FPGA内部に組み込むロジックアナライザのようなブロックです。

FPGA内部の信号が実機動作中にどのような状態になっているのか、Vivadoの画面から見ることができるようになります。

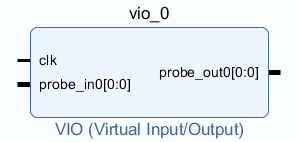

Virtual Input/Output

Vivadoの画面から指定した信号をFPGA内部に出力したり、内部の信号を見たりすることができます。

リセットボタンの代わりに使ったり、IPコアのパラメータを動的に変更したりするのに便利です。

シミュレーション系

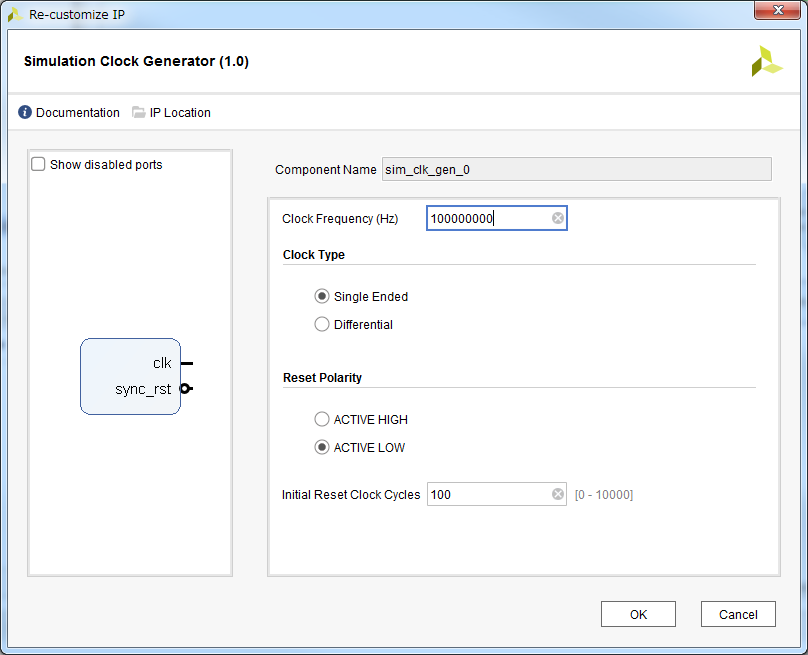

Simulation Clock Generator

ブロックデザインをシミュレーションするときに、クロック源リセット源として動作します。

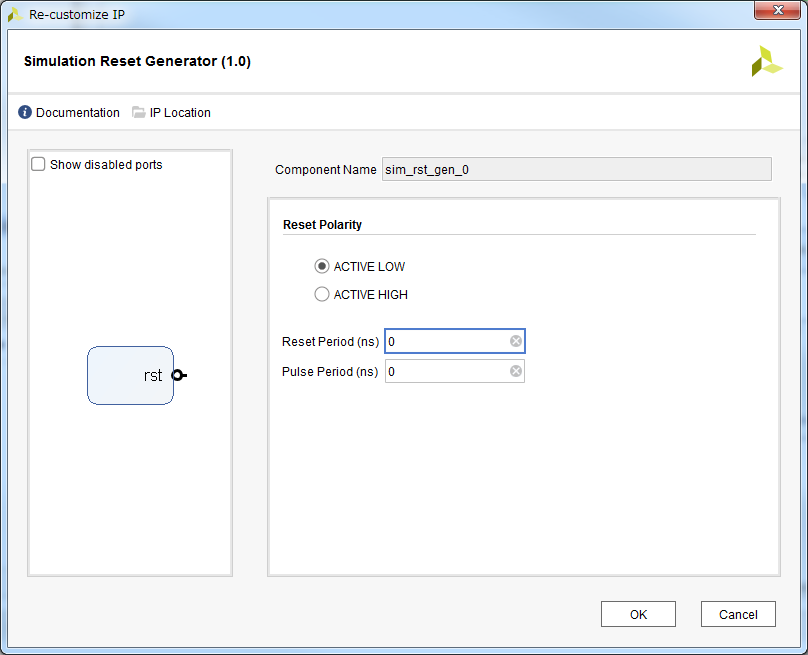

Simulation Reset Generator

ブロックデザインをシミュレーションするときにリセット源として動作します。

その他

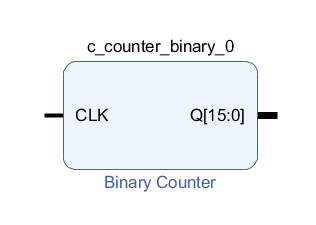

Binary Counter

クロックをカウントしてQに出力します。

クロック出力が動いているのをLEDに出力して確認したり、のこぎり波を作ったり、タイマーに使ったり、いろいろ便利です。

参考