1. はじめに

RoboCup Jr.のために設計したカスタム電源基板の第2版は、DCDCコンバータの自壊と、保護回路の制御不能なチャタリングという二つの致命的な問題に見舞われました。設計経験5ヶ月という浅さにもかかわらず、失敗の原因は単一ではなく、情報の誤認、部品選定、アートワークという三つの側面が複雑に絡み合った結果でした。

初心者(設計5ヶ月目)なのでひどいミスを連発しています。

下書き段階ですがとりあえず公開しているので、考察にミスがある可能性が高いです

2. 致命的な問題 I:DCDCコンバータの自壊(高周波設計の罠)

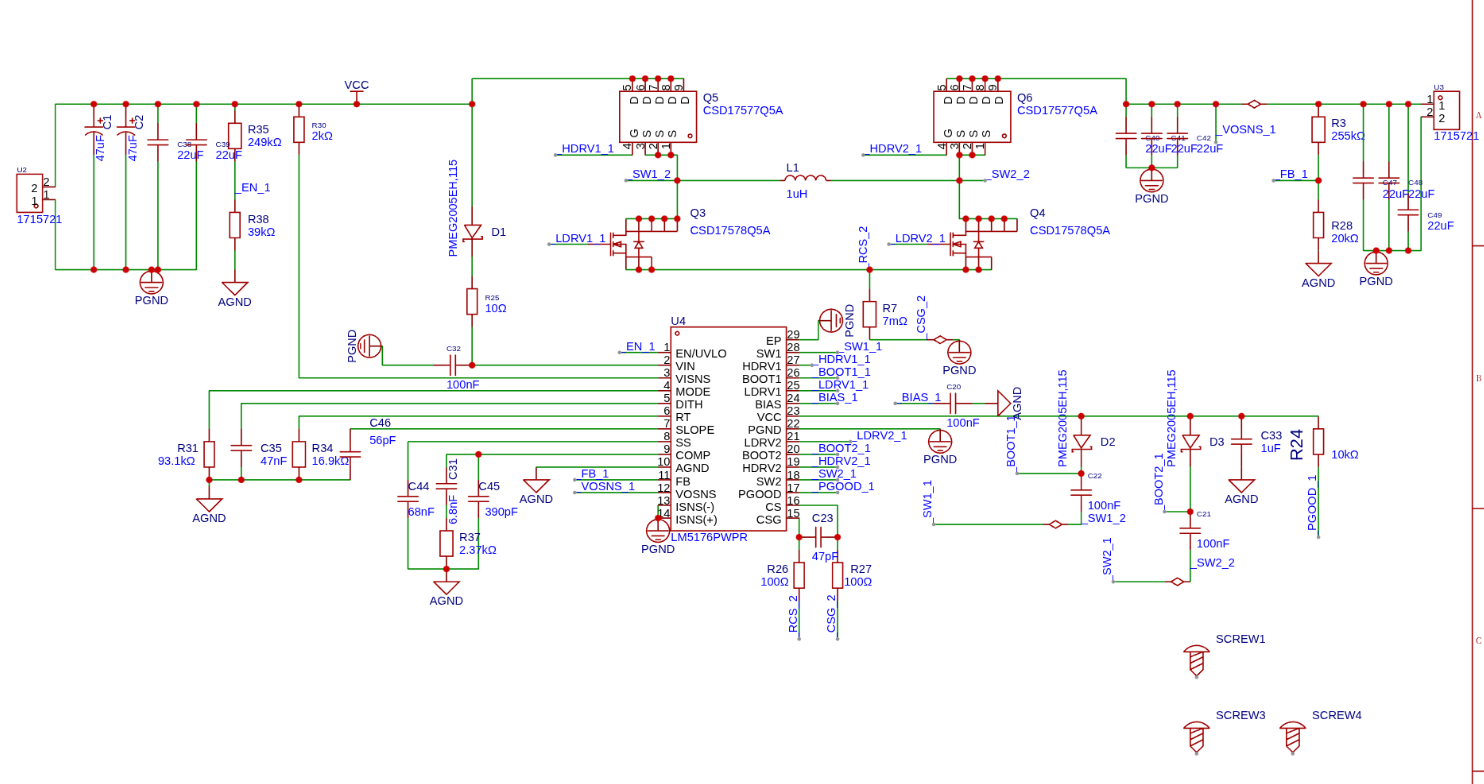

DCDC昇降圧コンバータ(LM5176使用)は、最終的にMOSFETが破壊され自壊しました。観測された「目標電圧に向けて徐々に下がった後に跳ね上がる」という挙動は、破壊に至る前に制御ループが発振していたことを示唆しています。

2.1 破壊の複合メカニズム

自壊は、アートワークによるノイズ源の発生と、それによる制御信号の不安定化という連鎖にあります。

-

ホットループの高インダクタンス化(ノイズ源の形成):

- Layer 2に完全なGNDプレーンを用意したにもかかわらず、その直上にあるDCDCホットループのビア接続が非効率でした。

- さらに、XTコネクタの足以外への無駄な放熱ビアを追加したことが、電流パスを複雑にし、寄生インダクタンス(L)を致命的に増大させました。この高Lが制御ループに大きな位相遅れをもたらし、不安定化の主因となりました。

-

貫通電流による熱破壊(推定):

高Lによって発生した深刻なノイズが、Layer 3のハイサイドMOSFET駆動信号線に結合し、駆動タイミングが狂いました。ノイズによるタイミングのずれで貫通電流(シュートスルー)が発生し、MOSFETが熱破壊に至ったと推定されます。

3. 致命的な問題 II:保護回路のチャタリング(情報と能力の破綻)

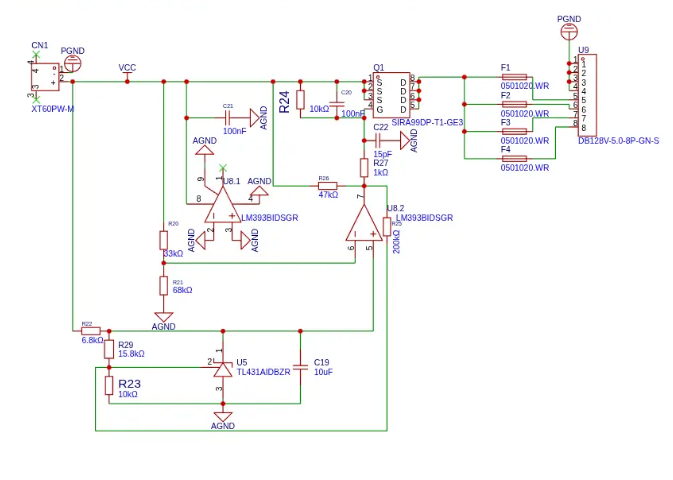

過放電保護回路のMOSFETが、**「12V → 6V」**という高速チャタリングを繰り返し、制御不能になりました。

(私の機体では実使用上は問題にならなかったが重大な欠陥)

3.1 駆動能力の破綻:誤認の悲劇

これがチャタリングの決定的な原因です。

-

$Q_g$の誤認(情報の信頼性):

JLCPCBライブラリの誤表記により、MOSFETのGS-10Vでの全ゲート電荷量($Q_g$)を$84\text{nC}$と誤認(実際は$172.5\text{nC}$以上)しました。この誤認が、後の駆動能力設計の過信につながりました。 -

プルアップ抵抗($R_{PU}$)の過大:

汎用コンパレータLM393のオープンコレクタ出力に、**$47\text{k}\Omega$**という極端に大きなプルアップ抵抗を使用してしまいました。 (いつものセンサプルアップのときのクセでつい47Kを使ってしまった) -

時定数の破綻: この組み合わせにより、ゲート電圧の充電時定数 $\tau$ が$500\mu\text{s}$オーダーにまで増大し、MOSFETは長時間、不安定な閾値付近を漂うことになりました。

3.2 ノイズの自己増幅ループ

- ノイズの結合: 上記が原因となったノイズが、AGNDとの一点スター接続のビアを介してTL431の基準電位を揺らしました。

- ノイズの増幅: ノイズに対する脆弱性が極限まで高まったMOSFETに対し、不安定な基準電圧が正帰還によって増幅され、LM393は高速なON/OFFを強制し続けました。

4. 総括:次の設計への教訓

今回の失敗は、情報の誤認・過信、駆動能力の破綻、レイアウトによるノイズの発生という、電子回路設計における重要なミスが複合的に絡み合った結果です。

最終的な教訓(Rev. 3設計原則)

- 情報源の徹底確認: サプライヤーの簡易ライブラリに頼らず、必ずメーカーオリジナルのデータシートを参照し、$Q_g$などの重要パラメータは**最大値(Max.)**で設計を行うこと。

- 専用ゲートドライバの導入: $Q_g$が$100\text{nC}$を超えるパワーMOSFETを駆動する際は、汎用ICと高抵抗の組み合わせは絶対に避け、専用のゲートドライバICを選定し、高速駆動能力を確保すること。

- 最短リターンパスの実現: メリットが少ないビアの使用を極力避け、Layer 1から直下のLayer 2への最短リターンを実現し、低インダクタンス化を徹底すること。

高校3年生でのリベンジに向け、この教訓を胸に、設計の精度を高めていきます。