背景

Cyclone® 10 GX FPGA 開発キットで動作するビデオ&画像処理スイート(VIP Suite)のリファレンスデザインが公開されているが、対応しているインテル® Quartus® Prime開発ソフトウェアのバージョンが18.0と非常に古く、かつそのままデザインを最新バージョンにアップデートしてもエラーが発生して動作しません。

この記事では古いデザインを最新のインテル® Quartus Prime開発ソフトウェアに移植して、動作させることを目的としています。

動作環境

ソフトウェア

今回使用するソフトウェア Quartus Prime 開発ソフトウェア プロ・エディション Ver.21.3 Build170

使用するリファレンスデザイン

Cyclone 10 GX HDMI 4Kp60 with Video and Image Processing Pipeline Reference Design

Revision:2.0

コードの対応ソフトウェア Quartus Prime Software Ver.18.0

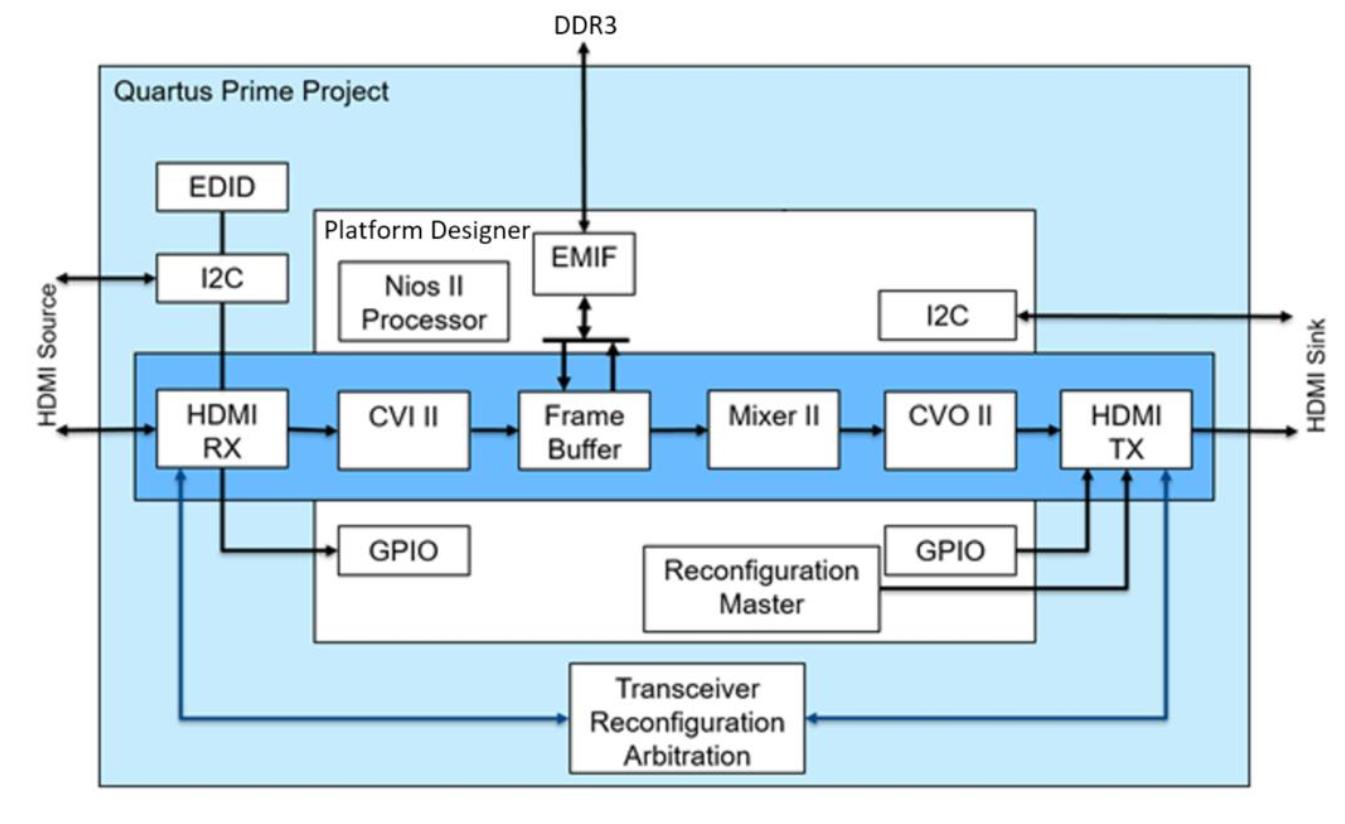

デザインは以下のような構成となっていて、HDMIで入力された画像をMIXしてHDMIで出力するというものです。

出力は3840x2160p60固定です。入力は3840x2160p60の場合そのまま出力され、たとえば入力が1080pの場合は背景のカラーバーとMixされて出力されます。詳細についてはユーザーガイドを参照ください。

移植の手順

HDMIだけでなく、DisplayPortやSDIのIPを使用しているデザインにおいても同様の手法が適用可能です。

- 新しいバージョンのインテル® Quartus® Prime ソフトウェアのIP CatalogでHDMIのリファレンスデザインを生成する

- オリジナルのデザインを新しいバージョンのインテル® Quartus Prime ソフトウェアで解凍およびIPのアップブレードをする

- 1.で生成したHDMI IPのファイルを2.のプロジェクトフォルダにコピーし、変更されたインターフェイス周りの呼び出しコードを修正する

- 各種設定ファイルを修正する

- フルコンパイル

HDMIのリファレンスデザインを生成する

旧バージョンのデザインでコンパイル時にエラーとなる一つの原因がIPのインターフェイスが変更されていることにあります。それでまずは新しいバージョンでリファレンスデザインを生成します。HDMIのIPはそれ単独ではなく、トランシーバーであるGXB、それを制御するリコンフィグマネージメントIP、PLLなどが絡んでいるため個々のIPのバージョンアップではなく、リファレンスデザインを使用する手法を今回は取ります。

詳細な手順はHDMI Intel Cyclone 10 GX FGPA IP Design Example User Guideの1.3章に記載があります。

1.インテル® Quartus® Prime ソフトウェア プロ・エディションVer.21.3を起動し、新しいプロジェクトを作成し、インテル® Cyclone® 10GXファミリーを選択します

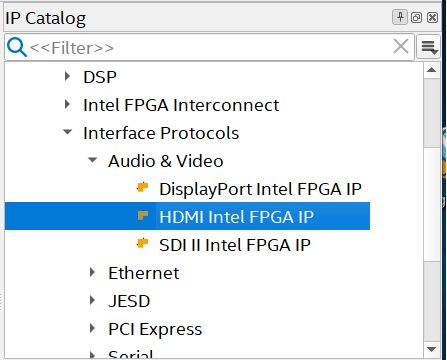

2.IP CatalogでHDMI Intel FPGA IPを選択し、ダブルクリックします

3.IPの名前を記載します。IPの名前はなんでもかまいません。

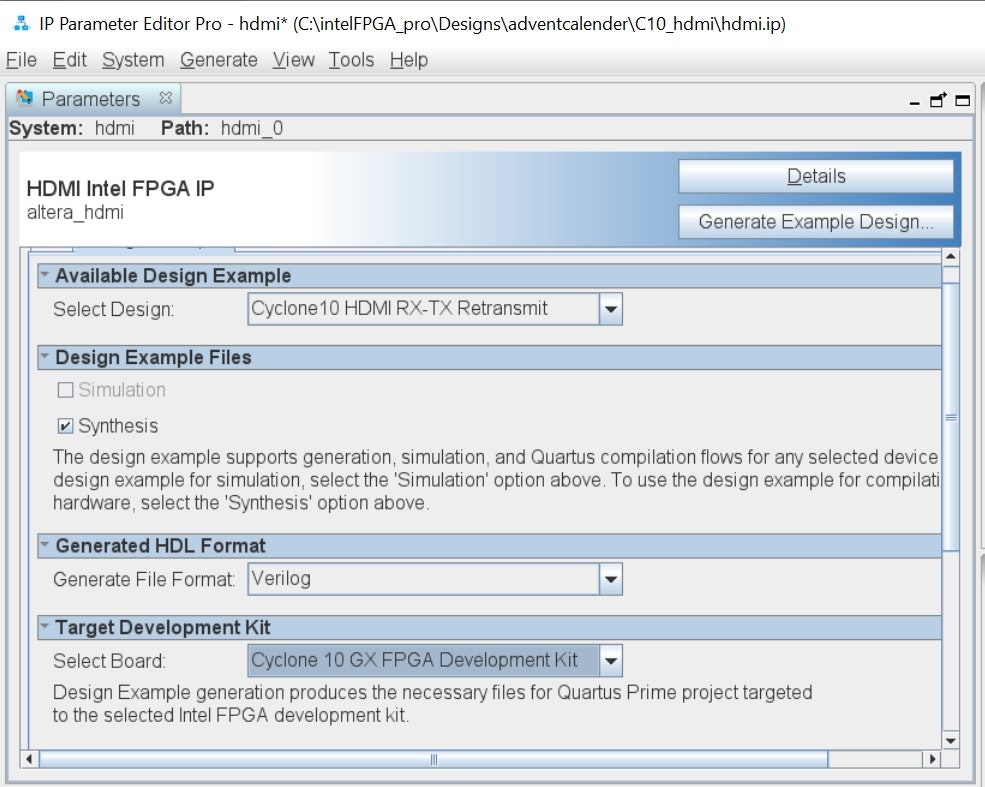

4.Createをクリックすると、IP Parameter Editorが開きます

5.IPのパラメータを設定します。Include I2C Master/Slaveのチェックを外しそれ以外はデフォルトの設定を使用します

6.Design Exampleタブを開き、Cyclone 10 HDMI RX-TX Retransmitを選択

7.Design Example FilesとしてSynthesisを選択

8.Gererated HDL FormatとしてVerilogを選択

9.Terget Development KitとしてCyclone 10 GX FPGA Development Kitを選択

10.Generate HDLをクリック

以上でプロジェクトフォルダ下にhdmi_0_aexample_designといったフォルダが作られ、リファレンスデザインのプロジェクトが生成されます。

リファレンスデザインの解凍とIPのアップグレード

1.LinkのDownloadからデザインをダウンロードします。c10gx_hdmi_vip.parというファイルが入手できます

2.Nios II Command Shellを起動して以下のコマンドを実行します。実行するとqarのあるフォルダに解凍されてるため、必要に応じてフォルダを作成した上で実行してください。

quartus_sh.exe --platform -name c10gx_hdmi_vip.qar

3. インテル® Quartus Prime ソフトウェアを起動して、2.で解凍したデザインのプロジェクトファイルtop.qpfを開きます

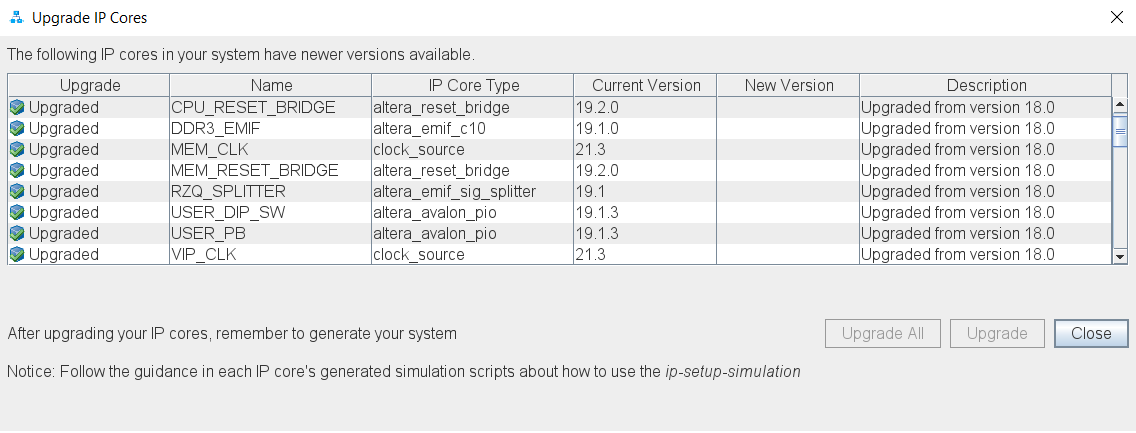

4. Launch IP Upgrade Toolアイコンをクリックします

5. 開いたUpgrade IP ComponentsウィンドウでAuto Upgradeアイコンをクリックします

6. IPの更新が終了したら一旦インテル® Quartus Prime ソフトウェアを閉じます

HDMI関連IPの更新

- 一番最初に生成したHDMIのリファレンスデザインのrtlフォルダからgxb, hdmi_rz, hdmi_tx, pll, reconfig_mgmtフォルダをVIPのリファレンスデザインのフォルダにコピーします。

- 続いて、トップのデザインhdmi_vip.vを修正します

u_hdmi_rx_top

(

/* I */ .mgmt_clk ( mgmt_clk ),

// /* I */ .mgmt_clk_reset ( mgmt_clk_reset_sync ), //コメントアウト

// /* I */ .hdmi_clk_in ( hdmi_clk_in ), //コメントアウト

(中略)

/* I */ .edid_ram_access(rx_edid_ram_access),

/* I */ .edid_ram_address (rx_edid_ram_address),

/* I */ .edid_ram_write (rx_edid_ram_write),

/* I */ .edid_ram_read (rx_edid_ram_read),

/* O */ .edid_ram_readdata (rx_edid_ram_readdata),

/* I */ .edid_ram_writedata (rx_edid_ram_writedata),

/* O */ .edid_ram_waitrequest (rx_edid_ram_waitrequest),

// 以下を追加

/* I */ .reset (reset),

/* I */ .reset_xcvr_powerup(reset),

/* I */ .fr_clk (refclk_fmc_p),

/* O */ .aux_error (),

/* O */ .vid_lock (),

/* I */ .user_pb_1 (1'b1)

);

(中略)

u_hdmi_tx_top

(

/* I */ .mgmt_clk ( mgmt_clk ),

// /* I */ .mgmt_clk_reset ( mgmt_clk_reset_sync ),// コメントアウト

(中略)

/* O */ .gxb_tx_cal_busy_out ( gxb_tx_cal_busy_out ),

/* I */ .gxb_reconfig_write ( gxb_tx_reconfig_write ),

/* I */ .gxb_reconfig_read ( gxb_tx_reconfig_read ),

/* I */ .gxb_reconfig_address ( gxb_tx_reconfig_address ),

/* I */ .gxb_reconfig_writedata ( gxb_tx_reconfig_writedata ),

/* O */ .gxb_reconfig_readdata ( gxb_tx_reconfig_readdata ),

/* O */ .gxb_reconfig_waitrequest ( gxb_tx_reconfig_waitrequest ),

/* I */ .gxb_tx_cal_busy_in ( gxb_tx_cal_busy_in ),

// 以下を追加

/* I */ .fr_clk (usb_refclk_p),

/* I */ .reset (reset)

);

設定ファイルの修正

top.qsfファイルをテキストエディタで開いて修正します。

- set_global_assignment -name QIP_FILE <ファイル名>.qip をコメントアウトします。ツールの仕様が変わったためか同じ名前の.ipファイルと.qipファイルがあるとエラーが発生したためです。

# set_global_assignment -name QIP_FILE output_buf_i2c/output_buf_i2c.qip

# set_global_assignment -name QIP_FILE pll/pll_hdmi_rx/pll_hdmi_rx.qip

# set_global_assignment -name QIP_FILE pll/pll_hdmi_tx/pll_hdmi_tx.qip

# set_global_assignment -name QIP_FILE qsys_vip_pipeline/qsys_vip_pipeline.qip

# set_global_assignment -name QIP_FILE pll/pll_hdmi_reconfig/pll_hdmi_reconfig.qip

# set_global_assignment -name QIP_FILE hdmi_tx/hdmi_tx/hdmi_tx.qip

# set_global_assignment -name QIP_FILE hdmi_rx/hdmi_rx/hdmi_rx.qip

# set_global_assignment -name QIP_FILE gxb/gxb_tx_reset/gxb_tx_reset.qip

# set_global_assignment -name QIP_FILE gxb/gxb_tx_fpll/gxb_tx_fpll.qip

# set_global_assignment -name QIP_FILE gxb/gxb_tx/gxb_tx.qip

# set_global_assignment -name QIP_FILE gxb/gxb_rx_reset/gxb_rx_reset.qip

# set_global_assignment -name QIP_FILE gxb/gxb_rx/gxb_rx.qip

# set_global_assignment -name QIP_FILE clock_control/clock_control.qip

2.以下の設定ををコメントアウトします

# set_global_assignment -name OUTPUT_IO_TIMING_NEAR_END_VMEAS "HALF VCCIO" -rise

# set_global_assignment -name OUTPUT_IO_TIMING_NEAR_END_VMEAS "HALF VCCIO" -fall

# set_global_assignment -name OUTPUT_IO_TIMING_FAR_END_VMEAS "HALF SIGNAL SWING" -rise

# set_global_assignment -name OUTPUT_IO_TIMING_FAR_END_VMEAS "HALF SIGNAL SWING" -fall

3."set_global_assignment -name IP_FILE pll/pll_hdmi.ip" をtop.qsfに追加します

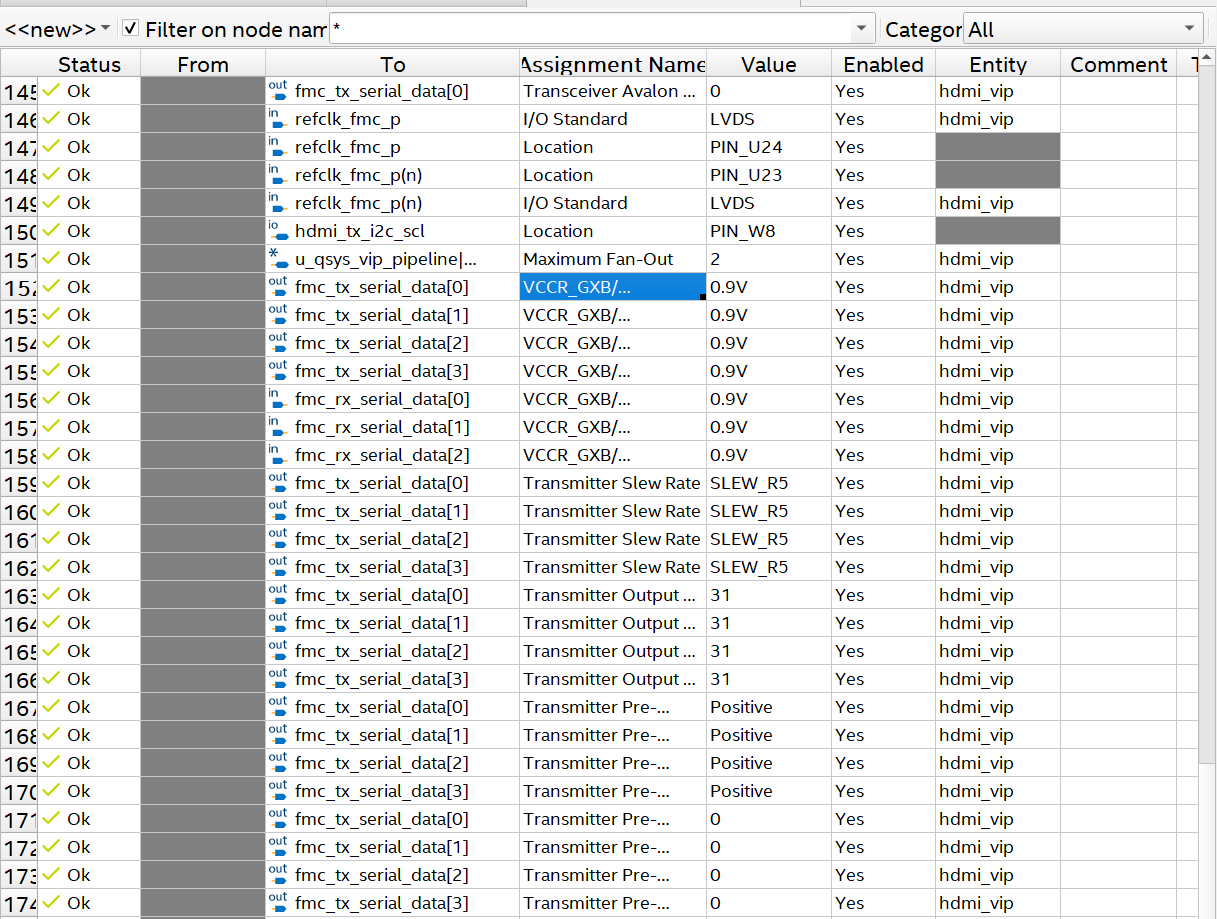

4. Assignment Editorを開きます

5. fmc_tx_serial_data[0:3]およびfmc_rx_serial_data[0:2]のVCCR_GXB/VCCT_GXB Voltageの設定を1.0Vから0.9Vに変えます。(一応、最新のHDMI Example Designの設定に合わせておきます)

6. もし StatusがOKではなく_Assignment is not valid for current device family_ と表示されている項目がある場合には再度同じパラメータの設定を行うことでエラーが消えます

プラットフォーム・デザイナー・システムの更新

-

インテル® Quartus® Prime ソフトウェアからプラットフォーム・デザイナーを立ち上げます

-

Platform Designer Systemとしてqsys_vip_pipeline.qsysを選択し、Openします

-

Update IP Cores画面をCloseします

-

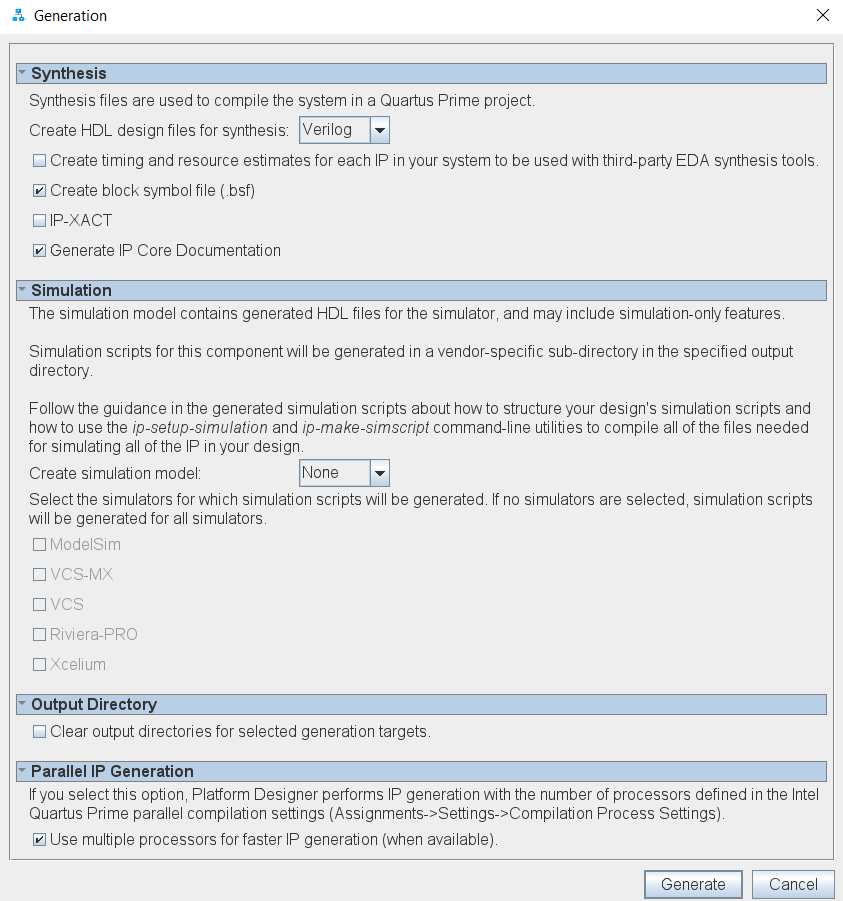

プラットフォーム・デザイナーからGenerate HDL を実行します

-

生成が終了したらプラットフォーム・デザイナーを閉じます

コンパイルと実行

- インテル® Quartus Prime ソフトウェアでコンパイルを行います

- インテル® Cyclone® 10 GX FPGA 開発キットのWeb pageにあるキットの配布資料をダウンロードします

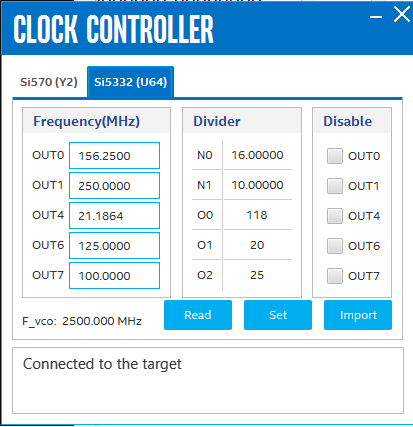

- ダウンロードした cyclone-10-gx-kit-collateral.zipを解凍し、examples\board_test_systemフォルダにあるClockController.exeを実行します

- Connected to the targetと表示されるのを待ってからImportでU64-Registers.txtを読み込みます

5. OUT1を250㎒に設定します。(もしその他のクロックが異なっているようでしたら、上記を参考に設定してください)

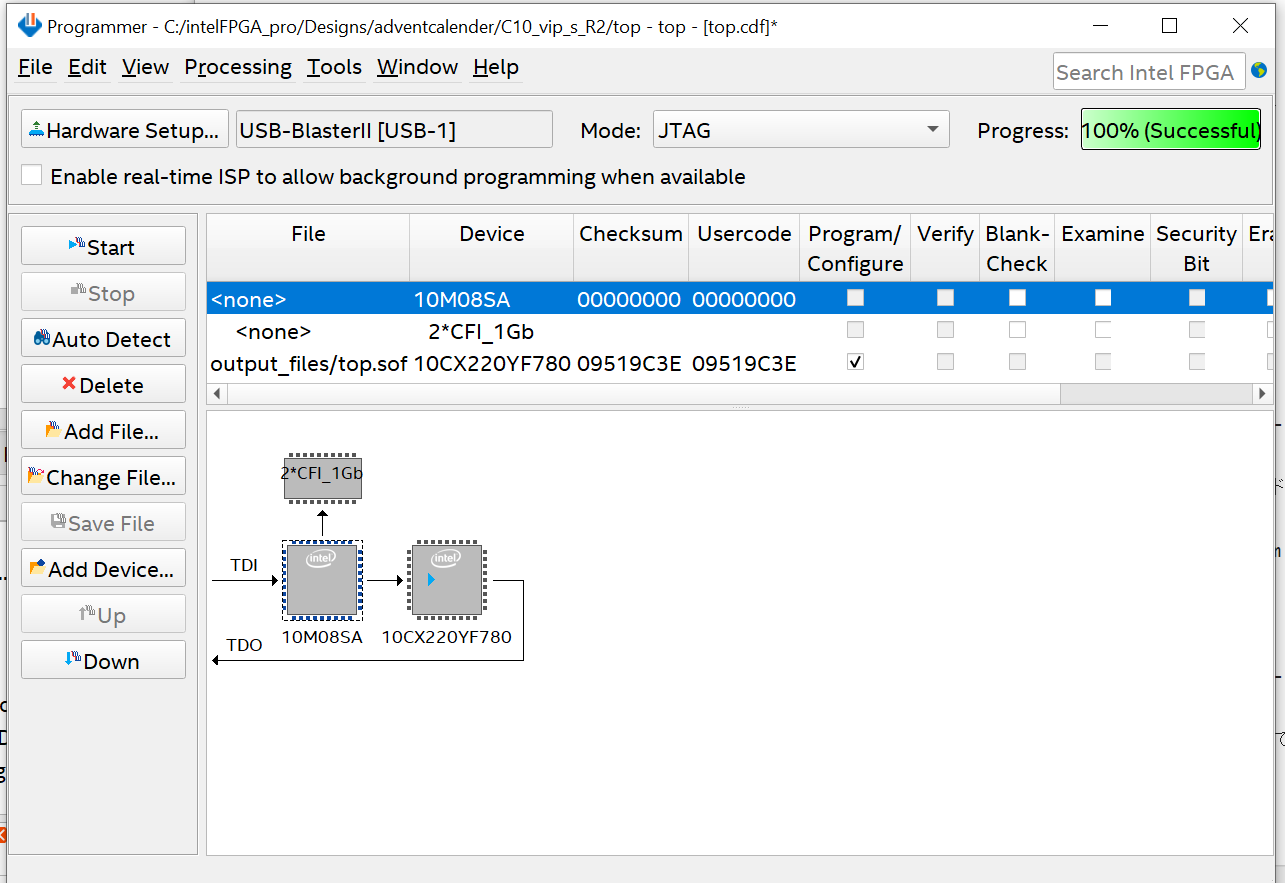

6. Programmerでtop.sofを書き込みます

7. Nios II Command Sellを起動して、nios2-terminalを実行します

実際のデザインの詳細や操作方法についてはユーザーガイドをご覧ください。

以上でサンプルデザインの実行はできるのですが、現状コンパイル結果のタイミング割れが解決できておりません。そのためか動作は不安定です。今後改善を図っていきたいと思います。

動作確認はビデオ&画像処理スイートの正式ライセンス下で確認しており、OpenCore Plusでの確認はしておりません。

Reference

- HDMI Intel FPGA IP User Guide

- HDMI Intel Cyclone 10 GX FGPA IP Design Example User Guide

- [Cyclone 10 GX HDMI 4Kp60 with Video and Image Processing Pipeline Reference Design User Guide] (https://www.intel.com/content/dam/altera-www/global/en_US/uploads/8/81/C10GX_hdmi_vip_ug.pdf)

- Video and Image Processing Suite User Guide

- Intel® Cyclone® 10 GX FPGA Development Kit User Guide

Notices & Disclaimers

Intel technologies may require enabled hardware, software or service activation.

No product or component can be absolutely secure.

Your costs and results may vary.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.