1.初めに

こんにちは、@shibatchii です。

普段はASICとかFPGAの設計をなりわいとしています。

昨年のアドベントでは「Microsemi社FPGA用のCPUコア紹介」ということでCPUコアIPを各種紹介しました。

その中の1つとしてRISC-VのIPも紹介しました。

RISC-V IPのその後の進展やこれからの予定など調査(というほど大げさなものでもないんですが)したことを書いてみたいと思います。

記事中の図はMicrosemi、Electronicdesign、SiFiveから引用しています。

2.MicrosemiのRISC-V扱い

1.Webページ

一年前は Technology Solutions/Embedded Processing MSS/RISC-V CPUs というかなり下の階層にCPU IPコアのうちの1つという扱いでひっそりとありました。

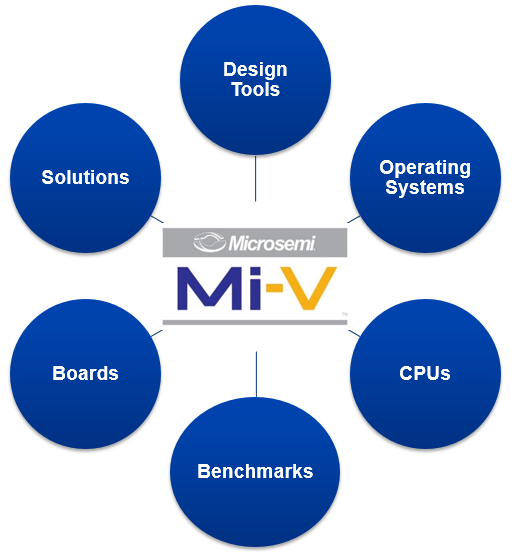

現在は Mi-V Embedded Ecosystem という項目に格上げされています。

https://www.microsemi.com/products/fpga-soc/mi-v-ecosystem

「With the Mi-V™ ecosystem, Microsemi with industry leaders, aims to increase adoption of RISC-V ISA and Microsemi's soft CPU product family.」

となっており、Mi-V(たぶんMicrrosemi RISC-V)をトレードマークにしたり、CPU IPとしてだけでなく DesignTool,RISC-V Soft CPUs,Boards,Solutions,Operating Systems など統合して推し進めていくというかなり力をいれたものになっています。

2.GitHub

MicrosemiはRISC-Vサポート時にGitHubも用意しました。

https://github.com/RISCV-on-Microsemi-FPGA

最初のころはSmartFusion2用のサンプル位しかなかったのですが、このところRTOS含め充実させてきています。

1.サンプル対応ボード

RISC-VのFPGAデザインやソフトのサンプルがGitHubあるボードです。ボードを持っていればダウンロードしてサンプル(LチカとTickTackTone)を走らせてみることができます。

・M2S090-Security-Eval-Kit

SmartFusion2 Security Evaluation Kit sample RISC-V Libero project(s)

・M2S060-Arrow-SF2Plus

SmartFusion2 M2S060 "Arrows SmartFusion2 Plus" development board sample RISC-V Libero project(s)

・M2S150-Advanced-Dev-Kit

SmartFusion2 M2S150 Advanced Development Kit sample RISC-V Libero project(s)

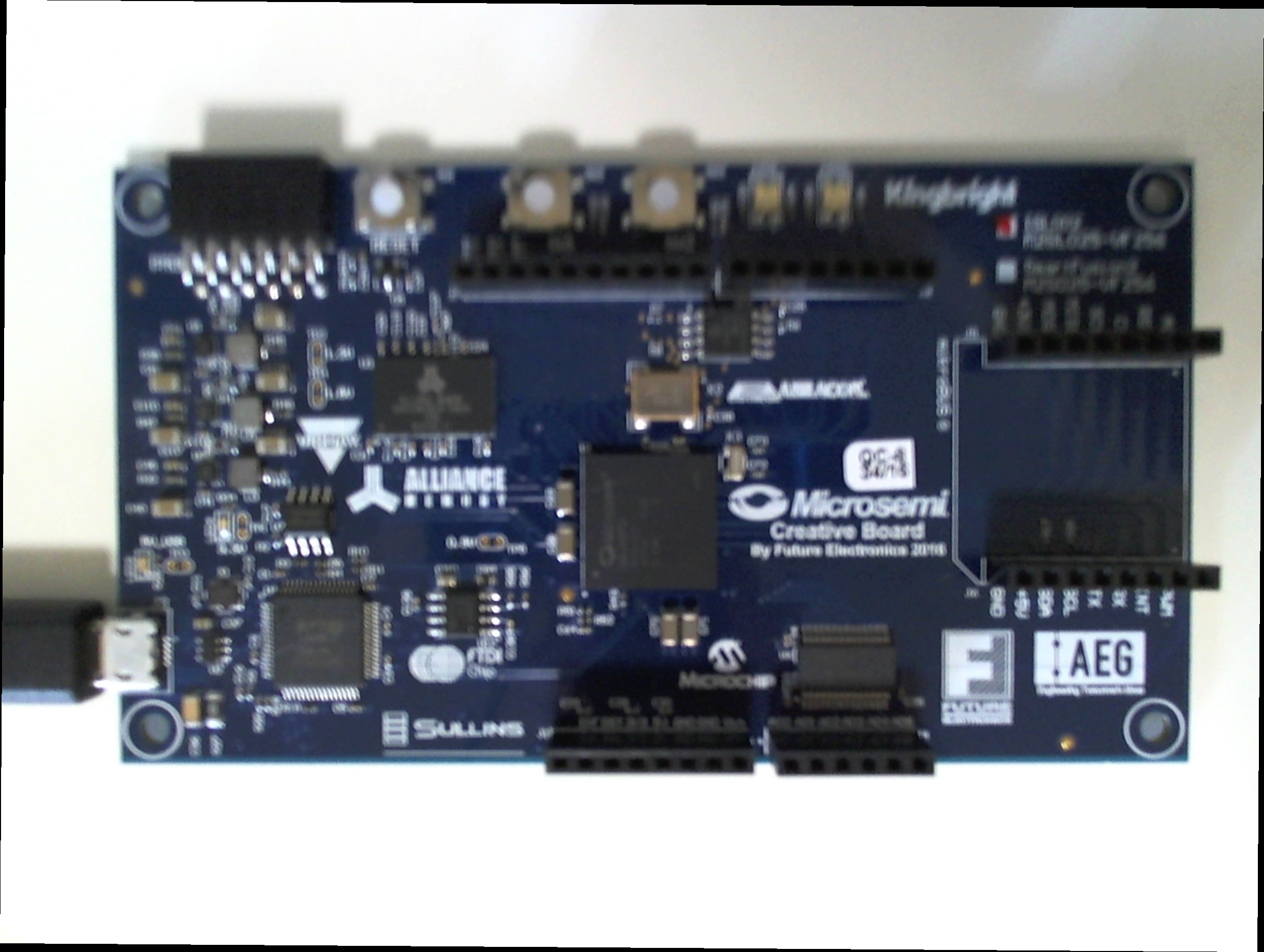

・M2GL025-Creative-Board

Igloo2 M2GL025 Creative Development Board

・M2S025-Creative-Board

SmartFusion2 M2S025 Creative Development Board

・MPF300T-PolarFire-Eval-Kit

PolarFire FPGA sample RISC-V designs

・RTG4-Development-Kit

Sample RISC-V Libero projects for the RTG4 Development Kit

この中で手に入りやすいのは FutuerElectornicsの M2GL025-Creative-Board ですね。$100以下で買えます。ただし国内での扱いが無いので個人輸入しないといけません。

2. RTOS

つい最近ですが、RTOS(リアルタイムOS)もサポートされ始めました。まだ実際に試してはないのですが時間をみて試してみようと思っています。ただ使い方の説明とかが無いのでまずは解析からですね。

・FreeRTOS

組み込みシステム用のオープンソースのリアルタイムOS

・Mynewt

Apache Mynewt、オープンソースでモジュール形式のリアルタイムOS

・LiteOS

中国Huawei TechnologiesのIoT向け軽量OS

・uCOS

Micrium Software (Silicon Labs)のリアルタイムOS

FreeRTOSは最近Amazonに買収されてMITライセンスになり話題になりましたね

またMicrosemiのWebページでは上記以外に、

・ThreadX

Express Logic社のリアルタイムOS

も対応OS例に挙がっています。

3. 開発ツール

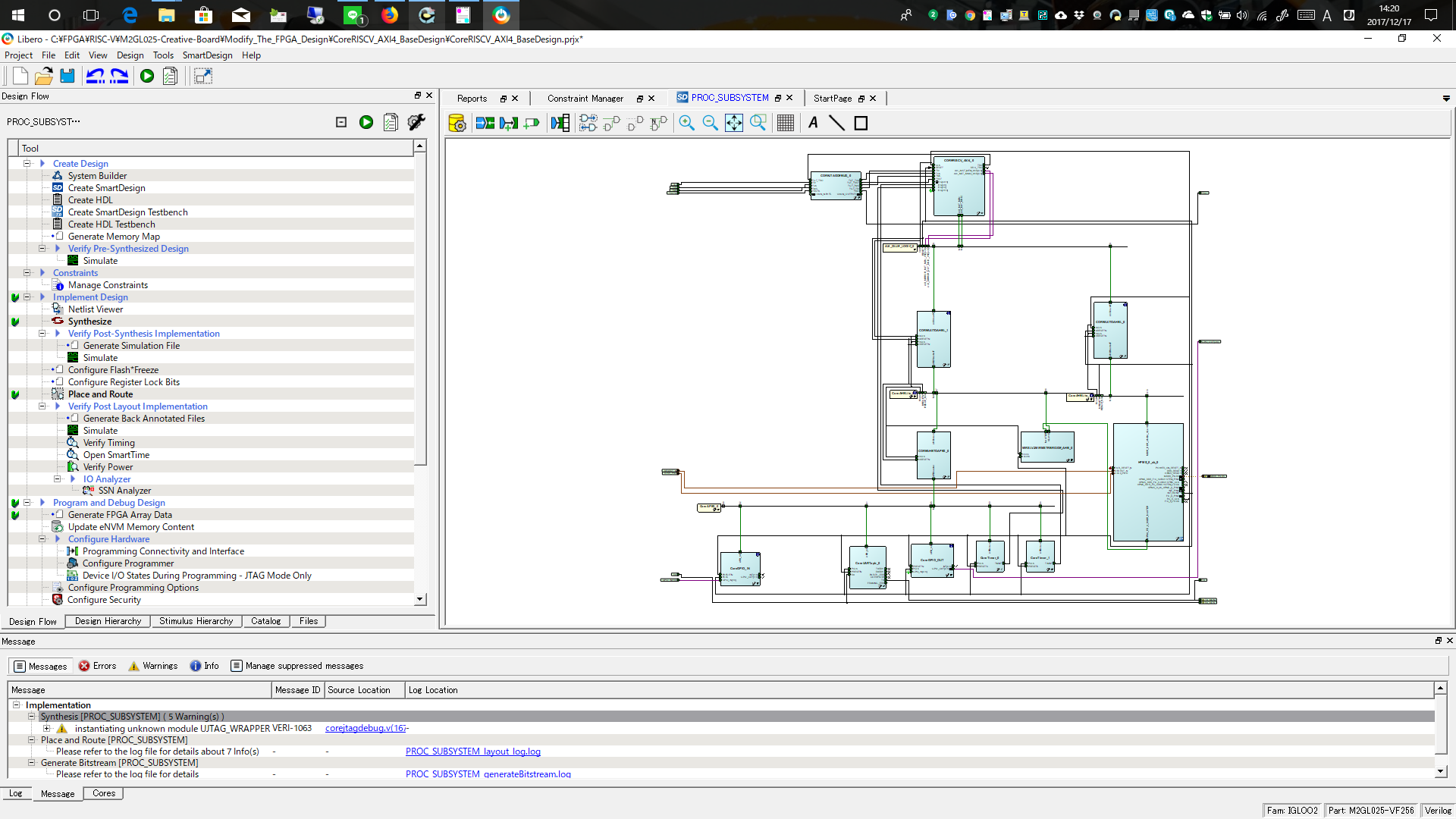

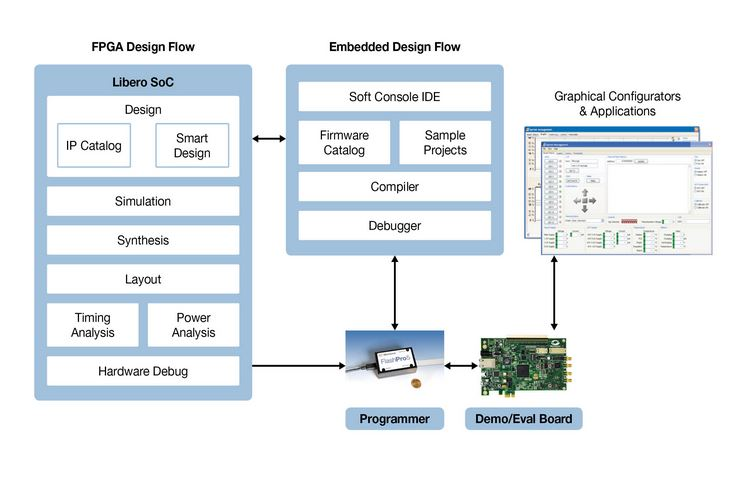

1.LiberoSoC

FPGAの統合開発ツールです。

https://www.microsemi.com/products/fpga-soc/design-resources/design-software/libero-soc#downloads

2017/12/17現在の最新バージョンは v11.8 SP2 です。Windows版とLinux版があります。

SystemBuilderを使用してのシステム構成や、合成、フィッティング、ビットデータ生成、書き込み、デバッグなどが一式になっています。

使っていて思うのは、RISC-V IPがAXIバスIFとして提供されているのでいままでの周辺IPがAXI-AHBブリッジとかAHB-APBブリッジを通すことによりほぼそのまま使えて便利ということですね。

コアが変わったから周辺も全部作り直し!とかならないところが良いです。デバイスドライバとかもそのまま使えますしね。

2.SoftConsole

RISC-VやCoretex-M3のソフト開発環境です。

https://www.microsemi.com/products/fpga-soc/design-resources/design-software/softconsole

2017/12/17現在の最新バージョンは v5.2 です。こちらもWindows版とLinux版があります。

RISC-Vサポートした当時、LINUX版でしかRISC-V対応していなくて、FPGA部の構成はWindows版で行って、ソフトはLINUX版で行うとか、ライセンスがーとか、いろいろめんどくさかったのですが、v5.1からWindowsでもサポートされたので開発がやり易くなりました。

使ってて思うのはCoretex-M3のソフト開発と同じ環境でできるので新たに環境を立ち上げたり学習する必要がほとんど無いのでRISC-Vへの移行もやり易いねってとこです。(ただし割り込み系は除く)

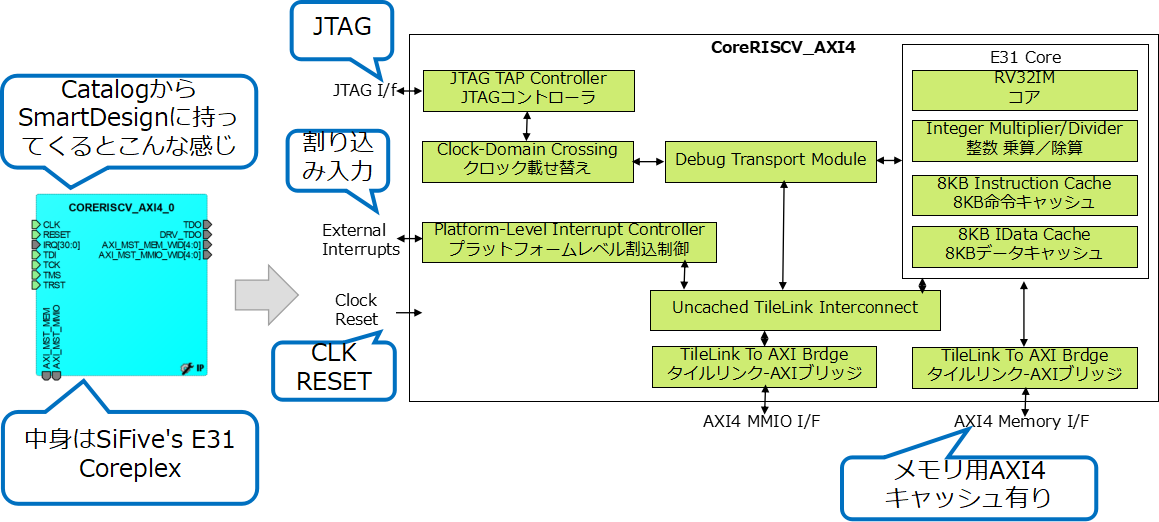

4.RISC-Vコア

おまたせしました。RISC-Vコアの話です。

実はこの一年、このRISC-Vコアは大きな展開や変更はありませんでした。

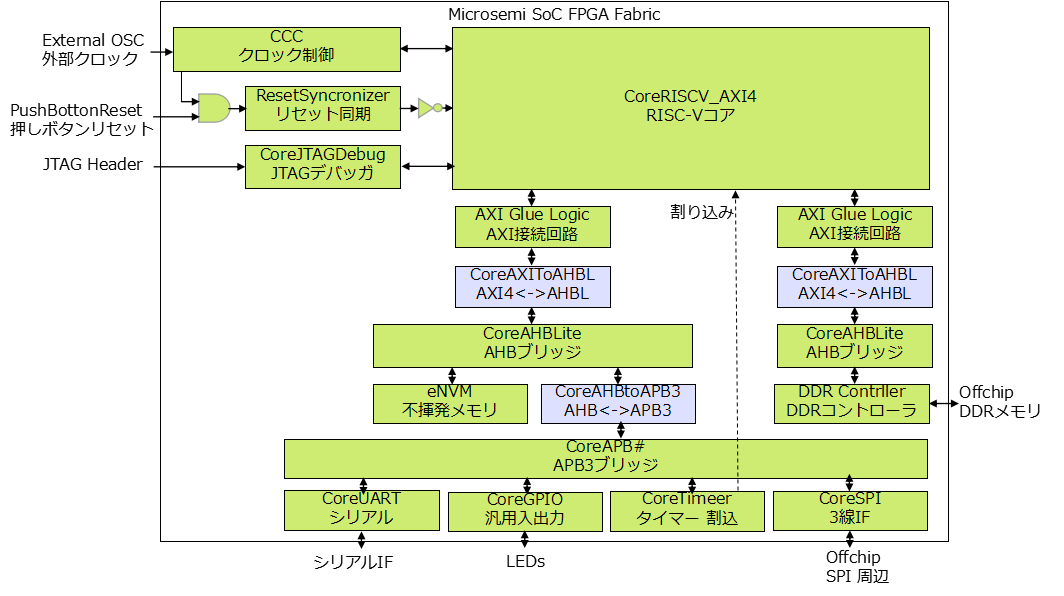

下記のような構成になっていてRV32IMベースです。要するに乗除算が付いているだけで後は素のRISC-Vというシンプルなものです。

これをベースに先のLチカ回路を構成するとこのようになります。GitHubにあるLチカサンプルの例です。

うーむ、AMBA 3兄弟総出演ですな。

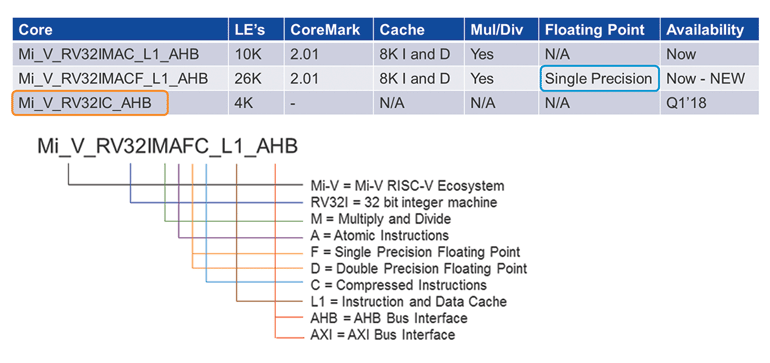

最近追加されたのが下の構成2種類。バスがAHBバスとなり、コアがIMA,IMAFとなっています。いままでのIMにアトミック命令が増えた物と浮動小数点が増えた物がリリースされました。

AXIで出していても上図にあるように結局AXI-AHBブリッジ通すのでいきなりAHBでいいんじゃね、となったのかもしれません。

また周辺IPがAHB I/FとAPB I/Fのが多いのも理由かもしれません。

3.Microsemi RISC-V の今後

このところのニュースリリースとかRISC-V関連のTwitterとか見ていると今後もかなり力を入れてRISC-V対応を進めていくようです。

1. 新しいRISC-Vコア

1.RV32Iのコア展開

Electronicdesignからの情報によると、さらにコア展開がある模様です。

http://www.electronicdesign.com/embedded-revolution/risc-v-fpga-design-leaps-forward-mi-v

2. 64bitコア展開

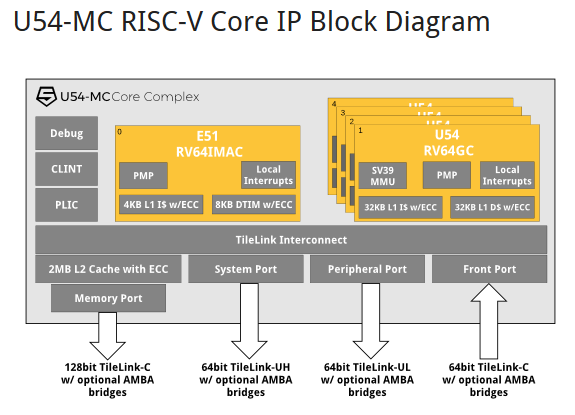

また SiFive社はMicrosemi PolarFire FPGAに SiFive U54-MC RISC-Vコアコンプレックス(Freedom U500 SoC)をインプリ、サポートするボードを2018第一四半期に出す模様です。OSはLinuxもサポートするようです。

https://www.sifive.com/posts/2017/11/28/sifive-and-microsemi-expand-relationship-with-strategic-roadmap-alignment-and-linux-capable-risc-v-development-board/

ただPolarFire FPGAはミッドレンジですがいわゆる「お高いんでしょう」になりそうで、ホビーユースで手に入る価格帯になるボードになるかは不明ですね。

2. 開発環境など

1.組み込み解析機能IP

UltraSocによるとトレースやデバッグなどの組み込み解析機能IPをMicrosemi RISC-V用にサポートするとのこと。

https://www.ultrasoc.com/ultrasoc-selected-by-microsemi-for-growing-risc-v-product-range/

2.ソフトウェアシミュレーション環境

ImperasはVirtual Extendable Platform KitでMicrosemiのRISC-Vソフトコア上で実行されるソフトウェアの開発、デバッグ、テストのためのソフトウェアシミュレーション環境を提供するとのこと。

https://investor.microsemi.com/2017-12-12-Microsemi-and-Imperas-Announce-Extendable-Platform-Kit-for-Microsemi-Mi-V-RISC-V-Soft-CPUs

4.終わりに

今回はMicrosemi社のRISC-Vにスポットを当てて紹介しました。

RISC-Vコアを使ったFPGAの設計とかも「FPGAでRISC-V~」というタイトルでブログにすこしずつ書いています。

http://shibatchii.cocolog-nifty.com/blog/

それでは、また。@shibatchii