簡単な足し算プログラムを書いてみる

Python で足し算プログラムを書いてみます。テストベンチも作ります。

adder.py

from polyphony import testbench

def adder(a, b):

return a + b

@testbench

def test():

v = adder(1, 2)

print("v = ", v)

test()

味気なですが Python で実行してみましょう。

Pythonで実行

> python adder.py

v = 3

うまく動きました。iverilog を使ったシミュレータではどうでしょう?polyphony の github にある simu.py で実行してみます。

iverilogで実行

> ../polyphony/simu.py adder.py

Compiling: [=========================] 100% ... printresouces

(99, 66, 2)

v = 3

170:finish

うまくいったようです。-vm オプションでモニターが出来ます。

-vmオプションを使う

> ../polyphony/simu.py -vm adder.py

Compiling: [=========================] 100% ... printresouces

(99, 66, 2)

0:adder_0_in_a= x, adder_0_in_b= x, adder_0_out_0= x

10:adder_0_in_a= x, adder_0_in_b= x, adder_0_out_0= 0

110:adder_0_in_a= 1, adder_0_in_b= 2, adder_0_out_0= 0

130:adder_0_in_a= 1, adder_0_in_b= 2, adder_0_out_0= 3

v = 3

170:finish

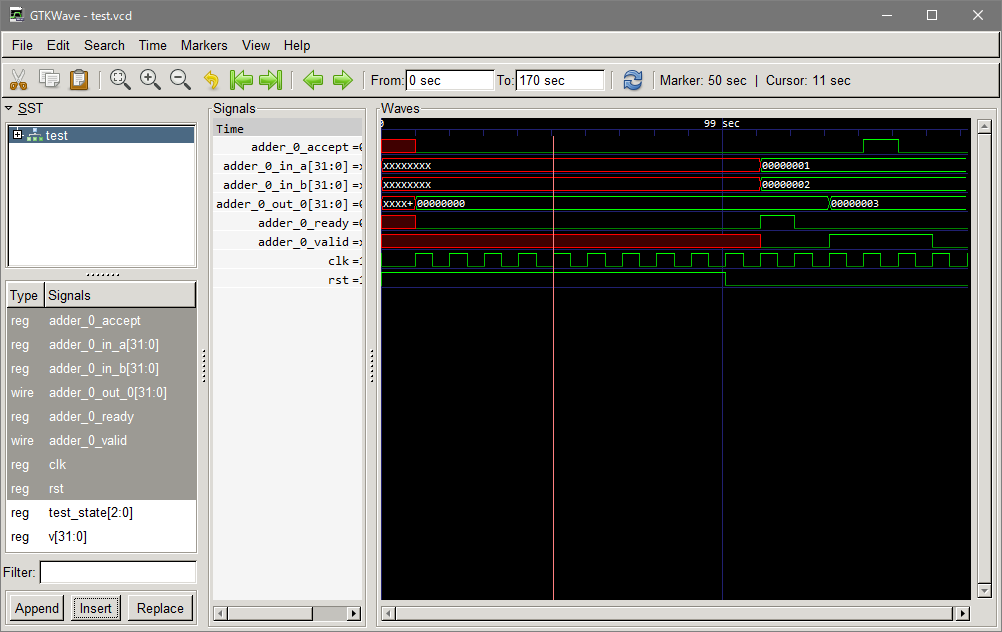

うまくいっているような気がします。-vd オプションで vcd ファイルを生成します。

-vdオプションを使う

> ../polyphony/simu.py -vd adder.py

Compiling: [=========================] 100% ... printresouces

(99, 66, 2)

VCD info: dumpfile test.vcd opened for output.

v = 3

170:finish

test.vcd が出来ました。gtkwave で見てみましょう。

うまくいっている気がします。