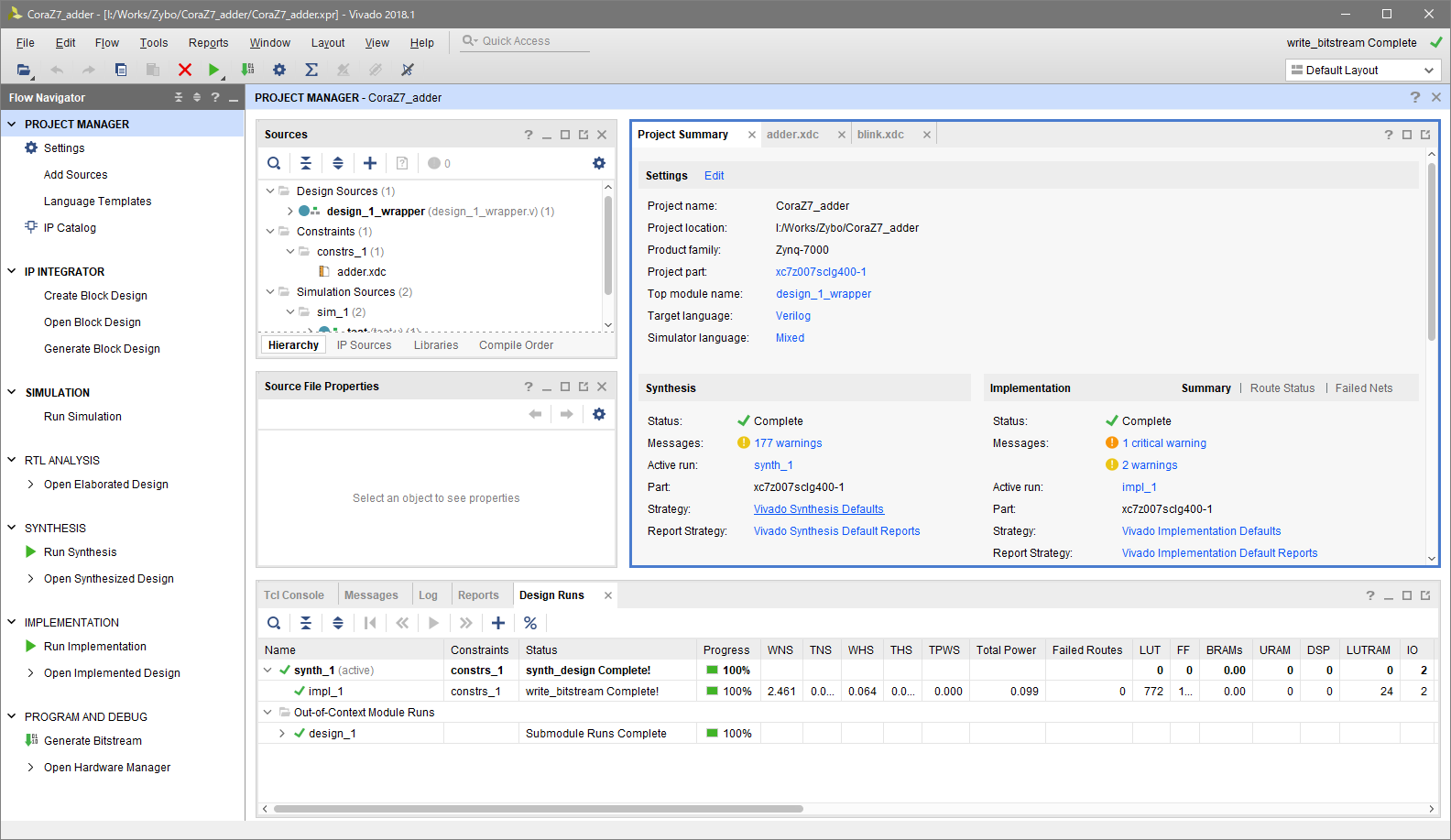

Vivado で合成

Python で書いた足し算プログラムを Polyphony でコンパイルし Vivado のシミュレータで動作確認をしてから Cora Z7 で動くように合成しました。

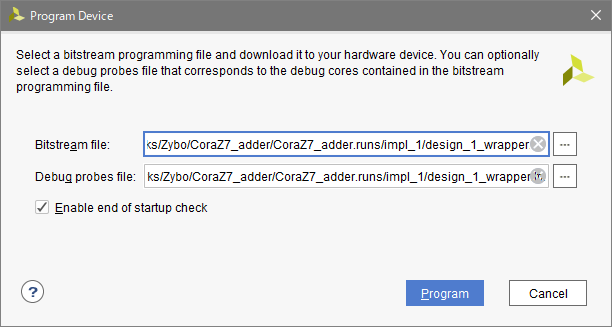

Program Device でダウンロード

VIO をつかったのでデバッグ用の設定になっています。

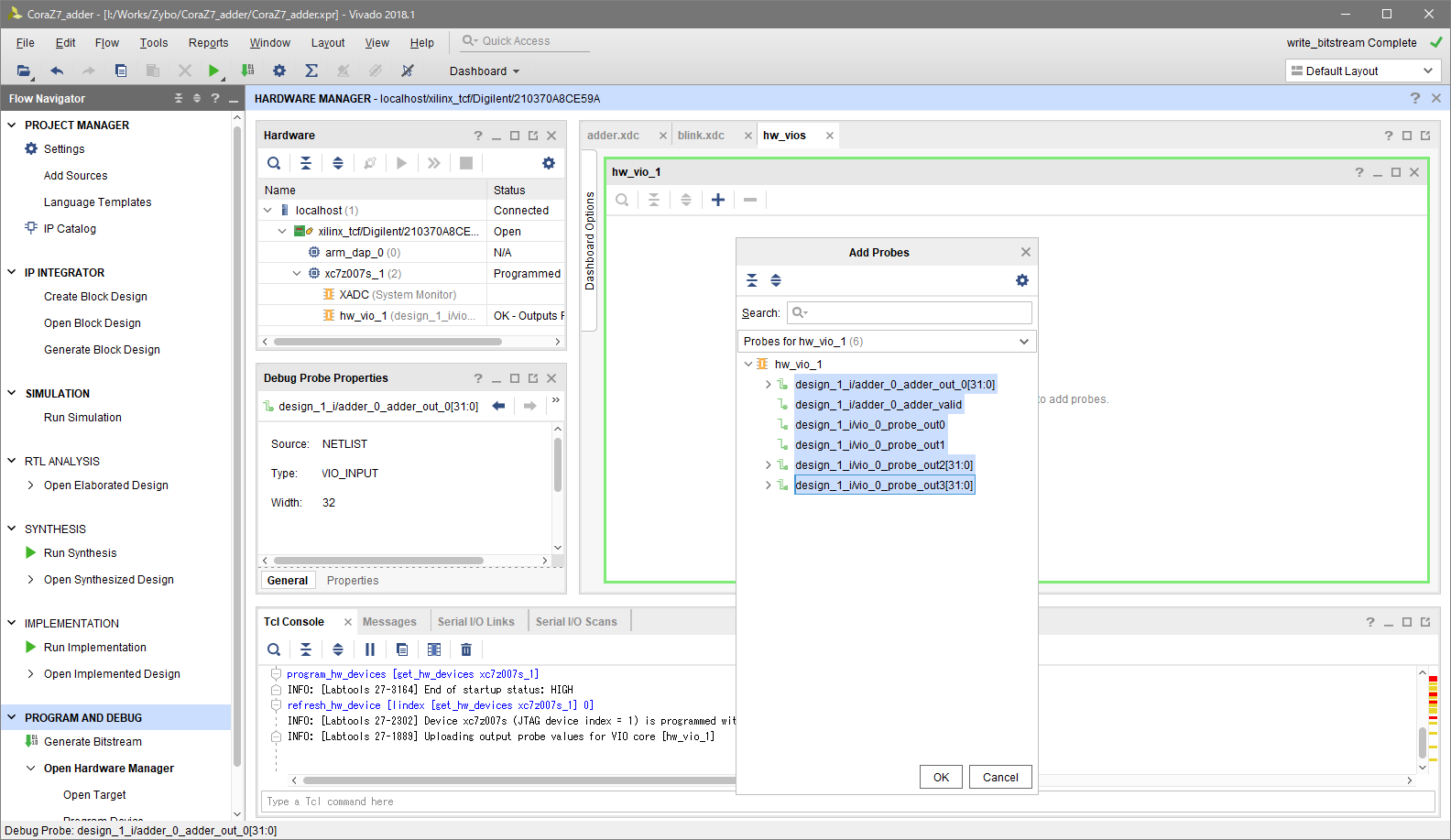

hw_vio_1 に信号線追加

VIO の操作画面が出る

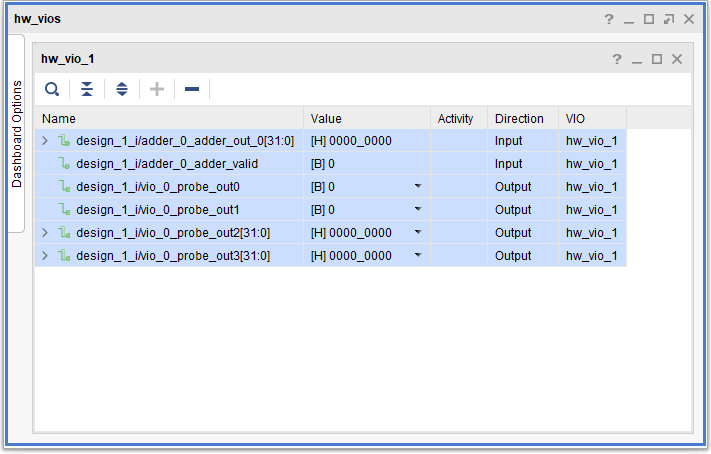

VIO で操作

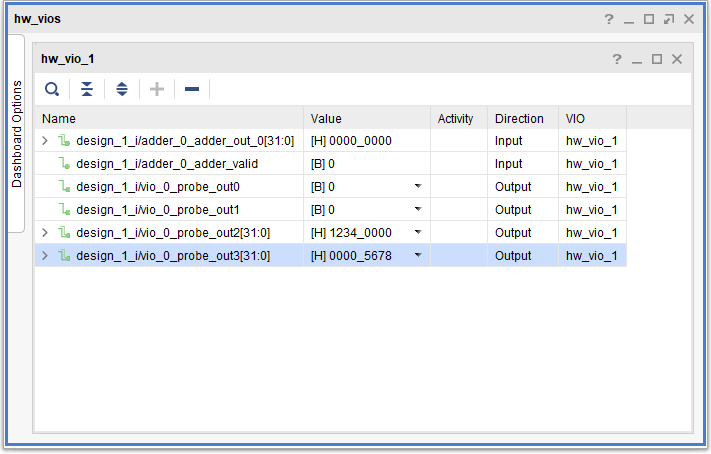

足す数を設定

vio_0_probe_out2 に 0x12340000 を vio_0_probe_out3 に 0x5678 を入れてみます。

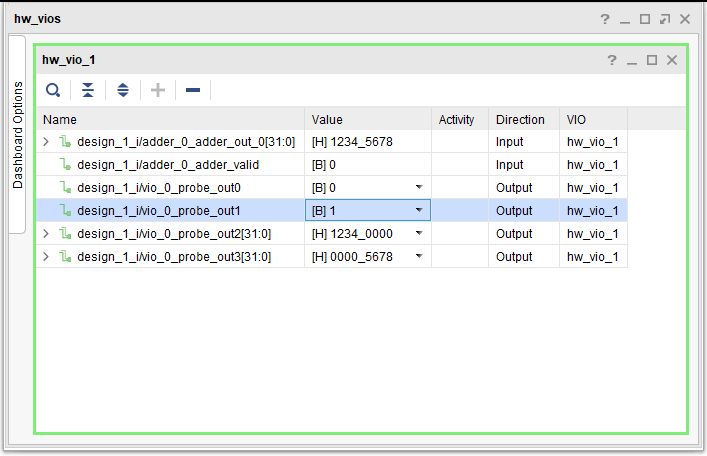

実行

vio_0_probe_out0 を 1 にします。すぐに結果が返ってきて adder_0_adder_out_0 に結果が adder_0_adder_valid に 1 が立ちました

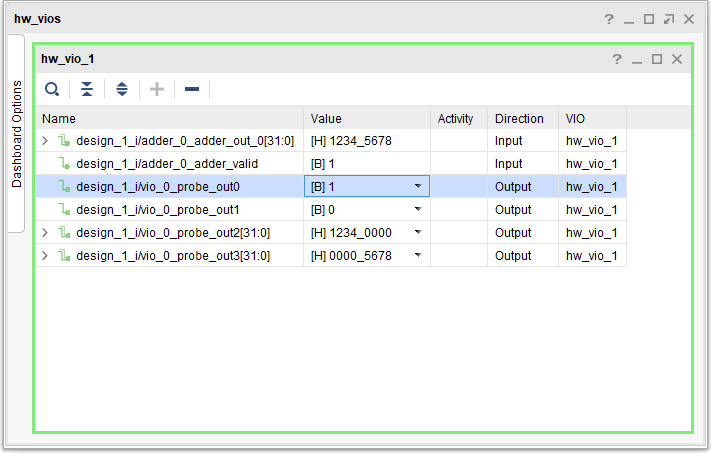

後処理

vio_0_probe_out0 を 0 に戻し、vio_0_probe_out1 を 1にしましょう。アクセプトしたことになり adder_0_adder_valid が 0 に戻りました。

VIO 注意点

どういうわけか VIO は前の GUI の情報をもっているようで、二度目以降、BitStream をダウンロードした時に output の値が前の時のが画面上に残っています。しかし、実際にはデフォルトの値が出力されているようです。なので、GUI 終了時にはデフォルトの値に戻してから終了しましょう。