概要

個人的に遭遇したエラーと解決した結果を羅列しました

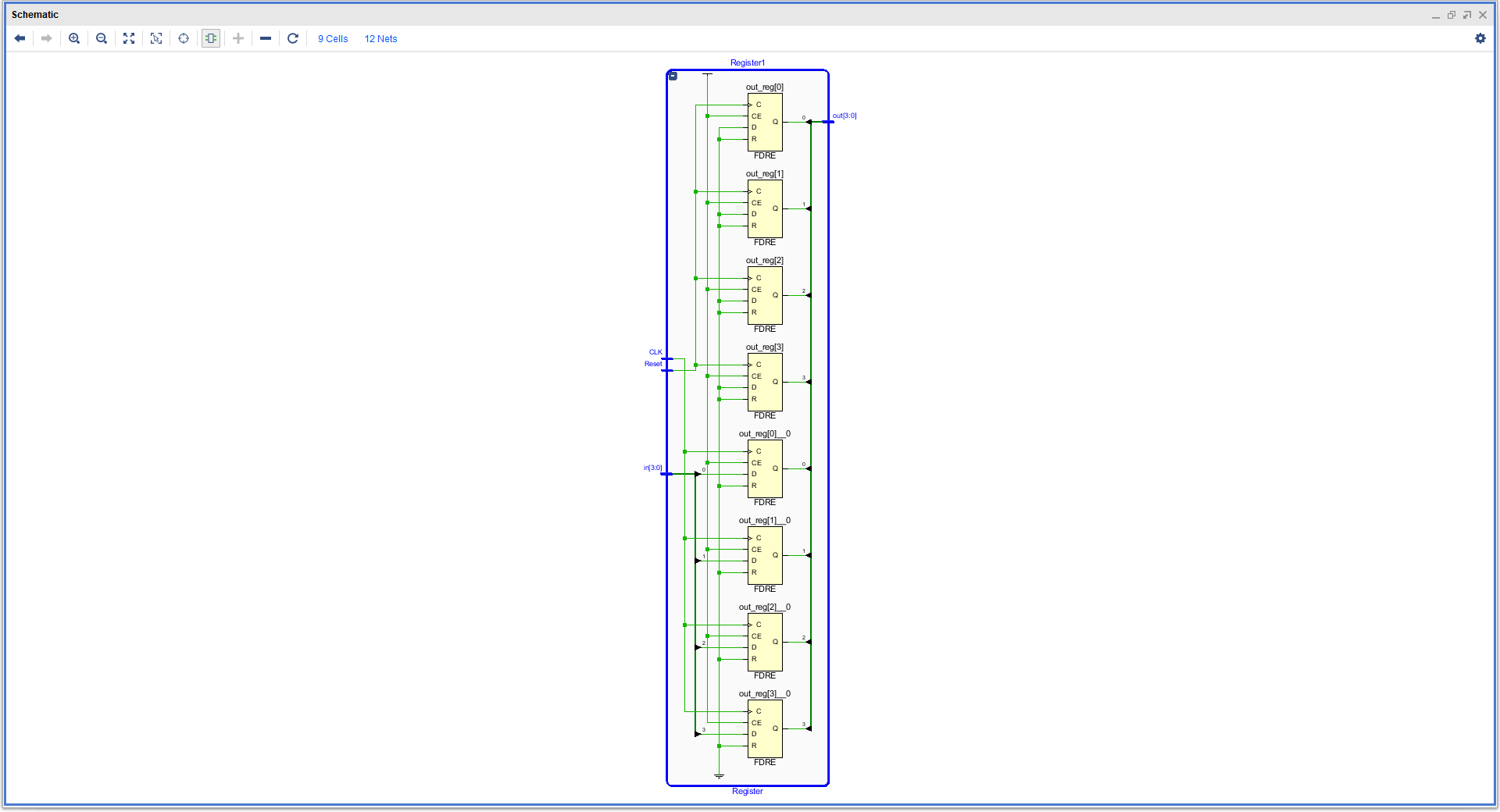

複数のalways文

module Register(

input [3:0] in,

output reg [3:0] out,

input CLK,

input Reset

);

always @(posedge CLK)

begin

out <= in;

end

always @ (posedge Reset)

begin

out <= 4'h0;

end

endmodule

[DRC MDRV-1] Multiple Driver Nets:

Net Register1/out[0] has multiple drivers:

Register1/out_reg[0]__0/Q, and Register1/out_reg[0]/Q.

リセットを別にして記述した結果,4bitRegisterを作ろうとしたのに,Registerが2set(8bit)生成されてしまっている.

そして,レジスタ二つの出力が直接接続されてマルチドライバーエラーを起こしている.

always文を一つにまとめれば,解決した

orderd port and named port

[Synth 8-2543] port connections cannot be mixed ordered and named

multiplexer multi1(.in1(switch[3:0]),in2(switch[7:4]), .out(out), .select(in[0]));

というように,モジュールを接続した際に発生しました.

原因

in2(switch[7:4])

で$.$をつけ忘れているため発生しました.

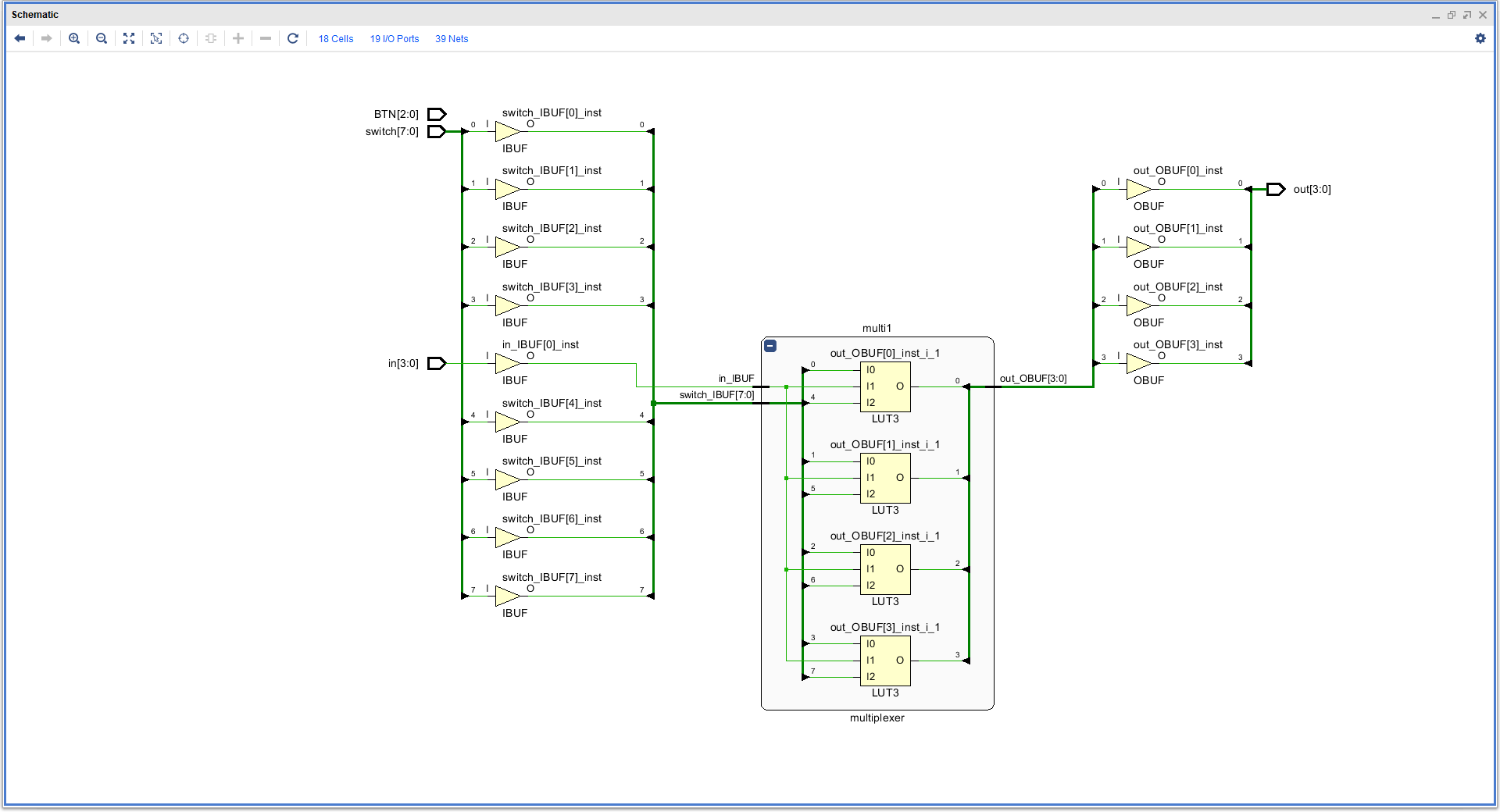

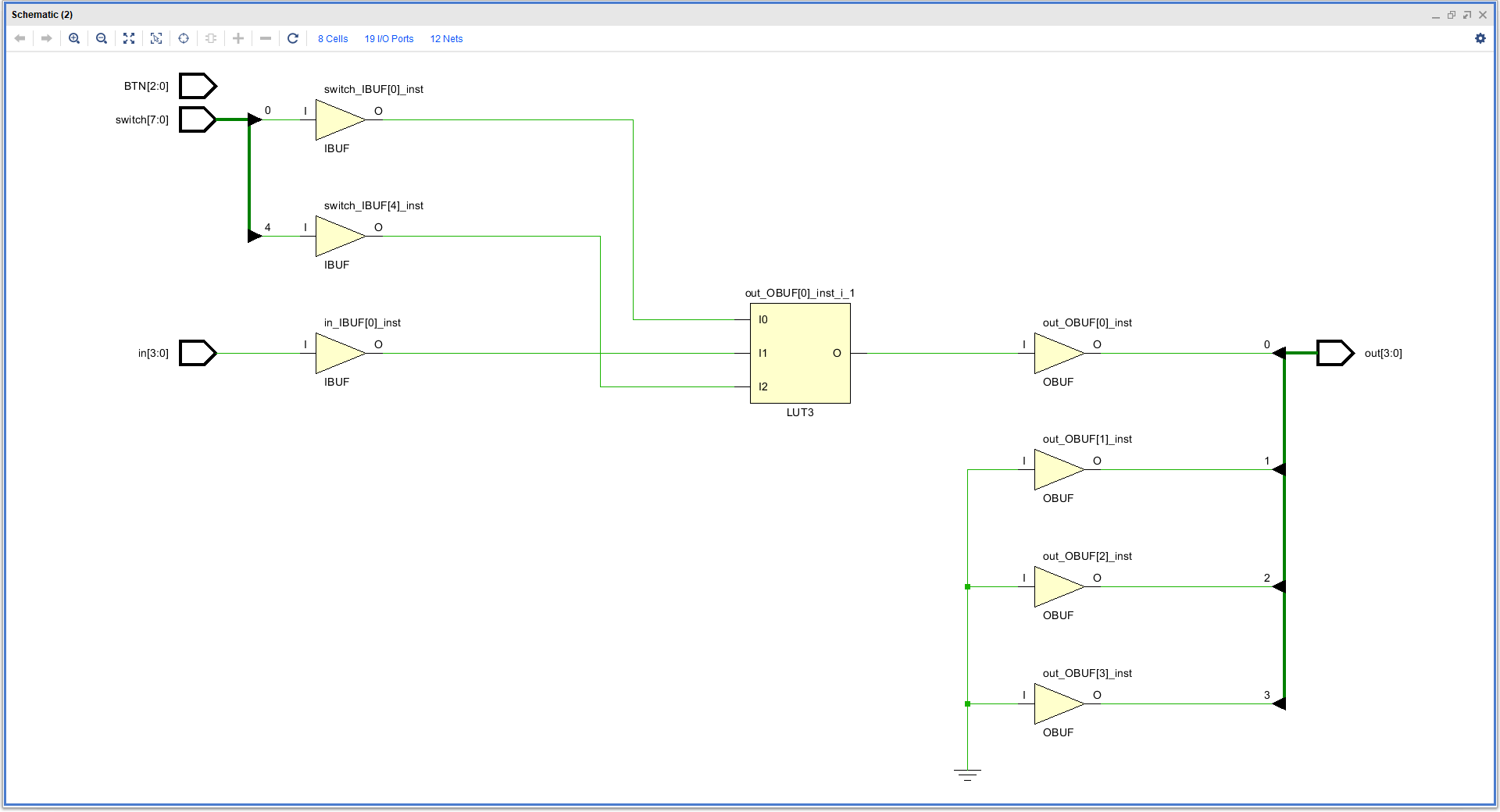

多bit線の接続

module GAWA(

input [3:0] in,

output [3:0] out,

input [2:0] BTN,

input [7:0] switch

);

multiplexer multi1(.in1(switch[3:0]),.in2(switch[7:4]), .out(out), .select(in[0]));

endmodule

module multiplexer(

input [3:0] in1,

input [3:0] in2,

output[3:0] out,

input select

);

function [3:0] Select;

input select;

input in1;

input in2;

begin

if(select == 1)

Select = in1;

else

Select = in2;

end

endfunction

assign out = Select(select,in1,in2);

endmodule

見苦しいコードだが...

結果

0bit目以降はGNDになってしまっている.実際,FPGAに導入しても同様の結果になる.

原因

function [3:0] Select;

input select;

input in1;

input in2;

begin

if(select == 1)

Select = in1;

else

Select = in2;

end

endfunction

で input in1,in2 のbitサイズを指定していない.指定しないと1bitになってしまう.

結果,使用するモジュールでおかしなことになる.

これはエラーを吐かないことに驚き.

思った動作をしない

bit ファイルの選択を別のものにしていたため,ずっと変更されていなかった.

これはバカすぎる.

デマルチプレクサの生成方法

function文,caseで作りました.

[3:0]selectの情報によって,CLKを[15:0]OUTのどれに接続するか選択できます.

module DeMultiplexer(

input CLK,

input [3:0] Select,

output [15:0] Out

);

function [15:0]out;

input [3:0]Select;

input in;

case(Select)

4'h0:out[0] = in;

4'h1:out[1] = in;

4'h2:out[2] = in;

4'h3:out[3] = in;

4'h4:out[4] = in;

4'h5:out[5] = in;

4'h6:out[6] = in;

4'h7:out[7] = in;

4'h8:out[8] = in;

4'h9:out[9] = in;

default : out = 16'h0000;

endcase

endfunction

assign Out = out(Select,CLK);

endmodule

module GAWA(

input clock,

input [3:0]SW,

output [3:0]LED

);

reg [26:0] D;

always @ (posedge clock)

begin

D <= D+1;

end

wire [15:0]Out;

DeMultiplexer DeMultiplexer(.CLK(D[26]), .Out(Out),.Select(SW));

assign LED[0] = Out[0];

assign LED[1] = Out[1];

assign LED[2] = Out[2];

assign LED[3] = D[26];

endmodule

これで,実行すると.確かにSelectの選択によって,outの出力が選択できた.

しかし,LEDにはOut[0]~[2]までしか指定していないのに,Select->LED の対応は

0->0

1->1

2->2

3->2

4->0

5->1

6->2

7->2

8->OFF

9以降OFF

Selectが3~7の動作がおかしい

原因

case(Select)

4'h0:out[0] = in;

4'h1:out[1] = in;

4'h2:out[2] = in;

4'h3:out[3] = in;

4'h4:out[4] = in;

4'h5:out[5] = in;

4'h6:out[6] = in;

4'h7:out[7] = in;

4'h8:out[8] = in;

4'h9:out[9] = in;

default : out = 16'h0000;

endcase

case文でoutの1bitのみの動作を指定しているためではないか?

module DeMultiplexer(

input CLK,

input [3:0] Select,

output [15:0] Out

);

function [15:0]out;

input [3:0]Select;

input in;

case(Select)

4'h0:begin

out[0] = in;

out[15:1] = 0;

end

4'h1:begin

out[0] = 0;

out[1] = in;

out[15:2] = 0;

end

4'h2:begin

out[1:0] = 0;

out[2] = in;

out[15:3] = 0;

end

4'h3:begin

out[2:0] = 0;

out[3] = in;

out[15:4] = 0;

end

4'h4:begin

out[3:0] = 0;

out[4] = in;

out[15:5] = 0;

end

4'h5:begin

out[4] = 0;

out[5] = in;

out[15:6] = 0;

end

4'h6:begin

out[5] = 0;

out[6] = in;

out[15:7] = 0;

end

4'h7:begin

out[6] = 0;

out[7] = in;

out[15:8] = 0;

end

4'h8:begin

out[7] = 0;

out[8] = in;

out[15:9] = 0;

end

4'h9:begin

out[8] = 0;

out[9] = in;

out[15:10] = 0;

end

default : out = 16'h0000;

endcase

endfunction

assign Out = out(Select,CLK);

endmodule

ほかのbitもちゃんと指定したところ問題なく動作した.

しかし,もっといい書き方があると思うので,どなたか教えてください.

if文の論理積

if(a>5 and b>2)

はエラーになります.

if(a>5 && b>2)

で通ります.