概要

「その1」 からの続きです。

SOY2 で Lチカ、まとめる時間があまり取れずに、小出しです。。。

今回は、少しだけ進めて、インプリまでです。

(「その3」へつづく)

SiTCP ライブラリ上書き

前回、SOY2出荷時ソースとSiTCPライブラリを入手しました。

SOY2出荷時ソースのディレクトリに、SiTCPライブラリを上書きします。同一ファイルは置き換えます。

Vivado でインプリ

Vivado で、新規プロジェクトを作成

*.v と *.edf をソースとして選択します。

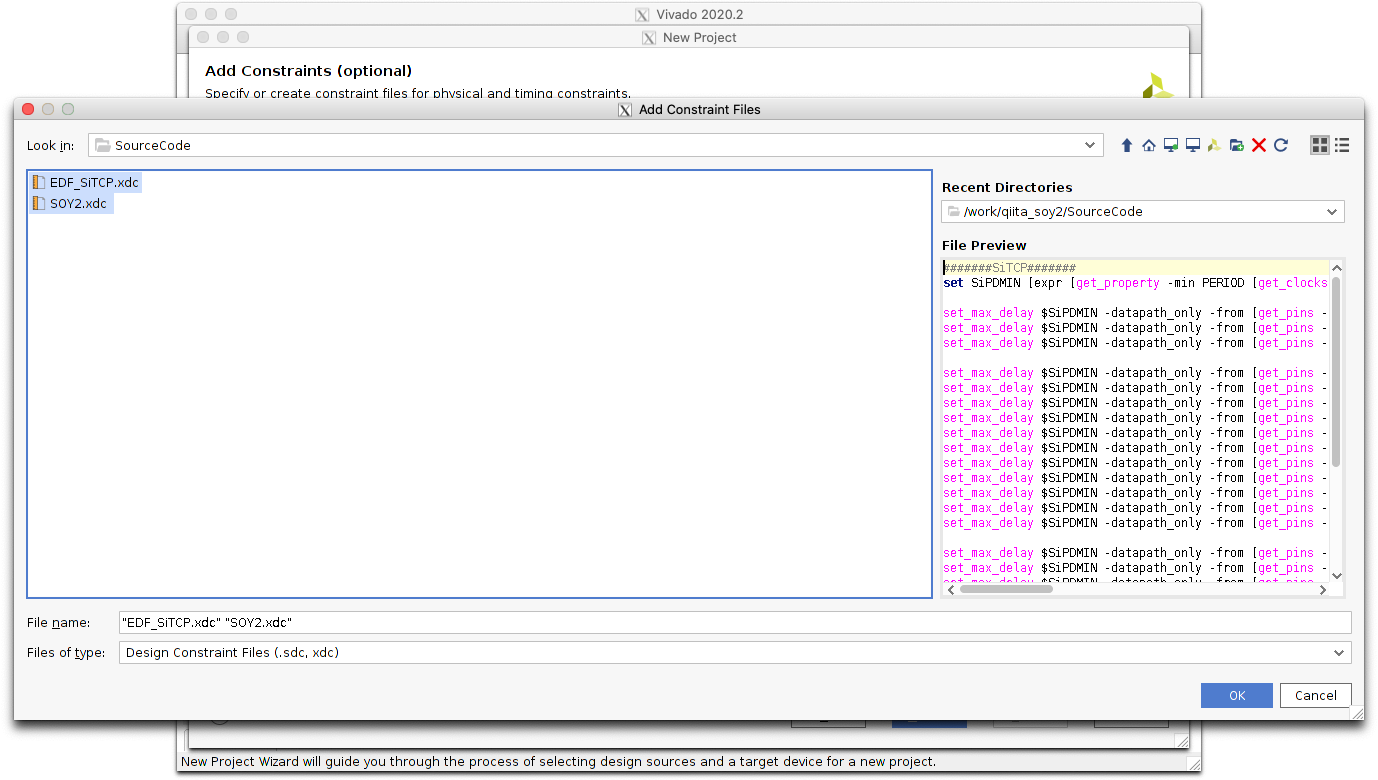

*.xdc を指定します。

制約ファイルは、SOY2.xdc, EDF_SiTCP.xdc の順番になるようにしてください。

順番が逆になってしまったときは、

[Edit Constraints Sets...] にて、修正できます。

"xc7s25ftgb196-1" を選択してください。

[Generate Bitstream] をクリックして、bitファイルを生成します。

※ Vivado は、Docker 上で動かしています。

「Xilinx の開発ツールを Docker コンテナに閉じ込める」 参考にしました。

その後は。。。

生成した bit ファイルを mcs ファイルに変換して、SiTCP ユーティリティを用いて、SOY2 に書き込みます。

そして、動作確認ですが、このあたりは来週にまとめられればと思います。