記事タイトル:

Dフリップフロップとタイミングチャート入門:シフトレジスタで学ぶクロック同期設計

1. はじめに ― デジタル回路は「時間で動く」

デジタル回路では、0と1の信号が時間とともにどう変わるかが非常に重要です。

その変化を表すのが タイミングチャート です。

2. クロック信号とDフリップフロップの基本

クロック信号(CLK)とは?

- デジタル回路の動作を制御する「拍子木」

- 矩形波で表現され、**立ち上がり(↑)か立ち下がり(↓)**で信号を反映

Dフリップフロップ(D-FF)の動作

- D入力:与えたいデータ

- CLK:タイミングトリガー

- Q出力:記憶された値

特性:

Q(t+1) = D(t) (ただしCLKが↑のとき)

3. タイミングチャートの基本構成

時間 → →

信号名ごとに横軸で状態遷移を示す

CLK: ┐ ┌─┐ ┌─┐ ┌─┐ ┌─┐

┘ └─┘ └─┘ └─┘ └─┘

D: 1 0 1 1 0

Q: ┌───┐ ┌───┐

│ 1 │───│ 0 │───...

└───┘ └───┘

4. Dフリップフロップの動作例

状況:

- D入力: 1 → 0 → 1 → 1 → 0

- CLK立ち上がり時のみDの値をQに反映

解説:

| 時刻 | CLK(↑立ち上がり) | D | Q(出力) |

|---|---|---|---|

| 1 | ↑ | 1 | 1 |

| 2 | ↑ | 0 | 0 |

| 3 | ↑ | 1 | 1 |

| 4 | ↑ | 1 | 1 |

| 5 | ↑ | 0 | 0 |

5. シフトレジスタ(Shift Register)とは?

D-FFを直列につなぐことで、1クロックごとにデータを右にずらす回路。

構成:

D → [DFF1] → [DFF2] → [DFF3] → 出力

↑ ↑ ↑

Q1 (t) Q2(t) Q3(t)

クロックが立ち上がるたびに:

- Q1 ← D入力

- Q2 ← Q1(1クロック前)

- Q3 ← Q2(1クロック前)

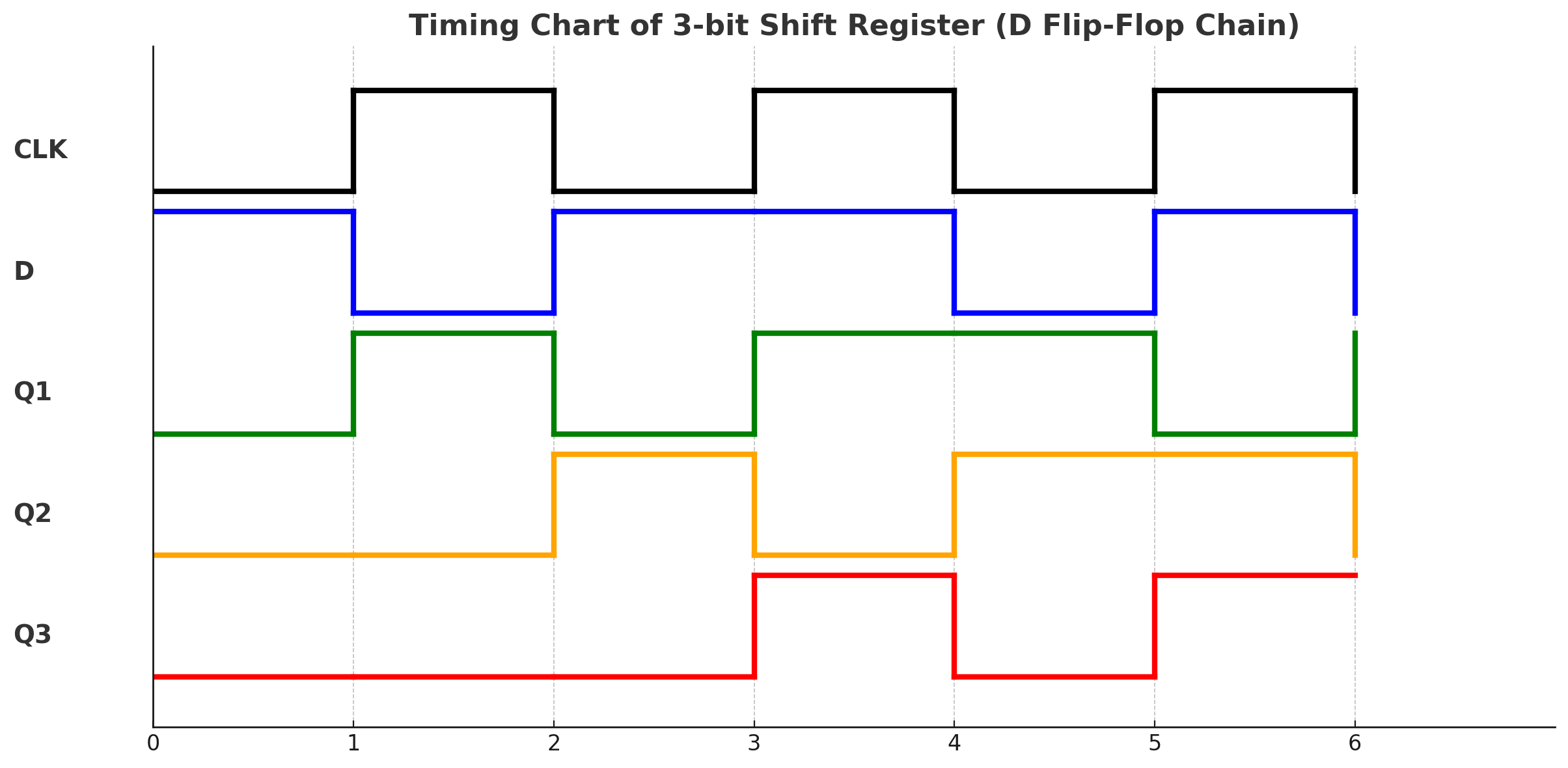

6. シフトレジスタのタイミングチャート例

D入力:

D: 1 0 1 1 0

タイミングチャート:

CLK: ┐ ┌─┐ ┌─┐ ┌─┐ ┌─┐ ┌─┐

┘ └─┘ └─┘ └─┘ └─┘ └─┘

D: 1 0 1 1 0

Q1: 1 0 1 1 0

Q2: - 1 0 1 1

Q3: - - 1 0 1

説明:

-

Q1:Dからの入力をそのまま受け取る -

Q2:Q1の1クロック前の値を保持 -

Q3:Q2のさらに1クロック前を保持

このように、D→Q1→Q2→Q3 と1ビットずつ右に「シフト」していく。

7. シフトレジスタの応用例

| 応用先 | 内容 |

|---|---|

| パラレル→シリアル変換 | ビット列を順に1本で出力 |

| データ遅延線 | 信号を1クロックずつ遅延させる(FIFO) |

| カウンタ制御 | シフトしながらビットの位置を管理 |

| CRC計算回路 | ビットシーケンスの整形やエラー検出に使用 |

8. まとめ

| 用語 | 説明 |

|---|---|

| タイミングチャート | デジタル信号の時間変化を示す図 |

| クロック信号 | 回路全体の動作を同期する矩形波 |

| Dフリップフロップ | D入力をクロック↑で記憶し、Q出力に反映する素子 |

| シフトレジスタ | 複数DFFを接続して、データを1クロックごとに送る回路 |