Float計算回路のVerilog実装

~ FPGA に載せたい ~

オレオレ実装なので間違っていても知りません

加算回路編

Float計算回路のVerilog-HDL実装について -その1

デバッグツール作成編

Float計算回路の(ry-その1.1(float値の16進数表記)

補足とLeadingZeros編

Float計算回路のVerilog-HDL実装について -その1.5 (LeadingZeros)

減算回路編

Float計算回路のVerilog-HDL実装について -その2(減算編)

回路共通化とタイミング調整編

Float計算回路のVerilog-HDL実装について -その2.1(加算回路の共通化とタイミング調整)

共通化編

Float計算回路のVerilog-HDL実装について -その2.5(共通化)

0対応編

Float計算回路のVerilog-HDL実装について -その2.7(0対応)

乗算回路編

Float計算回路のVerilog-HDL実装について -その3(積算回路)

目的

floatの勉強

float32のハードウェア実装

だいたい前回と一緒

0 に対応しない乗算回路の実装を行う

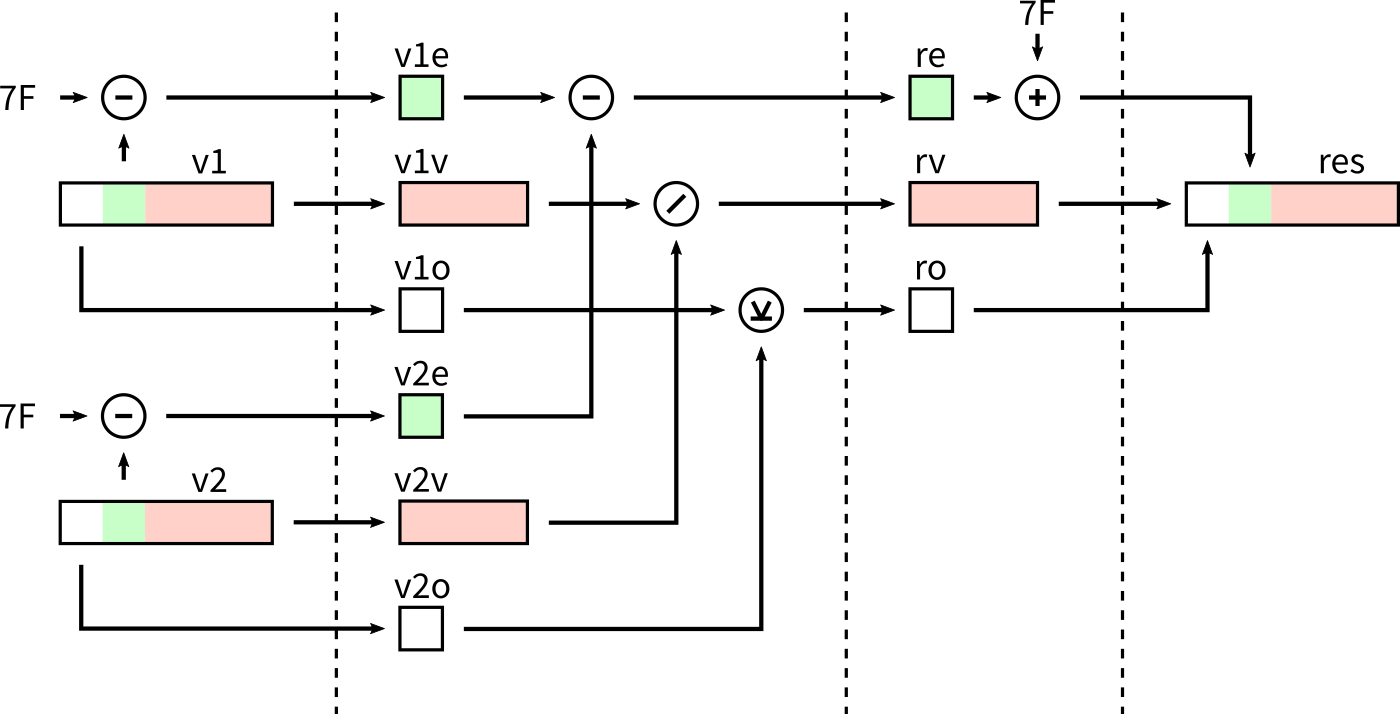

今回のHW

コード

module float_div(

input wire clk,

input wire [31:0] v1,

input wire [31:0] v2,

output wire [31:0] vres

);

assign vres = res;

// TIM1

reg [7:0] v1e;

reg [7:0] v2e;

reg [23:0] v1v;

reg [23:0] v2v;

reg v1o;

reg v2o;

// TIM2

reg [7:0] re;

reg [47:0] rv;

reg ro;

// TIM3

reg [31:0] res;

always @(posedge clk) begin

// TIM1

v1e <= (v1[30:23] - 8'h7F);

v2e <= (v2[30:23] - 8'h7F);

v1v <= {1'b1, v1[22:0]};

v2v <= {1'b1, v2[22:0]};

v1o <= v1[31];

v2o <= v2[31];

// TIM2

re <= v1e - v2e;

rv <= {v1v, 24'b0} / v2v;

ro <= v1o ^ v2o;

// TIM3

if (rv[24]) begin

res <= {ro, re + 8'h7F, rv[23:1]};

end else begin

res <= {ro, re + 8'h7E, rv[22:0]};

end

end

endmodule

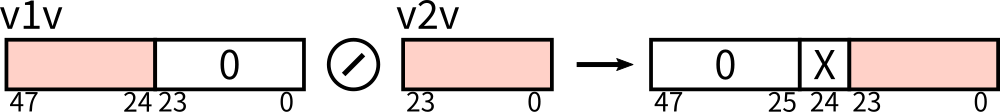

TIM2

v1v も v2v も最上位ビットが 1 であるため、

そのまま除算すると1桁しか答えが出ないので 0 で拡張する

逆に商は上位23ビットもしくは24ビットが 0 となる

シミュレーション結果と誤差

| 値1 | 値2 | 結果 | 正答 | |

|---|---|---|---|---|

| 123.4 | 7.25 | 17.020689 | 17.0206896… | |

| 7.25 | 123.4 | 0.058752023 | 0.0587520259… | |

| 123.4 | 0.725 | 170.20688 | 170.206896… | |

| 0.725 | 0.00123 | 589.43085 | 589.430894… |

ちょっとブレるけど誤差ということで・・・