Float計算回路のVerilog実装

~ FPGA に載せたい ~

オレオレ実装なので間違っていても知りません

加算回路編

Float計算回路のVerilog-HDL実装について -その1

デバッグツール作成編

Float計算回路の(ry-その1.1(float値の16進数表記)

補足とLeadingZeros編

Float計算回路のVerilog-HDL実装について -その1.5 (LeadingZeros)

減算回路編

Float計算回路のVerilog-HDL実装について -その2(減算編)

回路共通化とタイミング調整編

Float計算回路のVerilog-HDL実装について -その2.1(加算回路の共通化とタイミング調整)

目的

floatの勉強

float32のハードウェア実装

正負の加減算を均一にこなす加減算回路を作成する

今回は0を考慮しない

仕様

値計算方針

第2引数とオペレータの排他的論理和を獲り、第2引数の符号とする

すべての計算を加算表記とする

大きい値の符号を結果出力符号とする

まぁそうなるよね

加算と減算の判定は大きい値と小さい値の符号の排他的論理和とする

まぁそうなるよね

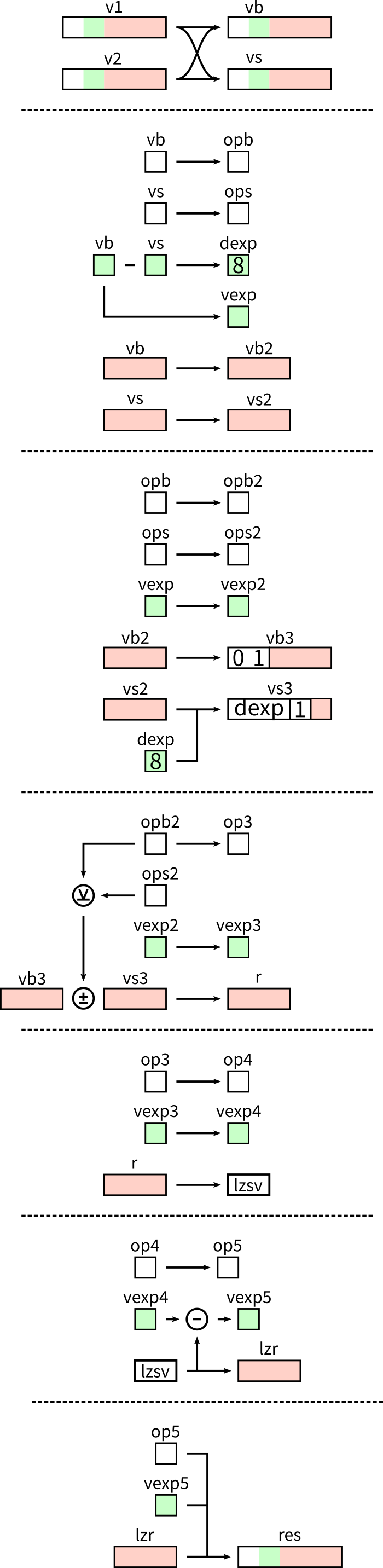

1. 値の比較

数値比較を行い, 大きい方を vb(value big), 小さい方を vs(value small)へ格納する.

加算回路と異なり、符号の話が関係するので完全に大小を分離したい.

//TIM1

reg [31:0] vb;

reg [31:0] vs;

always @(posedge clk) begin

if (v2[30:23] < v1[30:23]) begin

vb <= v1;

vs <= {v2[31] ^ op, v2[30:0]};

end else if (v1[30:23] < v2[30:23]) begin

vb <= {v2[31] ^ op, v2[30:0]};

vs <= v1;

end else if (v2[22:0] < v1[22:0]) begin

vb <= v1;

vs <= {v2[31] ^ op, v2[30:0]};

end else begin

vb <= {v2[31] ^ op, v2[30:0]};

vs <= v1;

end

end

第2引数の符号とオペレータの排他的論理和をとる( -(-v) の排除)

2, 3. 省略

符号が消されないように適宜保護する

4. 計算

//TIM4

reg [7:0] vexp3;

reg [24:0] r;

always @(posedge clk) begin

op3 <= opb2;

vexp3 <= vexp2;

if (opb2 ^ ops2) begin

r <= vb3 - vs3;

end else begin

r <= vb3 + vs3;

end

end

2値の符号が異なる場合は減算する(符号は大きい方を維持するから絶対値の計算だね)

5, 6. 省略

順当に作る(特にコメントなし)

シミュレーション結果

4302_A666 = 130.65

42E8_4CCD = 116.15

C2E8_4CCD = -116.17

C302_A666 = -130.65

|値1| 値2| 演算子|| 結果|

|:-:|:-:|:-:|:-:|:-:|:-:|

|123.4|7.25| +||130.65|

|123.4|-7.25| +||116.15|

|-123.4|7.25| +||-116.15|

|-123.4|-7.25| +||-130.65|

|||||||

|7.25|123.4| +||130.65|

|7.25|-123.4| +||-116.15|

|-7.25|123.4| +||116.15|

|-7.25|-123.4| +||-130.65|

|||||||

|123.4|7.25| -||116.15|

|123.4|-7.25| -||130.65|

|-123.4|7.25| -||-130.65|

|-123.4|-7.25| -||-116.15|

|||||||

|7.25|123.4| -||-116.15|

|7.25|-123.4| -||130.65|

|-7.25|123.4| -||-130.65|

|-7.25|-123.4| -||116.15|

あってるっぽい