140個のCLBで構成される.その中に5入力1出力のLUTを持つ.2つ組み合わせることで6入力2出力のLUTにできる.

それぞれのLUT5はD-FFを持つ.

CLBは外部出力用に用意されたIOB(140個)に囲まれている.

各CLBは8個のLUT5と,8個のD-FFを持つので,全部で1120個のLUT5を利用できる.

アーキテクチャ

140個のCLBは100個のロジック用CLB(CLBL)と,40個のメモリ用CLB(CLBM)で構成される.

R19DS0120EU0105 Rev 1.05 @ p.26

CLB

各CLBは4つのLUT6と8個のD-FFを持つ.

CLBの中では,Nビットのカウンタやアダーを効率よく実装できるよう,4つのLUT6と4ビットキャリーチェーンがグループになっている.

CLBの出力はクロススイッチで柔軟にルーティングできる.

ロジック用CLB(CLBL)はメモリ用CLB(CLBM)のサブセットである.CLBMだけが,Embedded Memory Mode(EMM)とShift Register Mode(SRM)という追加のモードを持っている.

シフトレジスタモード -Shift Register Mode-

CLBMがシフトレジスタモードのとき,シフトレジスタ幅を3つから選択できる.

- 4つの16ビットシフトレジスタ(SRL16E)

- 2つの32ビットシフトレジスタ(SRL32E)

- 1つの64ビットシフトレジスタ(SRL64E)

これらは, 5 kb 分散メモリの設定に含まれる.

組み込みメモリモード -Embedded Memory Mode-

CLBMがエンベデッドメモリモード(EMM)のとき,実装するメモリ要素の幅と深さを選択できる.

- 4つの32 x 1-bit memory array

- 2つの64 x 1-bit memory array

- 1つの128 x 1-bit memory array

R19DS0120EU0105 Rev 1.05 @ p.31

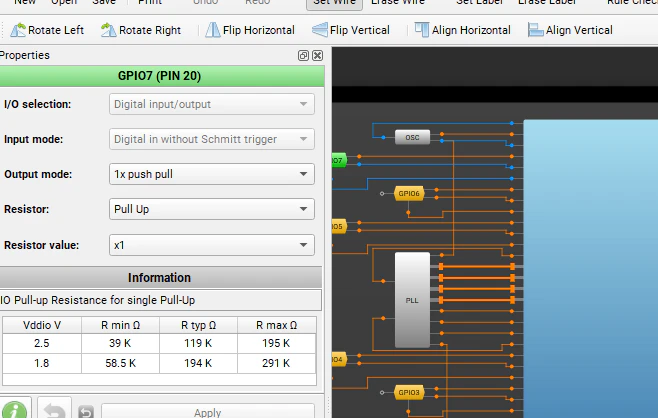

1:プルアップの設定 -Programmable Pull-Up Resistors-

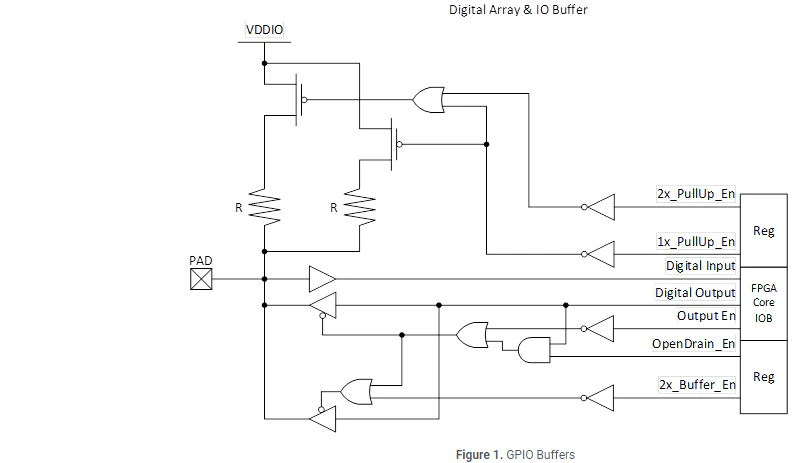

全てのI/Oピンは独立してプルアップ抵抗を設定できる.抵抗値はVDDIOの値によって決まる.

Go Configure Hubの設定画面を下に示す.

I/O selection:

グレーアウトしており設定できないが,ForgeFPGAのGPIOは,常に入力ポートとしても出力ポートとしても動作する.出力ポートとして動かす場合は, Output_En をHにすると,関連するスイッチがONになる.

Input mode:

グレーアウトしていて選択できない.常にDigital in without Schmitt triggerである.

Output mode:

次の4つから選択できる.

- 1× push pull

- 2x push pull

- 1x open drain

- 2x open drain

Resistor:

どちらかを選択する.

- Pull Up

- Hi-Z

(Shrike Liteボードでは,GPIO17などは,RP2040にも繋がっているため,Pull Upに設定しても,プルアップされないようである.orz)

2:内蔵オシレータ -On-Chip OSC-

概要

オンチップで50 MHzのオシレータを持っている.

OSC_EN信号が“H”になると,OSC_CLK信号を受信するまでにディレイがある.これによって出力からグリッジが取り除かれる.

OSC_CLK と OSC_READY はFPGA Core IOBに直接接続されている.

-Signal Descriptions-

制御入力と制御出力はFPGAコアから派生している.

OSC _EN

OSCの有効信号.アクティブHighであり,OSCを有効にする信号である.

OSC_CLK

バッファされたOSCクロック.オシレータクロックは,FPGAコアのグローバルクロックまたは,PLLのクロック入力ソースに送信できる.

OSC_READY

オシレータの周波数が安定したとき,1になる.

この信号はFPGAコアに接続されている.

R19DS0120EU0105 Rev 1.05 @ p.35

3:PLL

概要

レファレンスクロックは次のどちらかである(PLL_REF_CLK_SELで選択).

- オンチップのOSC(REF_CLK_OSC)

- 外部クロック(REF_CLK_EXT,GPIO2ピン経由で入れる)

注:分子および分母に大きな数値を指定すると,クロックジッタが減る代わりに,消費電流が増加する.

PLLを正しく動作させるために,入出力するクロックは幾つかの条件を満たす必要がある.

レファレンスクロック

入力するレファレンスクロックは,安定した単一周波数であり,指定された周波数レンジ内に収まっている必要がある.

PLLロック出力 PLL_LOCK

PLL_CLK は,PLL仕様に記載されている周波数レンジに収まっている必要がある.出力周波数が安定すると,PLL_LOCK がアサートされる.

VCOとPFD周波数

VCOおよびPFDの周波数は,PLL仕様で指定された周波数レンジ内に収まっている必要がある.

R19DS0120EU0105 Rev 1.05 @ p.36

信号の詳細 -Signal Descriptions-

クロックと制御入力信号によって,入力クロックソースと出力周波数が決定される.

PLL_REF_CLK_SEL(入力)

クロックソースとして,オンチップOSCまたは外部クロック(GPIO2経由)を選択する.LOWの場合,PLLへのクロック入力はオンチップOSCになる.

PLL_BYPASS(入力)

クロックソースと,PLL_CLK間の接続を有効にする.アクティブHigh.

PLL_REFDIV [5:0] (入力)

レファレンスクロックの分周値の設定.1~63から選択する.

PLL_FBDIV [11:0] (入力)

フィードバック分周値の設定.16~400から選択する.

PLL_POSTDIV1[2:0] および PLL_POSTDIV2[2:0] (入力)

2段のポスト分周器は,PLL_FOUTクロック出力の前にVCO周波数を分周するために使用される.各ポスト分周器には,1~7の分周オプションがある.ポスト分周比の合計は,PLL_POSTDIV1 × PLL_POSTDIV2

注:PLLに複数のポスト分周器が直列に接続されている場合,2番目のポスト分周器を有効にする前に,最初のポスト分周器を最大値に設定する必要がある.

4で割る場合の設定値を次に示す.

- 推奨:PLL_POSTDIV1 = 4,PLL_POSTDIV2 = 1

- 推奨されないが許容される:PLL_POSTDIV1 = 2,PLL_POSTDIV2 = 2

- 許容されない:PLL_POSTDIV1 = 1,PLL_POSTDIV2 = 4

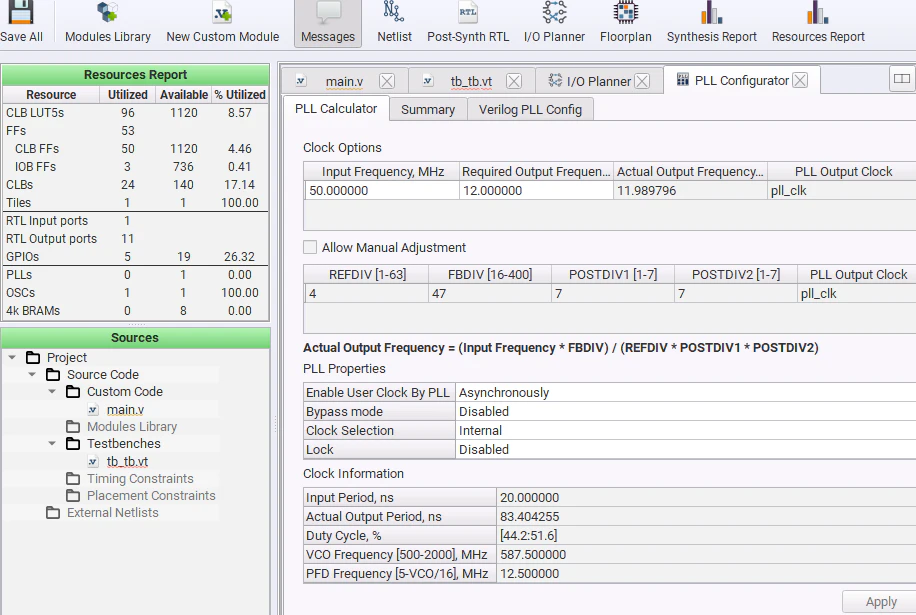

Go Configure Hubの PLL Calculator 機能を使用して,上記パラメータを変更し,出力周波数値を調整できる.

電源入力によってPLLの現在の電源状態が決まる.

- PLL_EN(入力)

PLLを有効にするイネーブル信号.アクティブHIGH. - PLL_CLK(出力)

出力クロック(PLLのロック状態による). - PLL_LOCK(出力)

PLLのロック状態を表す信号.PLLの出力周波数が安定すると,HIGHになる.

これは,フィードバッククロックと位相周波数検出器(PFRD)間のサイクルスリップが256サイクル連続して発生していないことを示す.

PLLの全ての信号は,専用のFPGAコアIOBに接続される.

Go Configure Hubで設定

所望の出力周波数を得るために,Go Configure Hubでパラメータを設定できる.メニューから[FPGA Editor] → [PLL Configurator]をクリックすると設定画面が開く.

PLL Calculatorタブ

パラメータの設定や,Verilogテンプレート,I/Oプランナー,レジスタへの割り当てを行える.

複数の出力を持つデバイスの場合は,右側にあるチェックボックスで出力先を選択する.

次の計算モードがある.

- ディバイダ自動計算

入力周波数と出力周波数のパラメータを設定し,ディバイダのパラメータ(REFDIV,FBDIV,POSTDIV1,POSTDIV2)を得る. - ディバイダ手動調整

Allow Manual Adjustment のチェックボックスをチェックする.

入力周波数と4つのディバイダに対するパラメータを全て入力して,所望の出力周波数にする.

プロパティテーブルでパラメータを設定し,[Apply]ボタンをクリックしてデータをレジスタに渡す.[Apply]ボタンは各PLLごとに変更を保存する.[Apply]ボタンによってPLLの配線が自動的にFPGAコアに接続される(信号名はデフォルト名を使用する).これはI/Oプランナーの画面で確認できる.

接続される配線を1タッチで解除する方法がない.PLLの使用をやめる場合は,I/Oプランナーの画面を開き手動で接続を外す.

※ メニューから[Options]-[Settings]をクリックすると,変更を保存する前の確認ウィンドウの挙動を変更できる.

PLLのデータは,コンポーネントのプロパティパネルでも設定できる.どちらで設定しても,設定値は同期される.

R19US0007EU0202 Rev.2.02 @ p.34

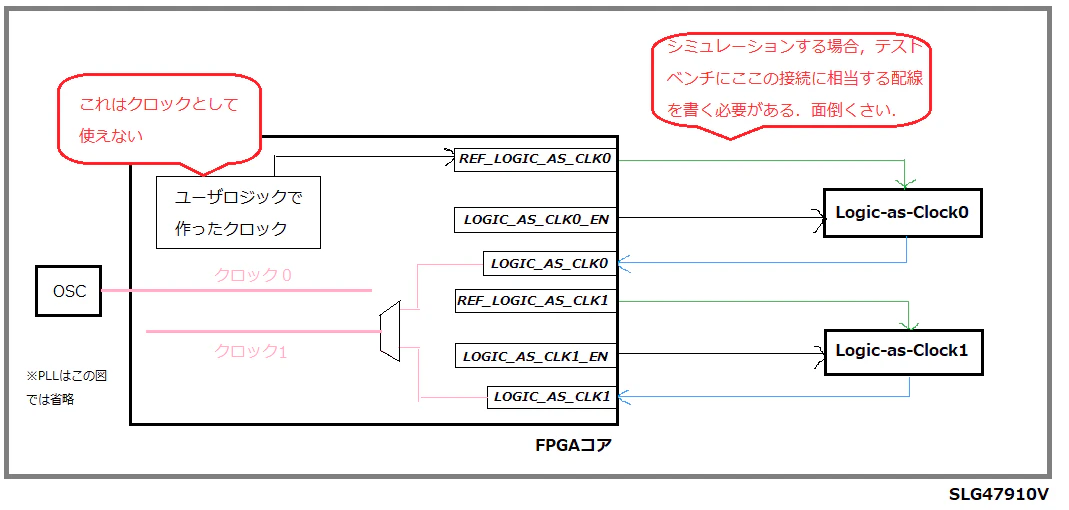

4:Logic as Clock

ForgeFPGAでは,reg や wire の信号をクロックとして使おうとすると,P&Rでエラーになる(センシティビティリストに入れると合成時にエラーになる).

ユーザロジックをクロック信号として利用するためには,Logic-as-Clockという機能を使う.クロックとして使用したい信号は,Logic-IOB( REF_LOGIC_AS_CLK0 / REF_LOGIC_AS_CLK1 )を通じてFPGAコアから出力し,その信号をIOB( LOGIC_AS_CLK0 / LOGIC_AS_CLK1 )を介してFPGAコアへループバックさせる(FPGAコアファブリックの外にあるLaC回路を通す).

FPGAコアの外には2つのLaC回路がある(LaC0とLaC1).

このLogic-as-Clock 回路を有効にするには, LOGIC_AS_CLK0_EN (もしくは LOGIC_AS_CLK1_EN )をHにする.Logic-as-Clock を使って,ロジック信号をクロック信号として使うときに,その信号源は2つ考えられる.

1:内部で生成した信号源

LaC回路へ入力するクロック信号として,FPGAコア内で生成した信号を使う.例えば,OSCクロックをカウンタで分周した信号などである.

後述する例では,FPGAコア内でカウンタを使い,1KHzのクロック clk_1k を作っている.これをそのままクロックとして利用することはできないので,LaC回路を経由させるわけである.

2:外部から入れた源振

外部クロックを任意のGPIOを通してFPGAコアに入力し,ロジック回路では何も処理せずにIOB出力する.入力信号と出力信号をAssignでつなぐだけであり,非同期になる.

その信号をLaC経路を通して再びFPGAコアにループバックすることでクロックとして利用できる.

注意:FPGAコアが持つクロックツリーは2つである.OSCまたはPLLを使用する場合は,LaC経由のクロックは1つだけ使用できる.OSCとLaC,またはPLLとLaCなど.OSCとPLLを使う場合は,LaCは使用できないと思われる.

R19DS0120EU0105 Rev 1.05 @ p.38

ロジック信号をクロック信号にする例

LaC機能をONにする

LaC機能を有効にするには,LOGIC_AS_CLK0_EN を1にする.

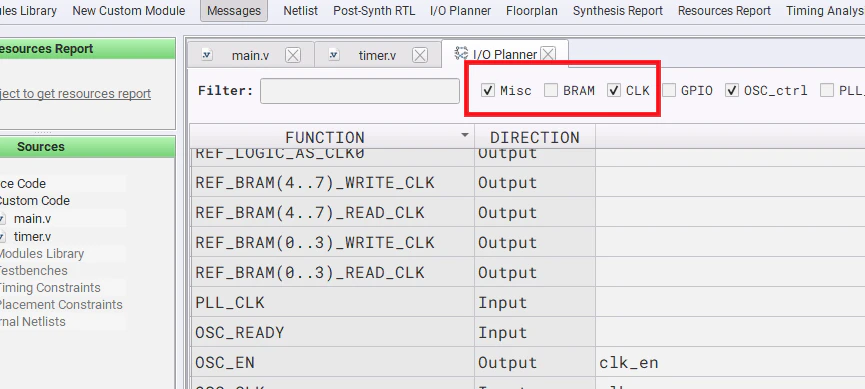

具体的には事前に,Verilogコードで適当なWireを作っておき,I/Oプランナーでその信号をLOGIC_AS_CLK0_ENに割り当てる(下図の通り,チェックボックスをチェックすると,関係する信号が表示される).

チェックボックスをチェックして所望の信号をリストに表示させる

ポートの割り当て:クロックにする信号を出力

クロックとして使用する信号を,IOB(REF_LOGIC_AS_CLK0/1)を通して出力する.

下図では, clk_1k を出力している.

ポートの割り当て:ループバックを入力

IOB(LOGIC_AS_CLK0/1)を通してFPGAコアに入力する.

これを受ける信号は,Verilogコードの中で宣言しておく.信号名が clk0 であれば次のようにする.

(* iopad_external_pin, clkbuf_inhibit *) input wire clk0,

clkbuf_inhibit を付けないと,クロックと認識されないようで,合成時にWarningが出るうえ,LaC回路からのループバック信号が接続されないようである.

I/O Plannerは下図のようになる.

参考文献

(1)FPGA.tokyo

https://fpga.tokyo/vicharak-shrike-lite/