所感

FPGAとマイコンを1ボードに搭載

Shrike LiteはマイコンとFPGAが搭載されたボードであり,

マイコンはRP2040(Raspberry Pi財団)が,FPGAはForgeFPGA SLG47910V(Renesas)が搭載されている.

ちなみにRP2350を搭載するボードも開発中(こちらは名称にLiteが付かないみたい)のようである.

筆者はFPGA側を使いたいので,その前提での解説になるが,コンフィグはRP2040で行うようなので,どのみちMCU側も触る必要がある.公式ドキュメントでは,MCU側のソフトウェアはMicroPythonか,Arduinoか,ラズベリーパイC SDKを使うことになっている.

RP2040なのでMicroPythonも

FPGAとはあまり関係ないだろうが,ボードとしてはRP2040が載っているので,Raspberry Pi Pico同様に,MicroPythonを使った開発もサポートしているようである.(OSからドライブとして認識する.MicroPython実行環境をインストール後は,Pythonファイルをドラッグアンドドロップするだけで,起動すると思われ)

開発環境

公式のドキュメントを見ると,それぞれ次の開発環境(IDE)が必要になる.

- ForgeFPGA:Go Configure Software Hub

- RP2040:Thonny IDE

ただし,RP2040用の開発環境については,公式サイトのドキュメントでもThonny IDE以外が使われている部分もある.(おそらくMicro Pythonとの組み合わせでThonny IDEを推奨していると思われる)

本稿では,RP2040用としては,Thonny IDEではなくArduino IDEを使う.

それぞれ取得してインストールする.

Shrike Liteでは電源ON時に,RP2040がForgeFPGAを設定(コンフィグレーション)する.

ビットストリームもRP2040のファームウェアも,ボード上のフラッシュ・メモリ25Q32(winbond)に書き込んでおく.FPGAはリセット後(PoR)SPIスレーブモードになり,RP2040からSPIでコンフィグレーションされる.

ForgeFPGA SLG47910のコンフィグについて

以下,SLG47910 Datasheetより抜粋

コンフィギュレーションは3モードある

- 外部SPIフラッシュ(SPIマスタ・モード)

- MCUホスト(SPIスレーブ・モード)

- 内部1タイム・メモリ(OTPモード)

SLG47910はビットストリームの保存に,384kビットを必要とするので,外部SPIフラッシュの使用が推奨されているようだ.

Shrike Liteでは,SPIスレーブ・モードになっており,RP2040がMCUになる.コンフィグ関係のGPIO3,GPIO4,GPIO5,GPIO6はRP2040に接続されており,ボードのヘッダには出ていないので,OTP以外ではこのボードはRP2040からしかコンフィグできない.

と,思いきやボード上にパッドがある!

基板上にパッドがある

シルク印刷をよく見ると,上からCLK,SS,SI,SOと書いてある.

基板上のパターンをたどると,これらの信号は次の通りである.

- GPIO3/SPI_CLK General Purpose IO or SPI Serial Clock

- GPIO4/SPI_SS General Purpose IO or SPI Slave Select

- GPIO5/SPI_SI General Purpose IO or SPI Serial Input

- GPIO6/SPI_SO General Purpose IO or SPI Serial Output/Config

Pin Information @ R19DS0120EU0105 Rev 1.05 p.9

コンフィグレーション・シーケンス

電源起動(PoR)後に,nRSTが1になるとコンフィグレーション・モードに入り,次のシーケンスでコンフィグされる.

-

Force load form OTPレジスタがEnableなら OTP から -

SPI_nSS(GPIO4) がHなら SPIマスタになり外部SPIフラッシュ から - MCUから

コンフィグレーションされると FPGA_CORE_READY が H になる.

FPGA_CORE_READY は FUNC_MODE に入る前に H になるので,ユーザロジックのリセット信号として利用できる.

Configuration Mode(コンフィグレーション・モード)が正常に完了すると, Functional Mode に入る.

ForgeFPGA SLG47910の電源について

以下,SLG47910 Datasheetより抜粋

次のnSLEEP信号によってリテンション・モード(スリープ)に移行する.

- nSLEEP signal source registe = 0の場合:EN = 0

- nSLEEP signal source registe = 1の場合:INT_FPGA_SLEEP = 1

リテンション・モードでは,ユーザ・ロジックは停止されクロックはFPGAコアに供給されない.OSCとPLLもOFFになる.

FPGAコアとBRAMの内容は保持される.GPIOはリテンション・モードへの移行前の状態を保持する.

nSLEEP signal source register の値に関係なく,ENピンの立ち上がりが検出されると再びFUNCTIONALモードに戻る.

このときコンフィグレーションは不要で,FPGAコアおよびBRAMの内部状態は復元される.ユーザ・ロジックも引き続き動作する.EN (nSLEEP)の最低パルス期間は,FUNCTIONALモードでOSCがONの場合は45µsで,OSCがOFFの場合は300µsである.

Shrike LiteではENピンはRP2040のGPIO 13に接続されているようである.これはボードのピンヘッダには引き出されていないため,RP2040のソフトウェアから制御するしかない.

ForgeFPGAのI/Oバッファ

各GPIOは4つのレジスタを持っている(2x_PullUp_En,1x_PullUp_En,OpenDrain_En,2x_Buffer_En).

各GPIOピンは次のどれかに設定される.

- 入力

- 出力,1x Drive Push-pull

- 出力,2x Drive Push-pull

- 出力,1x Drive Open-drain

- 出力,2x Drive Open-drain

GPIOの入出力はRTLコードから動的に変更できる.

出力設定(push-pull か Open Drain)とプルアップ設定(Pull_Up か Hi-Z)はコンフィグレーションされた後に動的変更できない.

開発環境1:RP2040の開発に使うArduino IDE

開発環境の準備

準備1:RP2040用ライブラリ追加

Arduino IDEをインストールしたら,メニューの「File」-「Preference」で設定ダイアログを開き,Additional Board Managerに次のURLを追加する.

https://github.com/earlephilhower/arduino-pico/releases/download/global/package_rp2040_index.json

そして,「Tool」-「Board」-「BoardManager」をクリックし,Raspberry Pi Pico/RP2040/RP2350をインストールする.

ライブラリインストールでタイムアウトの問題が発生する場合は ここを参照

準備2:ビットストリーム保存用ライブラリLittleFS追加

ビットストリームをボード上のフラッシュ・メモリに転送するために,LittleFSというライブラリを利用する.

https://github.com/earlephilhower/arduino-pico-littlefs-plugin/releases/

からZipファイルをダウンロードし,Arduino IDEに登録する

Arduino IDEのメニューにある 「Add .zip library」 では登録できない.しかも,Arduino IDEのバージョン1と2では,PicoLittleFSの登録方法が違うらしい

Arduino IDE2系の場合,LittleFSは ここからVSIXファイル をダウンロードする(1系でも出来そうだが試してない).

Arduinoのプラグイン置き場は,Windowsの場合,デフォルトならこの辺り..arduinoIDE\に Plugins フォルダがなければ作る.

C:\Users\<username>\.arduinoIDE\

ダウンロードしたVSIXファイルを, Plugins に設置する.

インストールできたか確認

Arduino IDEを再起動し,次の通り,Little FSのメニューが表示されることを確認する.

「Ctrl] + [Shift] + [P」を押して開くコマンド・パレットの中に Upload Little FS to Pico/ESP8266/ESP32 が表示されればOK(後ほど,このコマンドを使ってビットストリームを転送する)

準備3:Shrikeライブラリ追加

Arduino IDEの LIBRALY MANAGERで Shrike を検索し,表示されるものをインストールする.

Shrike Flash Library というものも表示されるが,ここではインストールしない.

動かす手順

手順1:Arduinoプロジェクトを作る

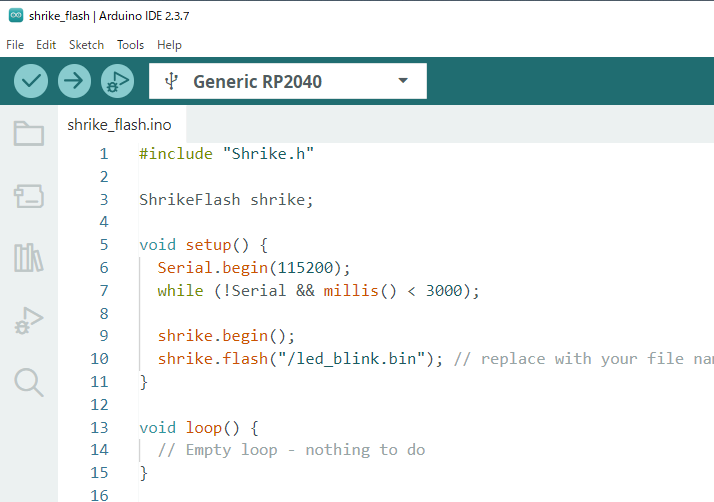

メニューから「File」-「Examples」-「Shrike」-「Shrike Flash」をクリックすると,exampleプロジェクトShrike Flashが開くので,「File」-「Save」とクリックし,任意の場所に保存する.

手順2:ビットストリームの設置と転送

上記で保存したプロジェクトのフォルダの中に, data というフォルダを作り,ビットストリームを配置する.

Shrike Liteボード上にあるBootボタンを押したままUSBケーブルでボードをPCに接続する.

この状態で,Ctrl+Shift+Pを押し,コマンドパレットを開く

ここで,Upload:LittleFS to Pico/ESP8226/ESP32 を実行することで, data フォルダに入れておいたビットストリームがShrike Liteに書き込まれる.

差し当って,公式から提供されている led_blink.bin を試すのがよい(ボード上の青LEDが点滅する).

独自のビットストリームを生成する方法は,本稿後半で触れる.

手順3:RP2040ファームウェア書き込み

Shrike Lite上のForgeFPGAは,SPIスレーブモード(MCUモード)でコンフィグされるようにRP2040に接続されている.従って,ForgeFPGAをコンフィグレーションするファームウェアをRP2040に書き込む必要がある.

そのためのCソースコード(プログラム)は,Shrike flash プロジェクトを開いた段階で既に設定されているので,コンパイルするだけである(プログラム中にビットストリームのファイル名がハードコートされているので,正しいファイル名に適宜変更する).

ボードに書き込む前に,Arduino IDEの「Tool」メニューからBoardをGeneric RP2040に設定する.すると,自動で次の項目が設定される.

- Flash Size:4MB(Sketch:2MB,FS:2MB)

- CPU Speed:133Mhz

Cソースコードの内容は,ほぼExampleのShrike flashのままでよいが,ビットストリームのファイル名は,実際に使うものに合わせて編集する( shrike.flash() 関数の引数 )

「→」書き込みボタンを押してコンパイルおよびファームウェアを書き込む

これで,転送しておいたビットストリームでFPGAがコンフィグされ,動作するようになる.

RP2040のファームウェアにはUARTが仕込まれており,ファームウェアの起動からコンフィグまでの各フェーズでメッセージが出るので,うまく動かない場合はUARTメッセージで状況を確認できる.

開発環境2:FPGAデザインの開発用Go Configure Software Hub

独自のデザインをFPGAで動かすためには,ルネサス純正の開発環境Go Configure を使う.

ダウンロードにはアカウント登録が必要

https://www.renesas.com/ja/software-tool/go-configure-software-hub#downloads

Go Configure Software HubはForgeFPGA用に,ルネサスから無償で提供されている開発環境

Debina,Ubuntu,Windows,MacOS用が用意されている.

開発の流れ

ForgeFPGAを動かすには,動作を示すビット・ストリームを作りボードに書き込む.

開発ツールを準備できたら,開発環境上(Go Configure)で所望のデザインを作り,それをツールの機能を使って合成する.次にツールの機能で配置配線を行う.

そして,出来上がったビット・ストリームをボードに書き込む

まずLチカしてみる

まず,一連の手順を確かめるために,Lチカのデザインを作る.

Go Configure Hubを起動したら,ウィンドウ左側から「Develop」-「Forge FPGA」をクリック

一覧表からSLG47910をダブルクリック

(新規でプロジェクトを作る代わりに,画面右下のフォルダボタンをクリックし,GitHubリポジトリにあるled blinkプロジェクトを開くだけでもよい)

ダイアログが開いたら,プロジェクト名と保存場所を入力する

「Properties」ボタンをクリックするとチップの設定を変更できる.次の通り設定する.

(「Properties」ボタンをクリックしなくても,新規プロジェクトの場合,自動でポップアップする)

RTL入力

画面中央にある「FPGA Core」と書かれた青い四角をダブルクリックすると,デザインの入力ウィンドウが出る(Verilogコードを入力できる)

対応言語は, Verilog 2005 (IEEE Standard 1364-2005)

2.5.4 Writing Verilog code @ Go Configure™ Software Hub User Guide v.2.12.0, p.163

エディタのLinterは,Verilator v5.034互換らしい.

packed / unpacked に関わらず多次元の定義はできない模様… (初期化の記述方法に制約あり)

識別子の先頭文字として _ は使えない…

main.v にコードを入力したら,画面左下の「Synthesize」ボタンをクリックすると合成される

今回は,公式の example に含まれるLチカのデザインを入力した.

配置配線

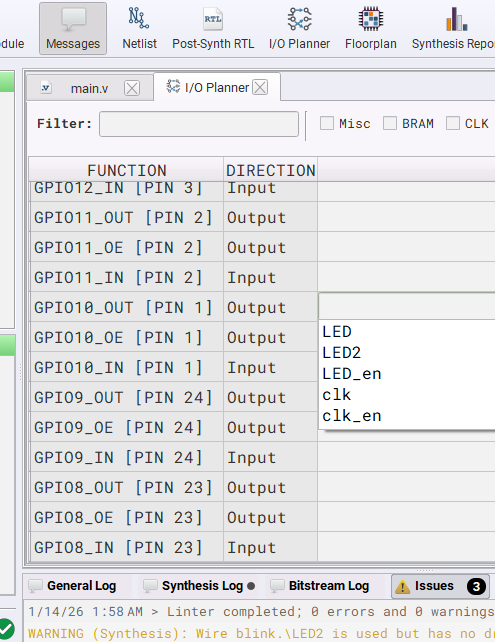

物理制約を設定するために,「I/O Planner」ボタンをクリックする

トップモジュールに設定したI/Oポートを物理的なピンに割り当てる.

このためのGUIツールが用意されており,所望の物理ピンに対応するコンボボックスで,Verilog上のピン名を選ぶだけである.Synthesizeすることで,自動でVerilog上で定義されたI/Oポートがコンボボックスに表示される.便利.

Lチカのデザインでは次の通り設定する.( FUNCTION にFPGAチップのピンがリストアップされている. PORT にはVerilog上で定義したI/Oポートが表示されている)

(この写真では見切れているが,OSC_CLK Input に clk を割り当てる)

Lチカのデザインとは関係ないが,参考として元のRTLコードに対して,LED2 を足したVerilogコードを次に示す(合成系はYosysらしい,未確認だが通常のYosysで合成したネットリストもForgeFPGAで使えるらしい).

これをSynthesizeしてI/O Plannerを開くと,コンボボックスに LED2 が追加されている.

話をLチカのデザインに戻す.I/Oを全て設定したら左下の「Generate Bitstream」ボタンをクリックする.

ビットストリームのファイル名は,

FPGA_bitstream_MCU.bin

として出力される.

出来たビットストームファイルを,前述の通り data フォルダに設置し,Little FSでボードに転送する.

このデザインでは,ボード上の青いLEDが1秒間隔で点滅する.

公式リポジトリには,Lチカ以外にも,Exampleデザインが色々と揃っている.

Go Configure Hub では一応シミュレーションもできます.

◇参考文献◇

(1)Shrike FPGA Bitstream Generation Guide

https://vicharak-in.github.io/shrike/generating_your_first_bitstream.html

(2)SLG47910(データシート)

https://www.renesas.com/en/products/slg47910

(3)写真

https://fpga.tokyo/vicharak-shrike-lite/

(4)公式リポジトリ

https://github.com/vicharak-in/shrike/tree/main/examples

(5)Verilog Style Guide for Shrike

https://vicharak-in.github.io/shrike/verilog_style_guide.html

(6)Schematics

https://github.com/vicharak-in/shrike/blob/main/hardware/shrike-lite_schematic.pdf