FPGAに再入門しようと思いたちFPGAプログラミング大全Xilinx編第2版を頭からやっていく7日目

時期的にも良いので一人Advent Calendarで25日続ける

最終的に作ったCPUを使えるようにFPGAプログラミング大全Xilinx編第2版第6章をやってCPU+FPGAシステムに慣れる

25日終了時の目標

4004等の実CPUの実装

目次

| # | タイトル |

|---|---|

| 01 | ツール導入 |

| 02 | 実機テスト下準備 |

| 03 | 実機テスト |

| 04 | クロック利用 |

| 05 | シミュレーション検証 |

| 06 | TD4 |

| 07 | TD4とりあえず実装 |

| 07 | TD4メモリ実装 |

| 09 | TD4完成 |

| 10 | 第6章1 |

| 12 | 未定 |

環境

【実装ボード】 Digilent Artix-7 35T Arty FPGA 評価キット

【OS】 Windows10

【IDE】 Vivado 2022.2

今日のゴール

第6章1を終わらせる

前準備

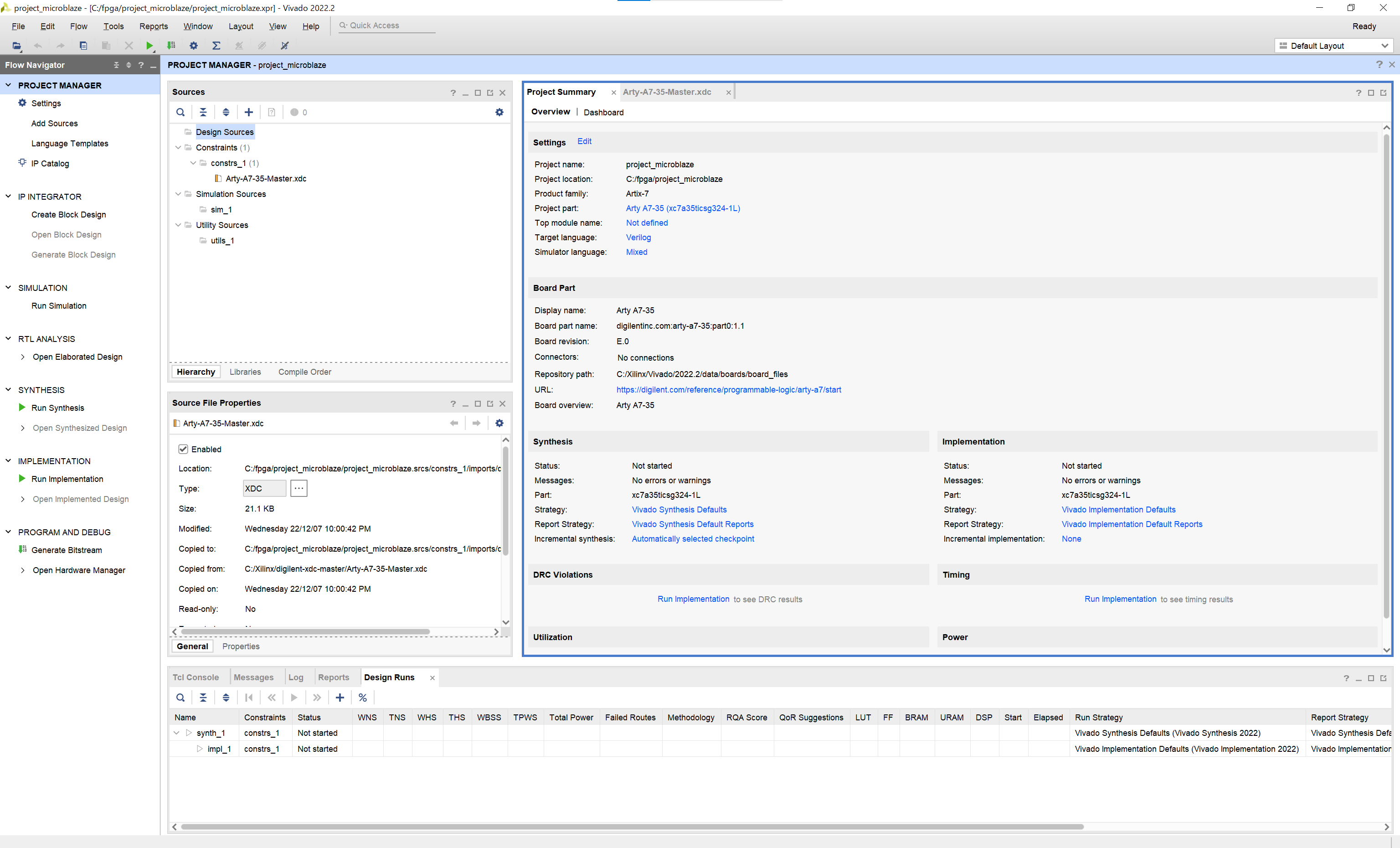

新しいプロジェクトを作る

XDC(制約ファイル)までを取り込み終わったところ

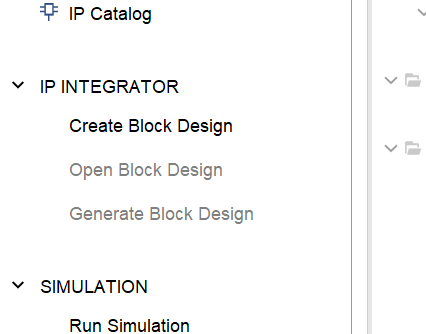

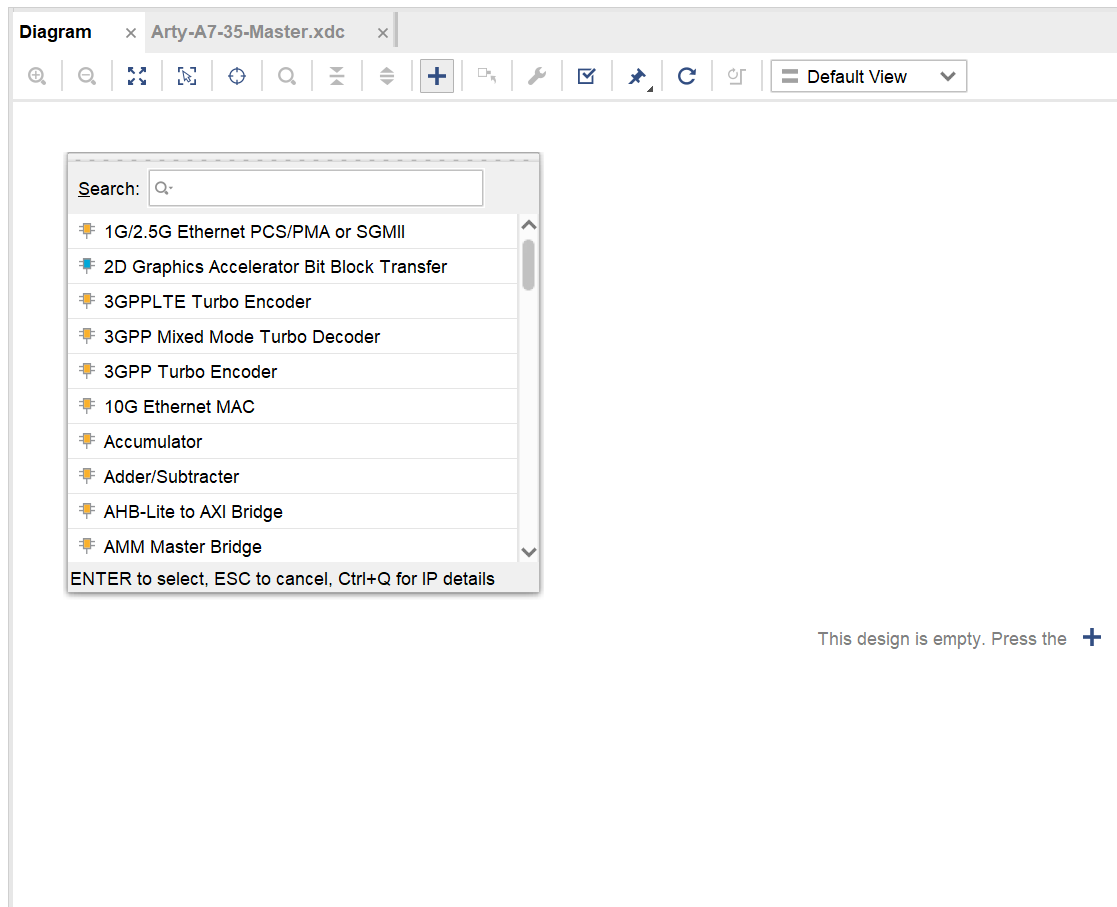

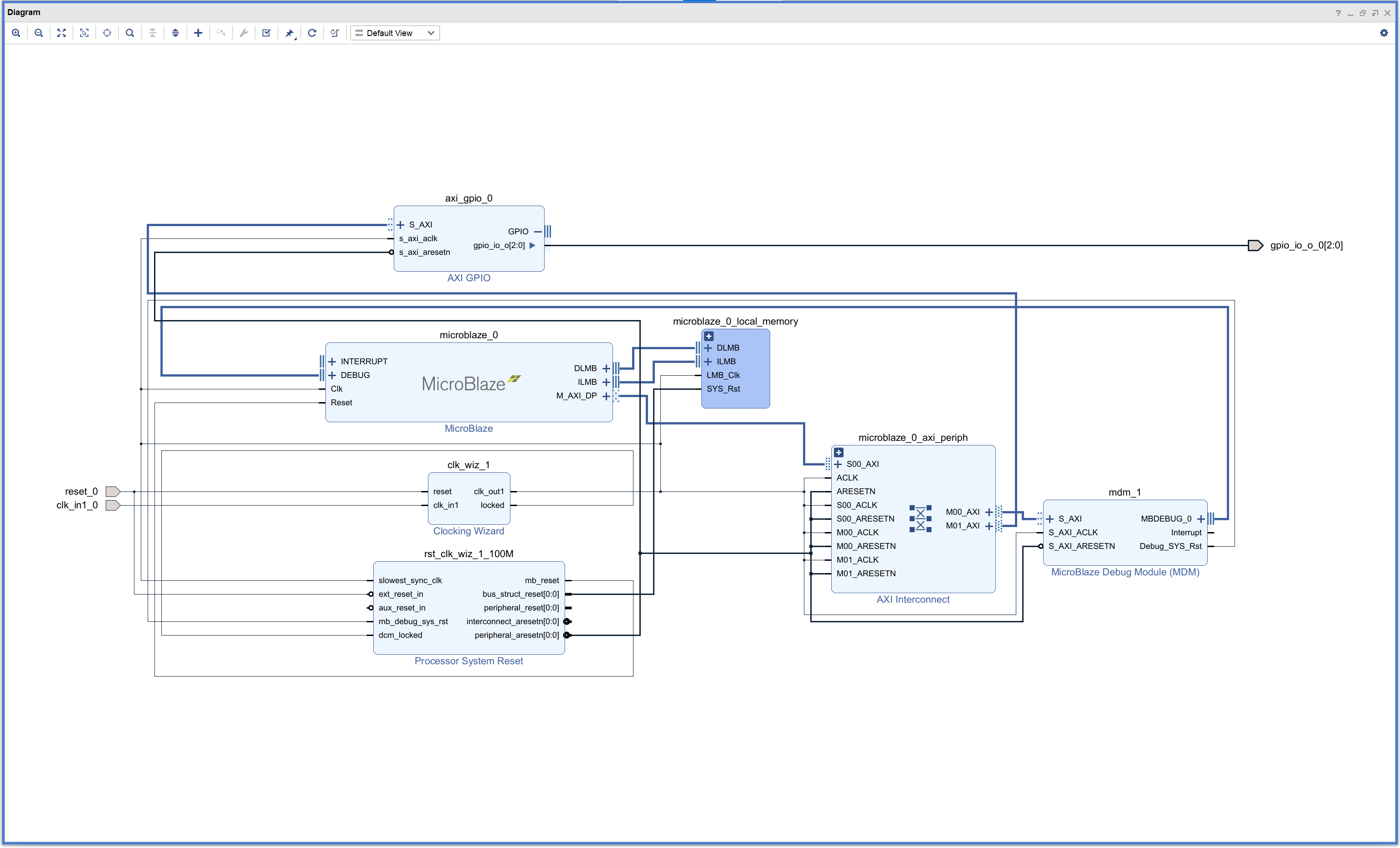

IPインテグレート

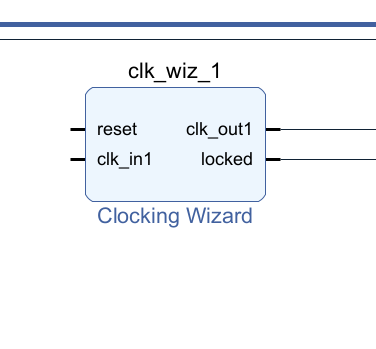

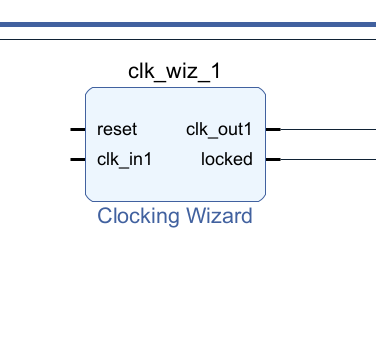

-

デフォルト設定で作成

-

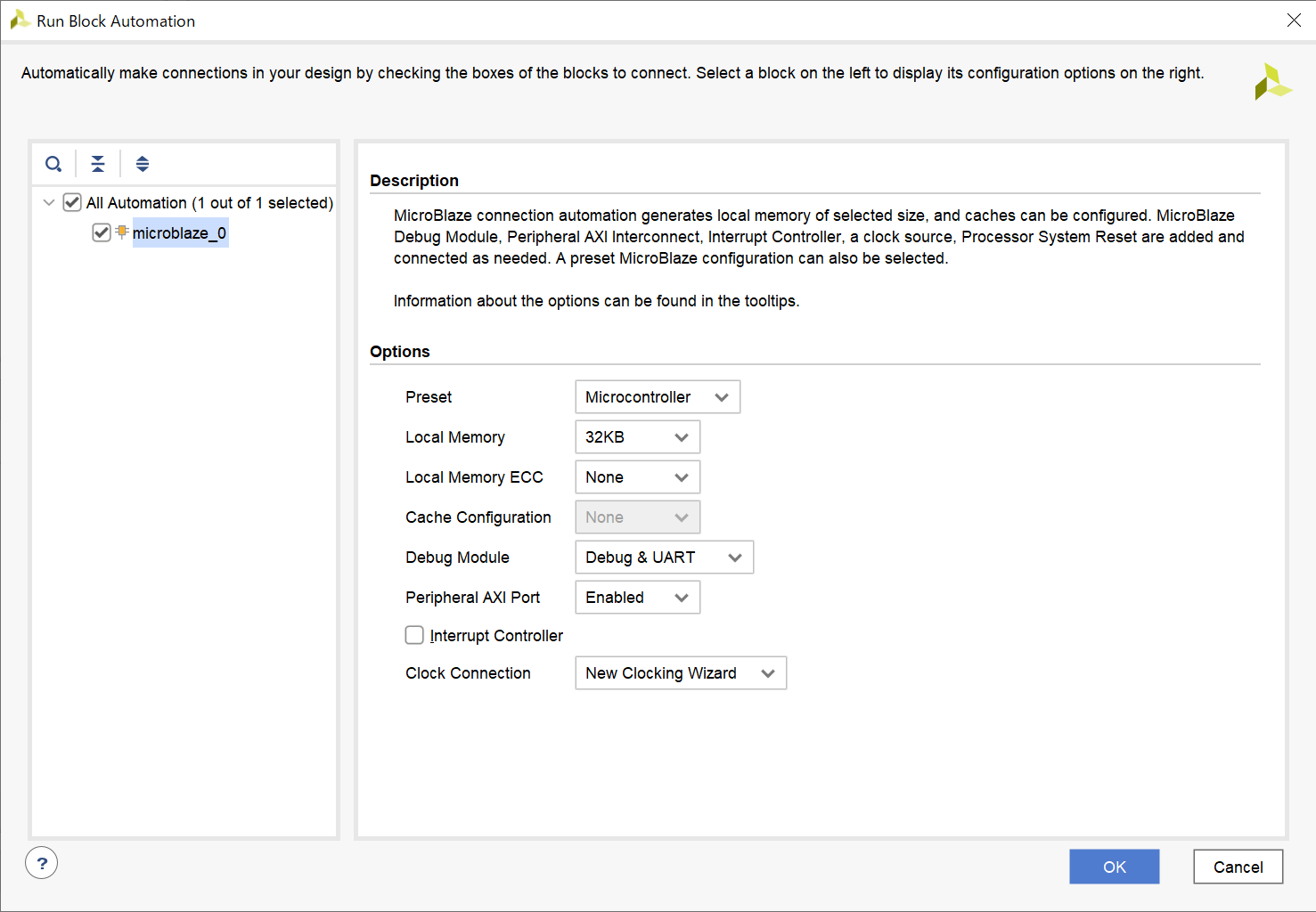

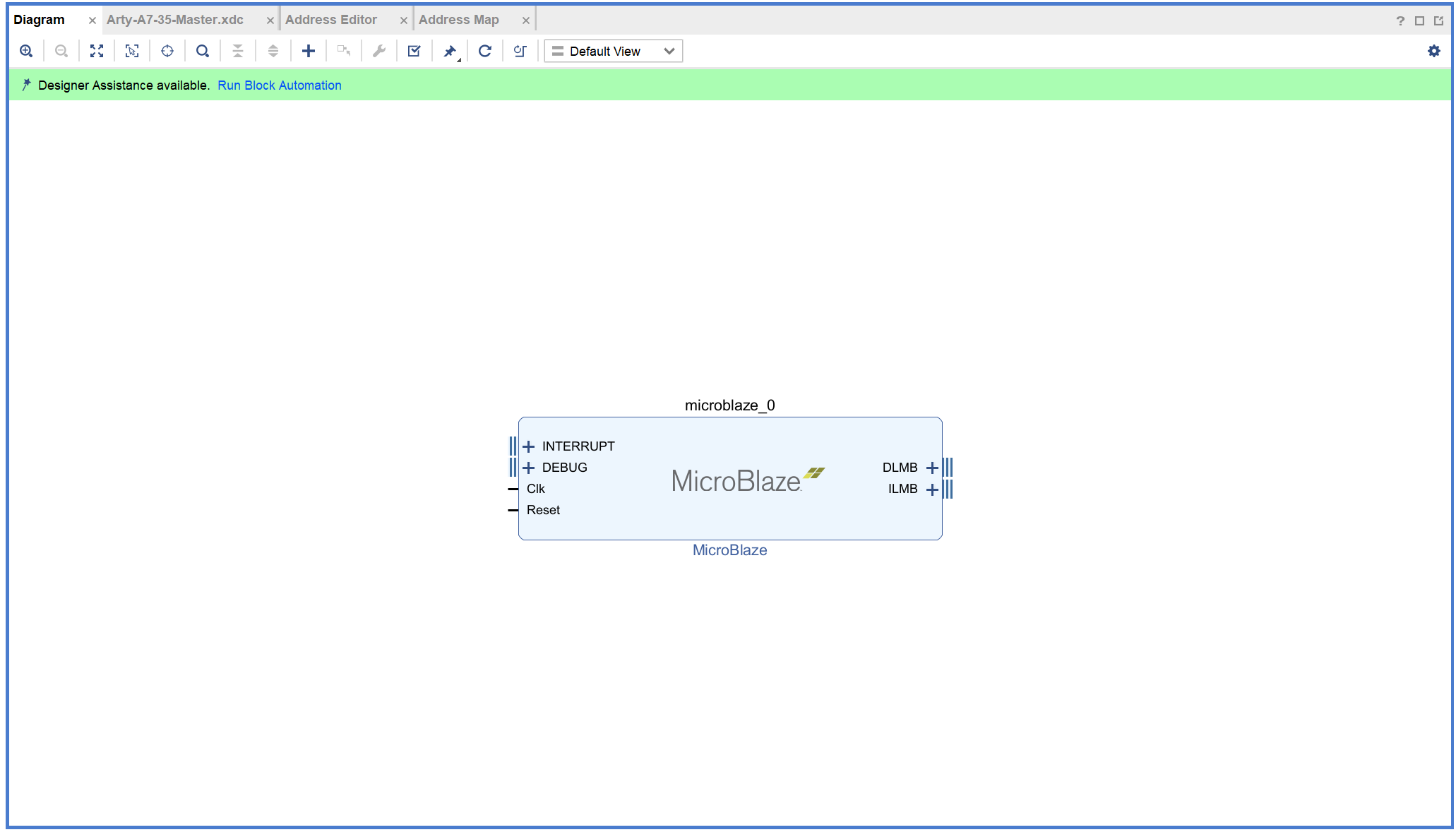

MicroBrazeを配置

Designの上バーの+を押すと追加するIPを指定するダイアログが出るので MicroBlazeを検索して追加

-

各種設定

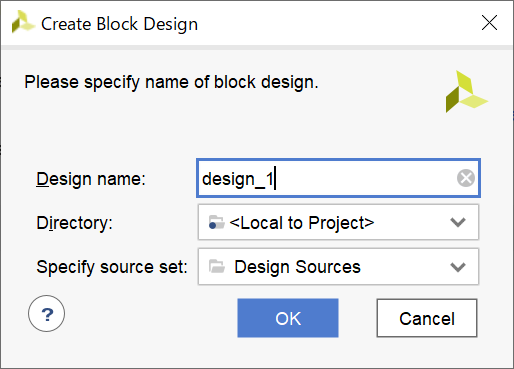

4.で追加するとウィンドウ内が変わるので画面上の Run Block Automation をクリック

設定Windowが出るので -

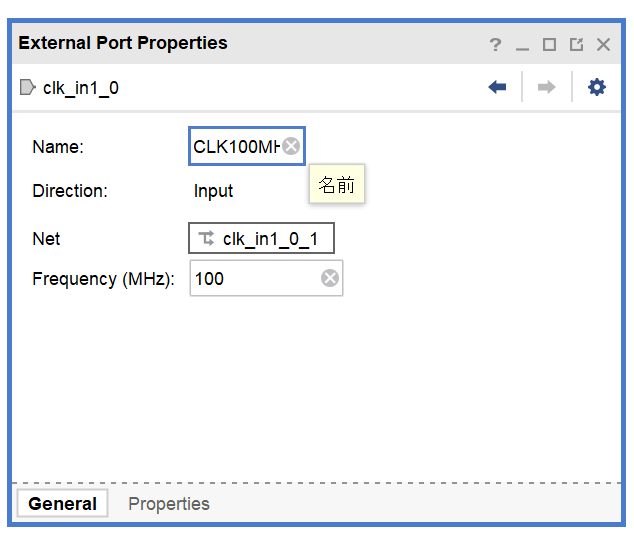

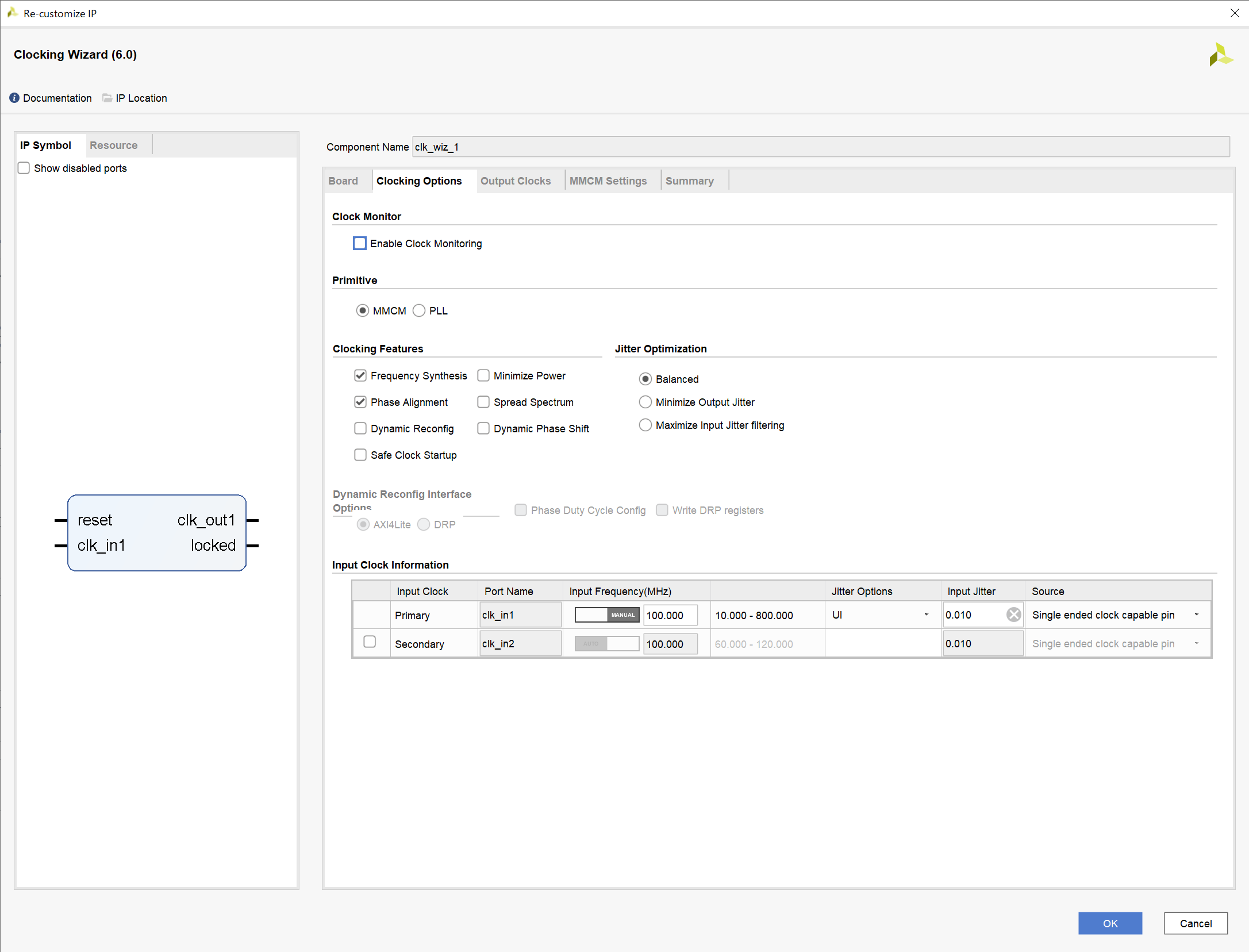

Clocing Wizardの設定

画面左下のClocing Wizardをダブルクリック

ダイアログが立ち上がるのでClocking Optionsをタブで選ぶ

下部のPrimaryのInput Frequencyをマニュアル:100MHzに

SourceをSingle ended clock capable pinに -

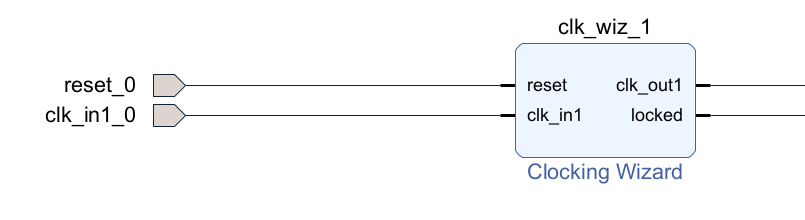

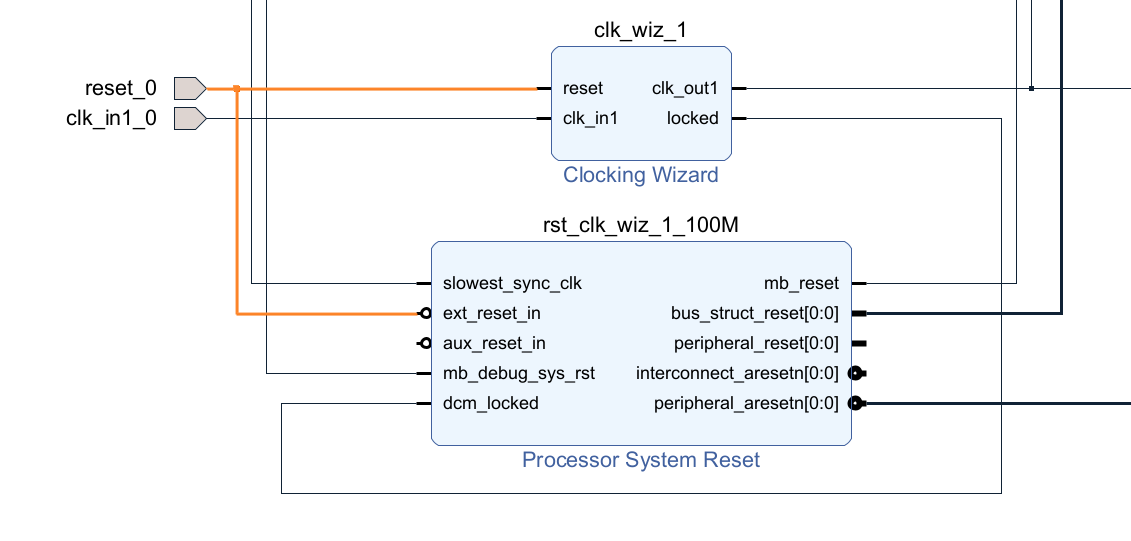

入力ポートの接続とリセット接続

reset、clk_in1の上で右クリック->Make Externalを実行

すると外部に端子ができる

-

リセット配線

リセット生成IPのext_reset_in端子とreset_0をつなげる

リセット生成IPのext_reset_in端子にマウスカーソルを近づけると鉛筆アイコンになるのでそれでドラッグアンドドロップでreset_0に

-

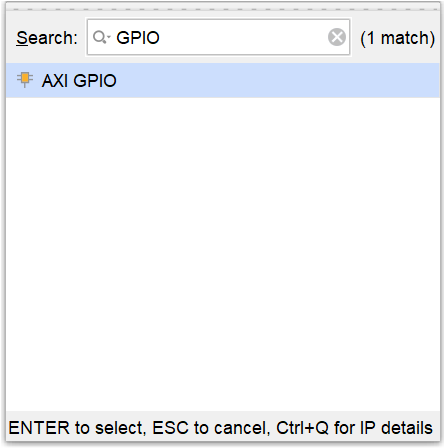

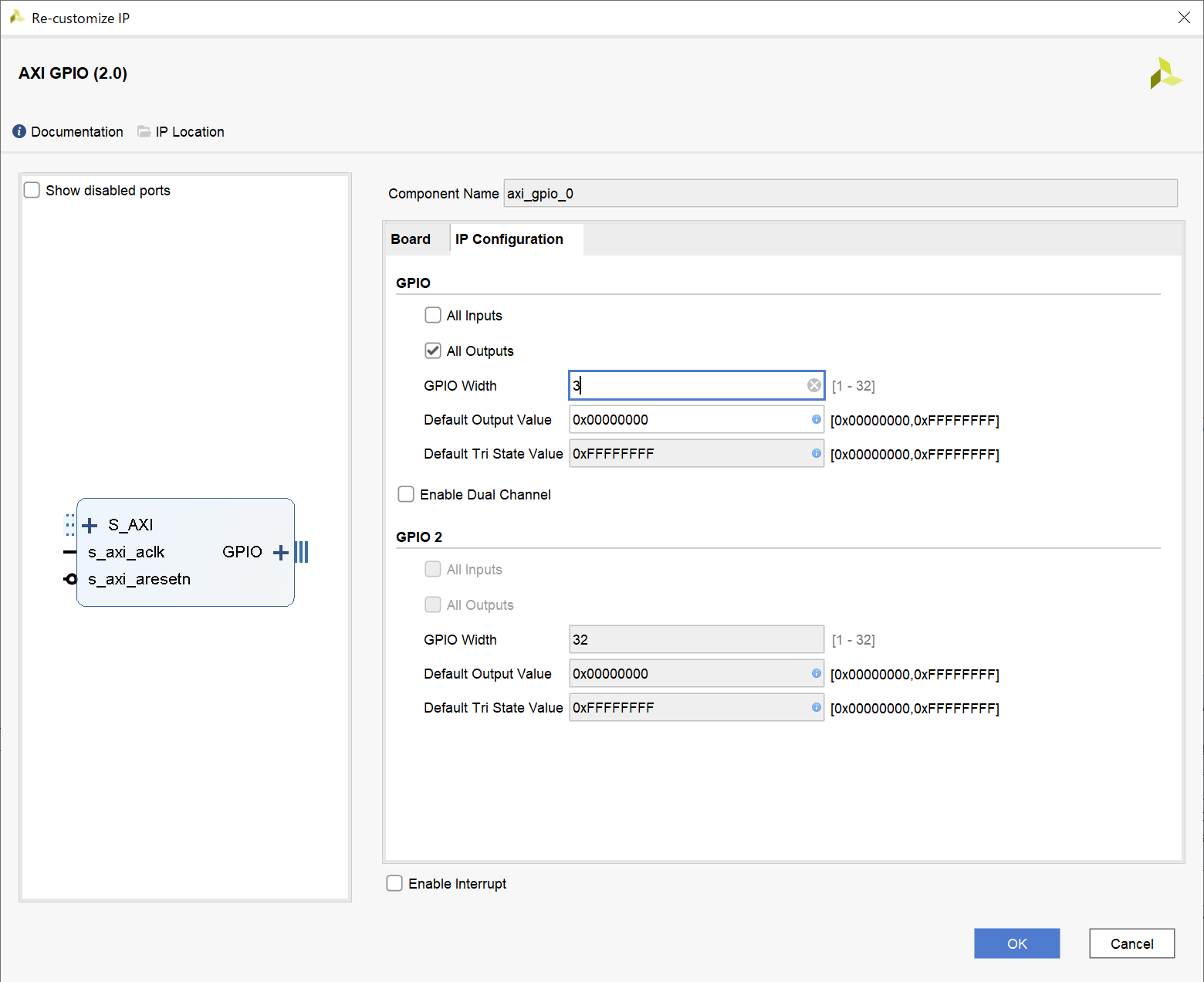

GPIO追加&設定

Add IPから AXI GPIOを追加

追加できたらAXI GPIOをダブルクリック->IP Configurationから

ALL OutputsをONに、GPIO Widthを3に

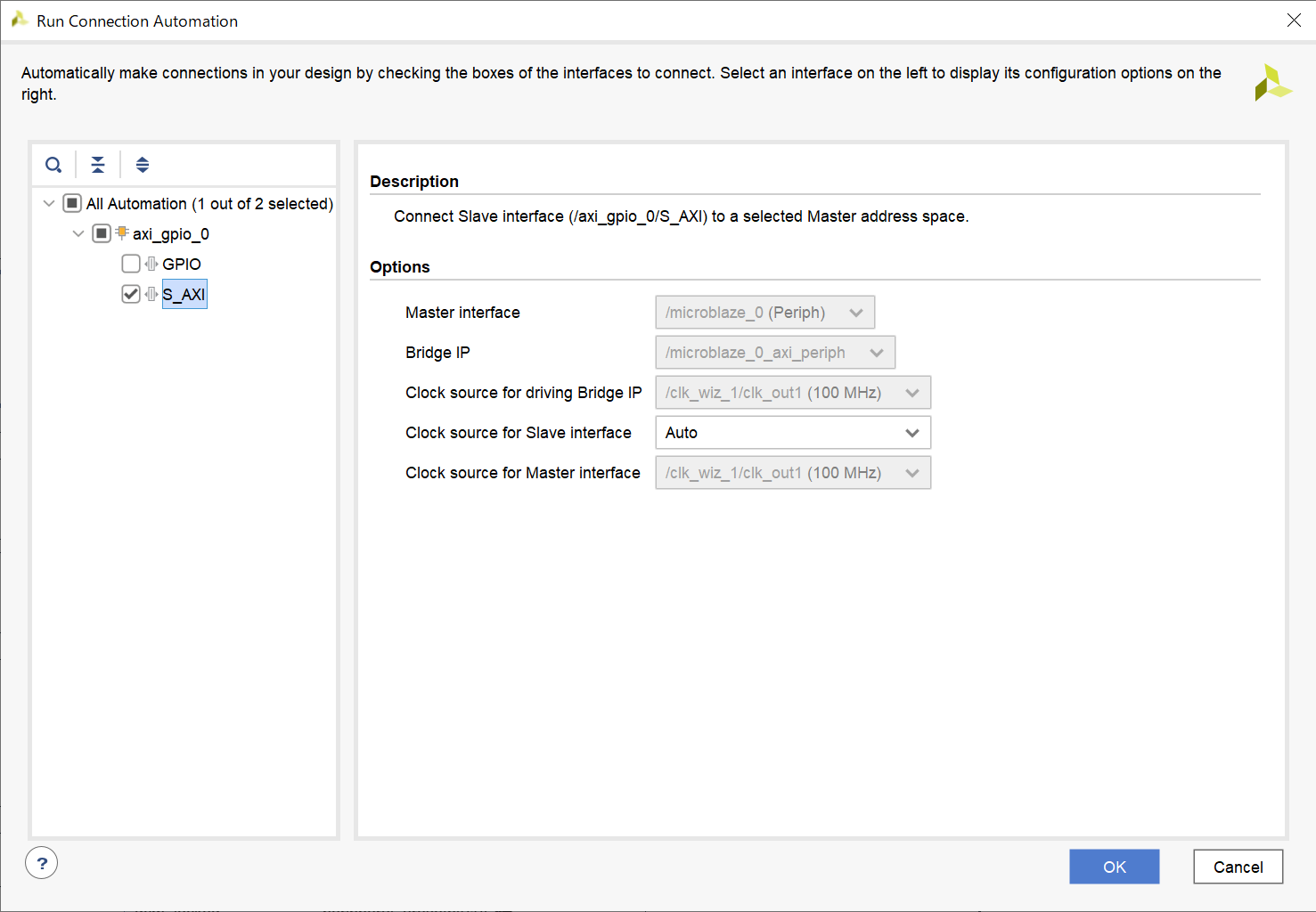

画面上部にまたRun Block Automationが表示されるのでクリック

S_AXIにチェックを付けてOK

画面上のAXI_GPIOの中のGPIOの右の+をクリック

するとgpio_io_o[2:0]ができるのでまた右クリック->Make Externalを実行

最後まで生成できると下記のような図になる

-

ポート名の修正

制約ファイルのポート名と合わせないとダメらしい

修正するのは -

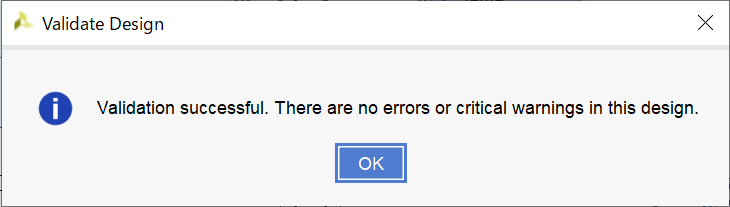

配線チェック

ここまでできたら画面上のValidate Designをクリックし回路チェックをする

問題なければ下記ダイアログが出る

今日はここまで