目次

はじめに

こんにちは。株式会社フィックスターズ の 望月 英輔 と申します。

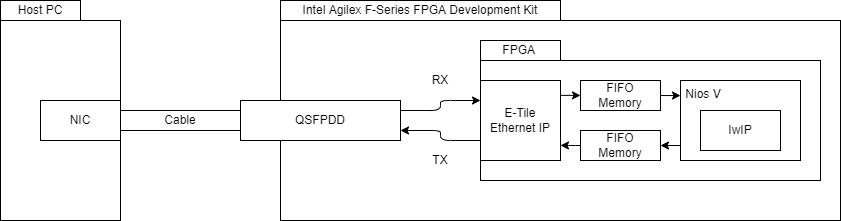

手元にあったES 品のIntel Agilex F-Series FPGA Development Kit を使用してTCP/IP 通信を行いました。

通信に必要なハードウェアはボード上に揃っているので、FPGA 上に通信するためのデザインを構築した手順を紹介します。

引用元: https://www.intel.co.jp/content/www/jp/ja/products/details/fpga/development-kits/agilex/f-series.html

Intel FPGA でTCP/IP 通信を行うには

Intel FPGA でTCP/IP 通信を行いたい場合、Nios® V Processor - Using the MicroC/TCP-IP Stack を利用する方法が挙げられます。

Intel 公式でサポートしているものなので、とりあえず動かしてみるにはこちらを選択するのがベターです。

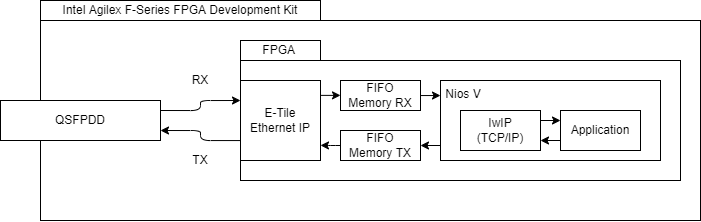

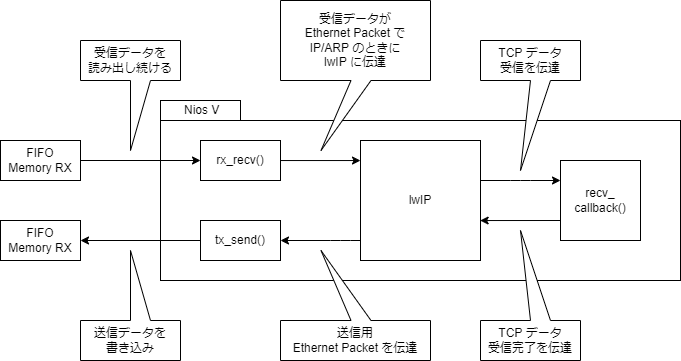

ただ今回は、OS なしで軽量に動作させたかったのと、単純にそれだけでは面白くないと思ったので、Nios V 上で軽量なTCP/IP プロトコル・スタック実装であるlwIP を動作させる、以下のような構成としました。

このような構成としたのは、

- E-Tile とのデータのやり取りはStream で行われる

- Nios V とのデータのやり取りはMemory Map で行いたい

という事情があり、Stream とMemory Map を変換するFIFO Memory を配置したという経緯があるためです。

Nios V からMemory Map でデータにアクセスできるようになれば、あとはNios V で動作するコードの開発を行えばよいので、FPGA 側はそれ以上の機能を有していません。

以下に用語の簡単な解説を記載しますので、併せてご覧ください。

Nios V

Intel FPGA に実装可能なRISC-V ソフトコア・プロセッサです。

今回はlwIP を動作させるために使用します。

詳細は Nios® V プロセッサー - インテル® FPGA をご覧ください

lwIP (lightweight IP)

オープンソースの軽量なTCP/IP プロトコル・スタック実装です。

今回はこちらをNios V 上で動作させ、TCP/IP 通信を実現します。

詳細は lwIP - A Lightweight TCP_IP stack - Summary [Savannah] をご覧ください。

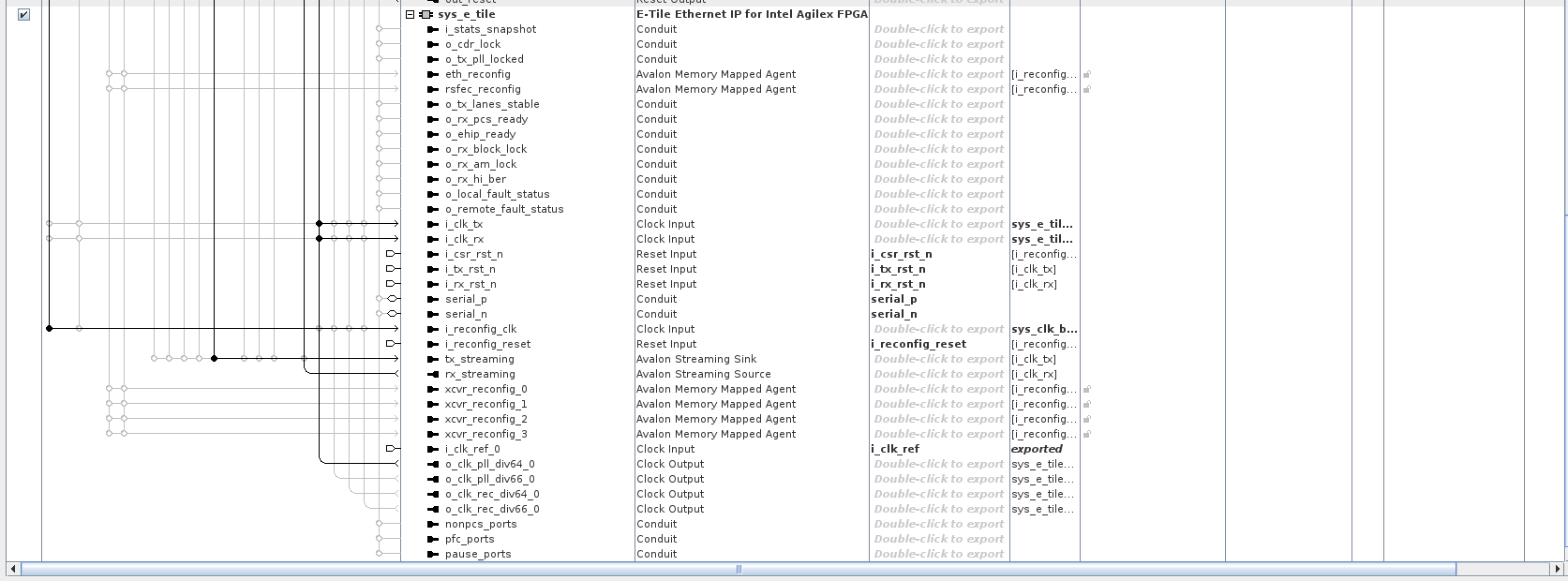

E-Tile

Stratix 10, Agilex に搭載されている高速トランシーバーです。

インテル ® FPGA E タイル・トランシーバー 紹介 – 株式会社マクニカ アルティマ カンパニー に詳しい記載があります。

今回は10/25/100Gbps のEthernet として利用可能な"E-Tile Ethernet IP"の一部として使用します。

詳細は インテル® Agilex™ およびインテル® Stratix® 10 FPGA E タイル・ハード IP をご覧ください。

FIFO Memory

E-Tile Ethernet IP へStream で入出力されるデータを、Nios V がアクセス可能なMemory Map 方式に変換するためのFIFO です。

詳細は 24. インテルFPGA Avalon FIFOメモリーコア をご覧ください。

QSFPDD

最大400Gbps での通信が可能なコネクタシステムです。

400G時代を見据えたモジュール/ケージ/コネクタシステム「QSFP-DD」 :: JANOG40 に詳しい記載があります。

FPGA の実装

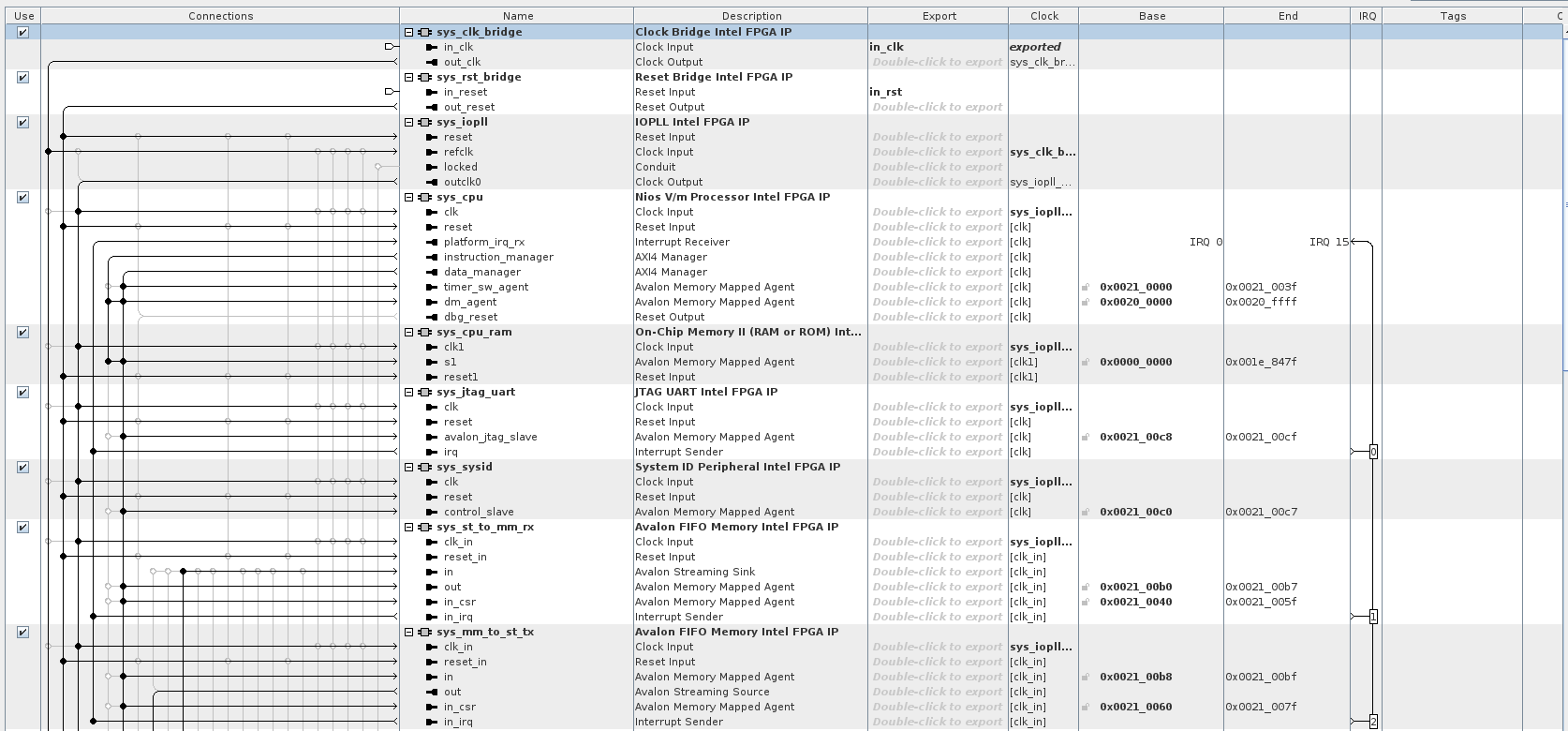

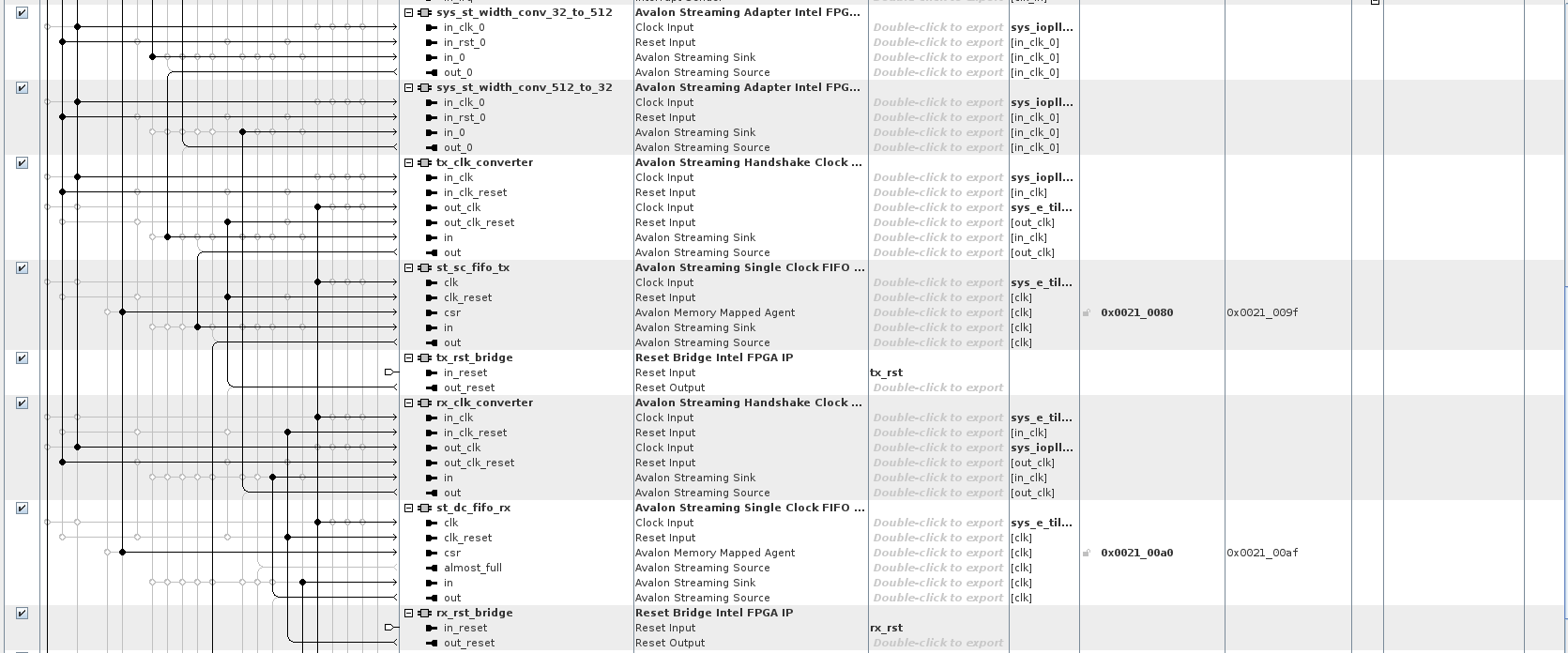

E-Tile Ethernet IP, FIFO Memory, Nios V をFPGA 上に実装します。

いずれもIntel 純正で用意されているIP だったため、Platform Designer を利用しました。

クロック乗り換えやAvalon-ST の幅変換、Nios V 用のメモリ等IP が追加されていますが、構成自体は「Intel FPGA でTCP/IP 通信を行うには」の図と同様です。

図だけだと各IP の設定が分からないので、tcl スクリプト化したものを用意しました。

sys.tcl を下記コマンドで展開すると、Platform Designer で中身を確認できます。

# sys.tcl を展開

$ qsys-script --script=sys.tcl

# Platform Designer で確認

$ qsys-edit sys.qsys -qpf=sys.qpf

sys.tcl

package require -exact qsys 21.3

# create the system "sys"

proc do_create_sys {} {

# create the system

create_system sys

set_project_property DEVICE {AGFB014R24A2E3VR0}

set_project_property DEVICE_FAMILY {Agilex}

set_project_property HIDE_FROM_IP_CATALOG {false}

set_use_testbench_naming_pattern 0 {}

# add HDL parameters

# add the components

add_component rx_clk_converter ip/sys/sys_hs_clk_xer_1.ip hs_clk_xer hs_clk_xer_1 19.3.1

load_component rx_clk_converter

set_component_parameter_value BITS_PER_SYMBOL {8}

set_component_parameter_value CHANNEL_WIDTH {1}

set_component_parameter_value DATA_WIDTH {512}

set_component_parameter_value ERROR_WIDTH {1}

set_component_parameter_value MAX_CHANNEL {0}

set_component_parameter_value READY_SYNC_DEPTH {2}

set_component_parameter_value SYNC_RESET {0}

set_component_parameter_value USE_CHANNEL {0}

set_component_parameter_value USE_ERROR {0}

set_component_parameter_value USE_OUTPUT_PIPELINE {1}

set_component_parameter_value USE_PACKETS {1}

set_component_parameter_value VALID_SYNC_DEPTH {2}

set_component_project_property HIDE_FROM_IP_CATALOG {false}

save_component

load_instantiation rx_clk_converter

remove_instantiation_interfaces_and_ports

add_instantiation_interface in_clk clock INPUT

set_instantiation_interface_parameter_value in_clk clockRate {0}

set_instantiation_interface_parameter_value in_clk externallyDriven {false}

set_instantiation_interface_parameter_value in_clk ptfSchematicName {}

add_instantiation_interface_port in_clk in_clk clk 1 STD_LOGIC Input

add_instantiation_interface in_clk_reset reset INPUT

set_instantiation_interface_parameter_value in_clk_reset associatedClock {in_clk}

set_instantiation_interface_parameter_value in_clk_reset synchronousEdges {DEASSERT}

add_instantiation_interface_port in_clk_reset in_reset reset 1 STD_LOGIC Input

add_instantiation_interface out_clk clock INPUT

set_instantiation_interface_parameter_value out_clk clockRate {0}

set_instantiation_interface_parameter_value out_clk externallyDriven {false}

set_instantiation_interface_parameter_value out_clk ptfSchematicName {}

add_instantiation_interface_port out_clk out_clk clk 1 STD_LOGIC Input

add_instantiation_interface out_clk_reset reset INPUT

set_instantiation_interface_parameter_value out_clk_reset associatedClock {out_clk}

set_instantiation_interface_parameter_value out_clk_reset synchronousEdges {DEASSERT}

add_instantiation_interface_port out_clk_reset out_reset reset 1 STD_LOGIC Input

add_instantiation_interface in avalon_streaming INPUT

set_instantiation_interface_parameter_value in associatedClock {in_clk}

set_instantiation_interface_parameter_value in associatedReset {in_clk_reset}

set_instantiation_interface_parameter_value in beatsPerCycle {1}

set_instantiation_interface_parameter_value in dataBitsPerSymbol {8}

set_instantiation_interface_parameter_value in emptyWithinPacket {false}

set_instantiation_interface_parameter_value in errorDescriptor {}

set_instantiation_interface_parameter_value in firstSymbolInHighOrderBits {true}

set_instantiation_interface_parameter_value in highOrderSymbolAtMSB {false}

set_instantiation_interface_parameter_value in maxChannel {0}

set_instantiation_interface_parameter_value in packetDescription {}

set_instantiation_interface_parameter_value in prSafe {false}

set_instantiation_interface_parameter_value in readyAllowance {0}

set_instantiation_interface_parameter_value in readyLatency {0}

set_instantiation_interface_parameter_value in symbolsPerBeat {1}

add_instantiation_interface_port in in_ready ready 1 STD_LOGIC Output

add_instantiation_interface_port in in_valid valid 1 STD_LOGIC Input

add_instantiation_interface_port in in_startofpacket startofpacket 1 STD_LOGIC Input

add_instantiation_interface_port in in_endofpacket endofpacket 1 STD_LOGIC Input

add_instantiation_interface_port in in_empty empty 6 STD_LOGIC_VECTOR Input

add_instantiation_interface_port in in_data data 512 STD_LOGIC_VECTOR Input

add_instantiation_interface out avalon_streaming OUTPUT

set_instantiation_interface_parameter_value out associatedClock {out_clk}

set_instantiation_interface_parameter_value out associatedReset {out_clk_reset}

set_instantiation_interface_parameter_value out beatsPerCycle {1}

set_instantiation_interface_parameter_value out dataBitsPerSymbol {8}

set_instantiation_interface_parameter_value out emptyWithinPacket {false}

set_instantiation_interface_parameter_value out errorDescriptor {}

set_instantiation_interface_parameter_value out firstSymbolInHighOrderBits {true}

set_instantiation_interface_parameter_value out highOrderSymbolAtMSB {false}

set_instantiation_interface_parameter_value out maxChannel {0}

set_instantiation_interface_parameter_value out packetDescription {}

set_instantiation_interface_parameter_value out prSafe {false}

set_instantiation_interface_parameter_value out readyAllowance {0}

set_instantiation_interface_parameter_value out readyLatency {0}

set_instantiation_interface_parameter_value out symbolsPerBeat {1}

add_instantiation_interface_port out out_ready ready 1 STD_LOGIC Input

add_instantiation_interface_port out out_valid valid 1 STD_LOGIC Output

add_instantiation_interface_port out out_startofpacket startofpacket 1 STD_LOGIC Output

add_instantiation_interface_port out out_endofpacket endofpacket 1 STD_LOGIC Output

add_instantiation_interface_port out out_empty empty 6 STD_LOGIC_VECTOR Output

add_instantiation_interface_port out out_data data 512 STD_LOGIC_VECTOR Output

save_instantiation

add_component rx_rst_bridge ip/sys/sys_rst_bridge.ip altera_reset_bridge sys_rst_bridge 19.2.0

load_component rx_rst_bridge

set_component_parameter_value ACTIVE_LOW_RESET {0}

set_component_parameter_value NUM_RESET_OUTPUTS {1}

set_component_parameter_value SYNCHRONOUS_EDGES {none}

set_component_parameter_value SYNC_RESET {0}

set_component_parameter_value USE_RESET_REQUEST {0}

set_component_project_property HIDE_FROM_IP_CATALOG {false}

save_component

load_instantiation rx_rst_bridge

remove_instantiation_interfaces_and_ports

add_instantiation_interface in_reset reset INPUT

set_instantiation_interface_parameter_value in_reset associatedClock {}

set_instantiation_interface_parameter_value in_reset synchronousEdges {NONE}

add_instantiation_interface_port in_reset in_reset reset 1 STD_LOGIC Input

add_instantiation_interface out_reset reset OUTPUT

set_instantiation_interface_parameter_value out_reset associatedClock {}

set_instantiation_interface_parameter_value out_reset associatedDirectReset {in_reset}

set_instantiation_interface_parameter_value out_reset associatedResetSinks {in_reset}

set_instantiation_interface_parameter_value out_reset synchronousEdges {NONE}

add_instantiation_interface_port out_reset out_reset reset 1 STD_LOGIC Output

save_instantiation

add_component st_dc_fifo_rx ip/sys/sys_sc_fifo_1.ip altera_avalon_sc_fifo sc_fifo_1 19.3.1

load_component st_dc_fifo_rx

set_component_parameter_value BITS_PER_SYMBOL {8}

set_component_parameter_value CHANNEL_WIDTH {0}

set_component_parameter_value EMPTY_LATENCY {3}

set_component_parameter_value ENABLE_EXPLICIT_MAXCHANNEL {0}

set_component_parameter_value ERROR_WIDTH {0}

set_component_parameter_value EXPLICIT_MAXCHANNEL {0}

set_component_parameter_value FIFO_DEPTH {1024}

set_component_parameter_value SYMBOLS_PER_BEAT {64}

set_component_parameter_value SYNC_RESET {0}

set_component_parameter_value USE_ALMOST_EMPTY_IF {0}

set_component_parameter_value USE_ALMOST_FULL_IF {1}

set_component_parameter_value USE_FILL_LEVEL {1}

set_component_parameter_value USE_MEMORY_BLOCKS {1}

set_component_parameter_value USE_PACKETS {1}

set_component_parameter_value USE_STORE_FORWARD {0}

set_component_project_property HIDE_FROM_IP_CATALOG {false}

save_component

load_instantiation st_dc_fifo_rx

remove_instantiation_interfaces_and_ports

set_instantiation_assignment_value debug.isTransparent {1}

add_instantiation_interface clk clock INPUT

set_instantiation_interface_parameter_value clk clockRate {0}

set_instantiation_interface_parameter_value clk externallyDriven {false}

set_instantiation_interface_parameter_value clk ptfSchematicName {}

add_instantiation_interface_port clk clk clk 1 STD_LOGIC Input

add_instantiation_interface clk_reset reset INPUT

set_instantiation_interface_parameter_value clk_reset associatedClock {clk}

set_instantiation_interface_parameter_value clk_reset synchronousEdges {DEASSERT}

add_instantiation_interface_port clk_reset reset reset 1 STD_LOGIC Input

add_instantiation_interface csr avalon INPUT

set_instantiation_interface_parameter_value csr addressAlignment {DYNAMIC}

set_instantiation_interface_parameter_value csr addressGroup {0}

set_instantiation_interface_parameter_value csr addressSpan {16}

set_instantiation_interface_parameter_value csr addressUnits {WORDS}

set_instantiation_interface_parameter_value csr alwaysBurstMaxBurst {false}

set_instantiation_interface_parameter_value csr associatedClock {clk}

set_instantiation_interface_parameter_value csr associatedReset {clk_reset}

set_instantiation_interface_parameter_value csr bitsPerSymbol {8}

set_instantiation_interface_parameter_value csr bridgedAddressOffset {0}

set_instantiation_interface_parameter_value csr bridgesToMaster {}

set_instantiation_interface_parameter_value csr burstOnBurstBoundariesOnly {false}

set_instantiation_interface_parameter_value csr burstcountUnits {WORDS}

set_instantiation_interface_parameter_value csr constantBurstBehavior {false}

set_instantiation_interface_parameter_value csr explicitAddressSpan {0}

set_instantiation_interface_parameter_value csr holdTime {0}

set_instantiation_interface_parameter_value csr interleaveBursts {false}

set_instantiation_interface_parameter_value csr isBigEndian {false}

set_instantiation_interface_parameter_value csr isFlash {false}

set_instantiation_interface_parameter_value csr isMemoryDevice {false}

set_instantiation_interface_parameter_value csr isNonVolatileStorage {false}

set_instantiation_interface_parameter_value csr linewrapBursts {false}

set_instantiation_interface_parameter_value csr maximumPendingReadTransactions {0}

set_instantiation_interface_parameter_value csr maximumPendingWriteTransactions {0}

set_instantiation_interface_parameter_value csr minimumReadLatency {1}

set_instantiation_interface_parameter_value csr minimumResponseLatency {1}

set_instantiation_interface_parameter_value csr minimumUninterruptedRunLength {1}

set_instantiation_interface_parameter_value csr prSafe {false}

set_instantiation_interface_parameter_value csr printableDevice {false}

set_instantiation_interface_parameter_value csr readLatency {1}

set_instantiation_interface_parameter_value csr readWaitStates {0}

set_instantiation_interface_parameter_value csr readWaitTime {0}

set_instantiation_interface_parameter_value csr registerIncomingSignals {false}

set_instantiation_interface_parameter_value csr registerOutgoingSignals {false}

set_instantiation_interface_parameter_value csr setupTime {0}

set_instantiation_interface_parameter_value csr timingUnits {Cycles}

set_instantiation_interface_parameter_value csr transparentBridge {false}

set_instantiation_interface_parameter_value csr waitrequestAllowance {0}

set_instantiation_interface_parameter_value csr wellBehavedWaitrequest {false}

set_instantiation_interface_parameter_value csr writeLatency {0}

set_instantiation_interface_parameter_value csr writeWaitStates {0}

set_instantiation_interface_parameter_value csr writeWaitTime {0}

set_instantiation_interface_assignment_value csr embeddedsw.configuration.isFlash {0}

set_instantiation_interface_assignment_value csr embeddedsw.configuration.isMemoryDevice {0}

set_instantiation_interface_assignment_value csr embeddedsw.configuration.isNonVolatileStorage {0}

set_instantiation_interface_assignment_value csr embeddedsw.configuration.isPrintableDevice {0}

set_instantiation_interface_sysinfo_parameter_value csr address_map {<address-map><slave name='csr' start='0x0' end='0x10' datawidth='32' /></address-map>}

set_instantiation_interface_sysinfo_parameter_value csr address_width {4}

set_instantiation_interface_sysinfo_parameter_value csr max_slave_data_width {32}

add_instantiation_interface_port csr csr_address address 2 STD_LOGIC_VECTOR Input

add_instantiation_interface_port csr csr_read read 1 STD_LOGIC Input

add_instantiation_interface_port csr csr_write write 1 STD_LOGIC Input

add_instantiation_interface_port csr csr_readdata readdata 32 STD_LOGIC_VECTOR Output

add_instantiation_interface_port csr csr_writedata writedata 32 STD_LOGIC_VECTOR Input

add_instantiation_interface almost_full avalon_streaming OUTPUT

set_instantiation_interface_parameter_value almost_full associatedClock {clk}

set_instantiation_interface_parameter_value almost_full associatedReset {clk_reset}

set_instantiation_interface_parameter_value almost_full beatsPerCycle {1}

set_instantiation_interface_parameter_value almost_full dataBitsPerSymbol {1}

set_instantiation_interface_parameter_value almost_full emptyWithinPacket {false}

set_instantiation_interface_parameter_value almost_full errorDescriptor {}

set_instantiation_interface_parameter_value almost_full firstSymbolInHighOrderBits {true}

set_instantiation_interface_parameter_value almost_full highOrderSymbolAtMSB {false}

set_instantiation_interface_parameter_value almost_full maxChannel {0}

set_instantiation_interface_parameter_value almost_full packetDescription {}

set_instantiation_interface_parameter_value almost_full prSafe {false}

set_instantiation_interface_parameter_value almost_full readyAllowance {0}

set_instantiation_interface_parameter_value almost_full readyLatency {0}

set_instantiation_interface_parameter_value almost_full symbolsPerBeat {1}

add_instantiation_interface_port almost_full almost_full_data data 1 STD_LOGIC Output

add_instantiation_interface in avalon_streaming INPUT

set_instantiation_interface_parameter_value in associatedClock {clk}

set_instantiation_interface_parameter_value in associatedReset {clk_reset}

set_instantiation_interface_parameter_value in beatsPerCycle {1}

set_instantiation_interface_parameter_value in dataBitsPerSymbol {8}

set_instantiation_interface_parameter_value in emptyWithinPacket {false}

set_instantiation_interface_parameter_value in errorDescriptor {}

set_instantiation_interface_parameter_value in firstSymbolInHighOrderBits {true}

set_instantiation_interface_parameter_value in highOrderSymbolAtMSB {false}

set_instantiation_interface_parameter_value in maxChannel {0}

set_instantiation_interface_parameter_value in packetDescription {}

set_instantiation_interface_parameter_value in prSafe {false}

set_instantiation_interface_parameter_value in readyAllowance {0}

set_instantiation_interface_parameter_value in readyLatency {0}

set_instantiation_interface_parameter_value in symbolsPerBeat {64}

add_instantiation_interface_port in in_data data 512 STD_LOGIC_VECTOR Input

add_instantiation_interface_port in in_valid valid 1 STD_LOGIC Input

add_instantiation_interface_port in in_ready ready 1 STD_LOGIC Output

add_instantiation_interface_port in in_startofpacket startofpacket 1 STD_LOGIC Input

add_instantiation_interface_port in in_endofpacket endofpacket 1 STD_LOGIC Input

add_instantiation_interface_port in in_empty empty 6 STD_LOGIC_VECTOR Input

add_instantiation_interface out avalon_streaming OUTPUT

set_instantiation_interface_parameter_value out associatedClock {clk}

set_instantiation_interface_parameter_value out associatedReset {clk_reset}

set_instantiation_interface_parameter_value out beatsPerCycle {1}

set_instantiation_interface_parameter_value out dataBitsPerSymbol {8}

set_instantiation_interface_parameter_value out emptyWithinPacket {false}

set_instantiation_interface_parameter_value out errorDescriptor {}

set_instantiation_interface_parameter_value out firstSymbolInHighOrderBits {true}

set_instantiation_interface_parameter_value out highOrderSymbolAtMSB {false}

set_instantiation_interface_parameter_value out maxChannel {0}

set_instantiation_interface_parameter_value out packetDescription {}

set_instantiation_interface_parameter_value out prSafe {false}

set_instantiation_interface_parameter_value out readyAllowance {0}

set_instantiation_interface_parameter_value out readyLatency {0}

set_instantiation_interface_parameter_value out symbolsPerBeat {64}

set_instantiation_interface_assignment_value out debug.controlledBy {in}

add_instantiation_interface_port out out_data data 512 STD_LOGIC_VECTOR Output

add_instantiation_interface_port out out_valid valid 1 STD_LOGIC Output

add_instantiation_interface_port out out_ready ready 1 STD_LOGIC Input

add_instantiation_interface_port out out_startofpacket startofpacket 1 STD_LOGIC Output

add_instantiation_interface_port out out_endofpacket endofpacket 1 STD_LOGIC Output

add_instantiation_interface_port out out_empty empty 6 STD_LOGIC_VECTOR Output

save_instantiation

add_component st_sc_fifo_tx ip/sys/sys_sc_fifo_0.ip altera_avalon_sc_fifo sc_fifo_0 19.3.1

load_component st_sc_fifo_tx

set_component_parameter_value BITS_PER_SYMBOL {8}

set_component_parameter_value CHANNEL_WIDTH {0}

set_component_parameter_value EMPTY_LATENCY {3}

set_component_parameter_value ENABLE_EXPLICIT_MAXCHANNEL {0}

set_component_parameter_value ERROR_WIDTH {0}

set_component_parameter_value EXPLICIT_MAXCHANNEL {0}

set_component_parameter_value FIFO_DEPTH {1024}

set_component_parameter_value SYMBOLS_PER_BEAT {64}

set_component_parameter_value SYNC_RESET {0}

set_component_parameter_value USE_ALMOST_EMPTY_IF {0}

set_component_parameter_value USE_ALMOST_FULL_IF {0}

set_component_parameter_value USE_FILL_LEVEL {1}

set_component_parameter_value USE_MEMORY_BLOCKS {1}

set_component_parameter_value USE_PACKETS {1}

set_component_parameter_value USE_STORE_FORWARD {1}

set_component_project_property HIDE_FROM_IP_CATALOG {false}

save_component

load_instantiation st_sc_fifo_tx

remove_instantiation_interfaces_and_ports

set_instantiation_assignment_value debug.isTransparent {1}

add_instantiation_interface clk clock INPUT

set_instantiation_interface_parameter_value clk clockRate {0}

set_instantiation_interface_parameter_value clk externallyDriven {false}

set_instantiation_interface_parameter_value clk ptfSchematicName {}

add_instantiation_interface_port clk clk clk 1 STD_LOGIC Input

add_instantiation_interface clk_reset reset INPUT

set_instantiation_interface_parameter_value clk_reset associatedClock {clk}

set_instantiation_interface_parameter_value clk_reset synchronousEdges {DEASSERT}

add_instantiation_interface_port clk_reset reset reset 1 STD_LOGIC Input

add_instantiation_interface csr avalon INPUT

set_instantiation_interface_parameter_value csr addressAlignment {DYNAMIC}

set_instantiation_interface_parameter_value csr addressGroup {0}

set_instantiation_interface_parameter_value csr addressSpan {32}

set_instantiation_interface_parameter_value csr addressUnits {WORDS}

set_instantiation_interface_parameter_value csr alwaysBurstMaxBurst {false}

set_instantiation_interface_parameter_value csr associatedClock {clk}

set_instantiation_interface_parameter_value csr associatedReset {clk_reset}

set_instantiation_interface_parameter_value csr bitsPerSymbol {8}

set_instantiation_interface_parameter_value csr bridgedAddressOffset {0}

set_instantiation_interface_parameter_value csr bridgesToMaster {}

set_instantiation_interface_parameter_value csr burstOnBurstBoundariesOnly {false}

set_instantiation_interface_parameter_value csr burstcountUnits {WORDS}

set_instantiation_interface_parameter_value csr constantBurstBehavior {false}

set_instantiation_interface_parameter_value csr explicitAddressSpan {0}

set_instantiation_interface_parameter_value csr holdTime {0}

set_instantiation_interface_parameter_value csr interleaveBursts {false}

set_instantiation_interface_parameter_value csr isBigEndian {false}

set_instantiation_interface_parameter_value csr isFlash {false}

set_instantiation_interface_parameter_value csr isMemoryDevice {false}

set_instantiation_interface_parameter_value csr isNonVolatileStorage {false}

set_instantiation_interface_parameter_value csr linewrapBursts {false}

set_instantiation_interface_parameter_value csr maximumPendingReadTransactions {0}

set_instantiation_interface_parameter_value csr maximumPendingWriteTransactions {0}

set_instantiation_interface_parameter_value csr minimumReadLatency {1}

set_instantiation_interface_parameter_value csr minimumResponseLatency {1}

set_instantiation_interface_parameter_value csr minimumUninterruptedRunLength {1}

set_instantiation_interface_parameter_value csr prSafe {false}

set_instantiation_interface_parameter_value csr printableDevice {false}

set_instantiation_interface_parameter_value csr readLatency {1}

set_instantiation_interface_parameter_value csr readWaitStates {0}

set_instantiation_interface_parameter_value csr readWaitTime {0}

set_instantiation_interface_parameter_value csr registerIncomingSignals {false}

set_instantiation_interface_parameter_value csr registerOutgoingSignals {false}

set_instantiation_interface_parameter_value csr setupTime {0}

set_instantiation_interface_parameter_value csr timingUnits {Cycles}

set_instantiation_interface_parameter_value csr transparentBridge {false}

set_instantiation_interface_parameter_value csr waitrequestAllowance {0}

set_instantiation_interface_parameter_value csr wellBehavedWaitrequest {false}

set_instantiation_interface_parameter_value csr writeLatency {0}

set_instantiation_interface_parameter_value csr writeWaitStates {0}

set_instantiation_interface_parameter_value csr writeWaitTime {0}

set_instantiation_interface_assignment_value csr embeddedsw.configuration.isFlash {0}

set_instantiation_interface_assignment_value csr embeddedsw.configuration.isMemoryDevice {0}

set_instantiation_interface_assignment_value csr embeddedsw.configuration.isNonVolatileStorage {0}

set_instantiation_interface_assignment_value csr embeddedsw.configuration.isPrintableDevice {0}

set_instantiation_interface_sysinfo_parameter_value csr address_map {<address-map><slave name='csr' start='0x0' end='0x20' datawidth='32' /></address-map>}

set_instantiation_interface_sysinfo_parameter_value csr address_width {5}

set_instantiation_interface_sysinfo_parameter_value csr max_slave_data_width {32}

add_instantiation_interface_port csr csr_address address 3 STD_LOGIC_VECTOR Input

add_instantiation_interface_port csr csr_read read 1 STD_LOGIC Input

add_instantiation_interface_port csr csr_write write 1 STD_LOGIC Input

add_instantiation_interface_port csr csr_readdata readdata 32 STD_LOGIC_VECTOR Output

add_instantiation_interface_port csr csr_writedata writedata 32 STD_LOGIC_VECTOR Input

add_instantiation_interface in avalon_streaming INPUT

set_instantiation_interface_parameter_value in associatedClock {clk}

set_instantiation_interface_parameter_value in associatedReset {clk_reset}

set_instantiation_interface_parameter_value in beatsPerCycle {1}

set_instantiation_interface_parameter_value in dataBitsPerSymbol {8}

set_instantiation_interface_parameter_value in emptyWithinPacket {false}

set_instantiation_interface_parameter_value in errorDescriptor {}

set_instantiation_interface_parameter_value in firstSymbolInHighOrderBits {true}

set_instantiation_interface_parameter_value in highOrderSymbolAtMSB {false}

set_instantiation_interface_parameter_value in maxChannel {0}

set_instantiation_interface_parameter_value in packetDescription {}

set_instantiation_interface_parameter_value in prSafe {false}

set_instantiation_interface_parameter_value in readyAllowance {0}

set_instantiation_interface_parameter_value in readyLatency {0}

set_instantiation_interface_parameter_value in symbolsPerBeat {64}

add_instantiation_interface_port in in_data data 512 STD_LOGIC_VECTOR Input

add_instantiation_interface_port in in_valid valid 1 STD_LOGIC Input

add_instantiation_interface_port in in_ready ready 1 STD_LOGIC Output

add_instantiation_interface_port in in_startofpacket startofpacket 1 STD_LOGIC Input

add_instantiation_interface_port in in_endofpacket endofpacket 1 STD_LOGIC Input

add_instantiation_interface_port in in_empty empty 6 STD_LOGIC_VECTOR Input

add_instantiation_interface out avalon_streaming OUTPUT

set_instantiation_interface_parameter_value out associatedClock {clk}

set_instantiation_interface_parameter_value out associatedReset {clk_reset}

set_instantiation_interface_parameter_value out beatsPerCycle {1}

set_instantiation_interface_parameter_value out dataBitsPerSymbol {8}

set_instantiation_interface_parameter_value out emptyWithinPacket {false}

set_instantiation_interface_parameter_value out errorDescriptor {}

set_instantiation_interface_parameter_value out firstSymbolInHighOrderBits {true}

set_instantiation_interface_parameter_value out highOrderSymbolAtMSB {false}

set_instantiation_interface_parameter_value out maxChannel {0}

set_instantiation_interface_parameter_value out packetDescription {}

set_instantiation_interface_parameter_value out prSafe {false}

set_instantiation_interface_parameter_value out readyAllowance {0}

set_instantiation_interface_parameter_value out readyLatency {0}

set_instantiation_interface_parameter_value out symbolsPerBeat {64}

set_instantiation_interface_assignment_value out debug.controlledBy {in}

add_instantiation_interface_port out out_data data 512 STD_LOGIC_VECTOR Output

add_instantiation_interface_port out out_valid valid 1 STD_LOGIC Output

add_instantiation_interface_port out out_ready ready 1 STD_LOGIC Input

add_instantiation_interface_port out out_startofpacket startofpacket 1 STD_LOGIC Output

add_instantiation_interface_port out out_endofpacket endofpacket 1 STD_LOGIC Output

add_instantiation_interface_port out out_empty empty 6 STD_LOGIC_VECTOR Output

save_instantiation

add_component sys_clk_bridge ip/sys/sys_clk_bridge.ip altera_clock_bridge sys_clk_bridge 19.2.0

load_component sys_clk_bridge

set_component_parameter_value EXPLICIT_CLOCK_RATE {100000000.0}

set_component_parameter_value NUM_CLOCK_OUTPUTS {1}

set_component_project_property HIDE_FROM_IP_CATALOG {false}

save_component

load_instantiation sys_clk_bridge

remove_instantiation_interfaces_and_ports

add_instantiation_interface in_clk clock INPUT

set_instantiation_interface_parameter_value in_clk clockRate {0}

set_instantiation_interface_parameter_value in_clk externallyDriven {false}

set_instantiation_interface_parameter_value in_clk ptfSchematicName {}

add_instantiation_interface_port in_clk in_clk clk 1 STD_LOGIC Input

add_instantiation_interface out_clk clock OUTPUT

set_instantiation_interface_parameter_value out_clk associatedDirectClock {in_clk}

set_instantiation_interface_parameter_value out_clk clockRate {100000000}

set_instantiation_interface_parameter_value out_clk clockRateKnown {true}

set_instantiation_interface_parameter_value out_clk externallyDriven {false}

set_instantiation_interface_parameter_value out_clk ptfSchematicName {}

set_instantiation_interface_sysinfo_parameter_value out_clk clock_rate {100000000}

add_instantiation_interface_port out_clk out_clk clk 1 STD_LOGIC Output

save_instantiation

add_component sys_cpu ip/sys/sys_cpu.ip intel_niosv_m sys_cpu 21.3.0

load_component sys_cpu

set_component_parameter_value enableDebug {1}

set_component_parameter_value exceptionOffset {32}

set_component_parameter_value exceptionSlave {sys_cpu_ram.s1}

set_component_parameter_value numGpr {32}

set_component_parameter_value resetOffset {0}

set_component_parameter_value resetSlave {sys_cpu_ram.s1}

set_component_parameter_value useResetReq {0}

set_component_project_property HIDE_FROM_IP_CATALOG {false}

save_component

load_instantiation sys_cpu

remove_instantiation_interfaces_and_ports

set_instantiation_assignment_value embeddedsw.CMacro.CPU_FREQ {300000000u}

set_instantiation_assignment_value embeddedsw.CMacro.DATA_ADDR_WIDTH {32}

set_instantiation_assignment_value embeddedsw.CMacro.DCACHE_LINE_SIZE {0}

set_instantiation_assignment_value embeddedsw.CMacro.DCACHE_LINE_SIZE_LOG2 {0}

set_instantiation_assignment_value embeddedsw.CMacro.DCACHE_SIZE {0}

set_instantiation_assignment_value embeddedsw.CMacro.EXCEPTION_ADDR {0x00000020}

set_instantiation_assignment_value embeddedsw.CMacro.HAS_DEBUG_STUB {}

set_instantiation_assignment_value embeddedsw.CMacro.ICACHE_LINE_SIZE {0}

set_instantiation_assignment_value embeddedsw.CMacro.ICACHE_LINE_SIZE_LOG2 {0}

set_instantiation_assignment_value embeddedsw.CMacro.ICACHE_SIZE {0}

set_instantiation_assignment_value embeddedsw.CMacro.INST_ADDR_WIDTH {32}

set_instantiation_assignment_value embeddedsw.CMacro.MTIME_OFFSET {0x00210000}

set_instantiation_assignment_value embeddedsw.CMacro.NUM_GPR {32}

set_instantiation_assignment_value embeddedsw.CMacro.RESET_ADDR {0x00000000}

set_instantiation_assignment_value embeddedsw.CMacro.TICKS_PER_SEC {no_quote(NIOSV_INTERNAL_TIMER_TICKS_PER_SECOND)}

set_instantiation_assignment_value embeddedsw.CMacro.TIMER_DEVICE_TYPE {2}

set_instantiation_assignment_value embeddedsw.configuration.HDLSimCachesCleared {1}

set_instantiation_assignment_value embeddedsw.configuration.cpuArchitecture {Abbotts Lake}

set_instantiation_assignment_value embeddedsw.configuration.exceptionOffset {32}

set_instantiation_assignment_value embeddedsw.configuration.exceptionSlave {sys_cpu_ram.s1}

set_instantiation_assignment_value embeddedsw.configuration.isTimerDevice {1}

set_instantiation_assignment_value embeddedsw.configuration.numGpr {32}

set_instantiation_assignment_value embeddedsw.configuration.resetOffset {0}

set_instantiation_assignment_value embeddedsw.configuration.resetSlave {sys_cpu_ram.s1}

set_instantiation_assignment_value embeddedsw.dts.params.altr,exception-addr {0x00000020}

set_instantiation_assignment_value embeddedsw.dts.params.altr,reset-addr {0x00000000}

set_instantiation_assignment_value embeddedsw.dts.params.clock-frequency {300000000u}

set_instantiation_assignment_value embeddedsw.dts.params.dcache-line-size {0}

set_instantiation_assignment_value embeddedsw.dts.params.dcache-size {0}

set_instantiation_assignment_value embeddedsw.dts.params.icache-line-size {0}

set_instantiation_assignment_value embeddedsw.dts.params.icache-size {0}

add_instantiation_interface clk clock INPUT

set_instantiation_interface_parameter_value clk clockRate {0}

set_instantiation_interface_parameter_value clk externallyDriven {false}

set_instantiation_interface_parameter_value clk ptfSchematicName {}

add_instantiation_interface_port clk clk clk 1 STD_LOGIC Input

add_instantiation_interface reset reset INPUT

set_instantiation_interface_parameter_value reset associatedClock {clk}

set_instantiation_interface_parameter_value reset synchronousEdges {DEASSERT}

add_instantiation_interface_port reset reset_reset reset 1 STD_LOGIC Input

add_instantiation_interface platform_irq_rx interrupt OUTPUT

set_instantiation_interface_parameter_value platform_irq_rx associatedAddressablePoint {}

set_instantiation_interface_parameter_value platform_irq_rx associatedClock {clk}

set_instantiation_interface_parameter_value platform_irq_rx associatedReset {reset}

set_instantiation_interface_parameter_value platform_irq_rx irqMap {}

set_instantiation_interface_parameter_value platform_irq_rx irqScheme {INDIVIDUAL_REQUESTS}

add_instantiation_interface_port platform_irq_rx platform_irq_rx_irq irq 16 STD_LOGIC_VECTOR Input

add_instantiation_interface instruction_manager axi4 OUTPUT

set_instantiation_interface_parameter_value instruction_manager associatedClock {clk}

set_instantiation_interface_parameter_value instruction_manager associatedReset {reset}

set_instantiation_interface_parameter_value instruction_manager combinedIssuingCapability {2}

set_instantiation_interface_parameter_value instruction_manager issuesFIXEDBursts {true}

set_instantiation_interface_parameter_value instruction_manager issuesINCRBursts {true}

set_instantiation_interface_parameter_value instruction_manager issuesWRAPBursts {true}

set_instantiation_interface_parameter_value instruction_manager maximumOutstandingReads {1}

set_instantiation_interface_parameter_value instruction_manager maximumOutstandingTransactions {1}

set_instantiation_interface_parameter_value instruction_manager maximumOutstandingWrites {1}

set_instantiation_interface_parameter_value instruction_manager readIssuingCapability {2}

set_instantiation_interface_parameter_value instruction_manager trustzoneAware {true}

set_instantiation_interface_parameter_value instruction_manager writeIssuingCapability {1}

add_instantiation_interface_port instruction_manager instruction_manager_awaddr awaddr 32 STD_LOGIC_VECTOR Output

add_instantiation_interface_port instruction_manager instruction_manager_awsize awsize 3 STD_LOGIC_VECTOR Output

add_instantiation_interface_port instruction_manager instruction_manager_awprot awprot 3 STD_LOGIC_VECTOR Output

add_instantiation_interface_port instruction_manager instruction_manager_awvalid awvalid 1 STD_LOGIC Output

add_instantiation_interface_port instruction_manager instruction_manager_awready awready 1 STD_LOGIC Input

add_instantiation_interface_port instruction_manager instruction_manager_wdata wdata 32 STD_LOGIC_VECTOR Output

add_instantiation_interface_port instruction_manager instruction_manager_wstrb wstrb 4 STD_LOGIC_VECTOR Output

add_instantiation_interface_port instruction_manager instruction_manager_wlast wlast 1 STD_LOGIC Output

add_instantiation_interface_port instruction_manager instruction_manager_wvalid wvalid 1 STD_LOGIC Output

add_instantiation_interface_port instruction_manager instruction_manager_wready wready 1 STD_LOGIC Input

add_instantiation_interface_port instruction_manager instruction_manager_bresp bresp 2 STD_LOGIC_VECTOR Input

add_instantiation_interface_port instruction_manager instruction_manager_bvalid bvalid 1 STD_LOGIC Input

add_instantiation_interface_port instruction_manager instruction_manager_bready bready 1 STD_LOGIC Output

add_instantiation_interface_port instruction_manager instruction_manager_araddr araddr 32 STD_LOGIC_VECTOR Output

add_instantiation_interface_port instruction_manager instruction_manager_arsize arsize 3 STD_LOGIC_VECTOR Output

add_instantiation_interface_port instruction_manager instruction_manager_arprot arprot 3 STD_LOGIC_VECTOR Output

add_instantiation_interface_port instruction_manager instruction_manager_arvalid arvalid 1 STD_LOGIC Output

add_instantiation_interface_port instruction_manager instruction_manager_arready arready 1 STD_LOGIC Input

add_instantiation_interface_port instruction_manager instruction_manager_rdata rdata 32 STD_LOGIC_VECTOR Input

add_instantiation_interface_port instruction_manager instruction_manager_rresp rresp 2 STD_LOGIC_VECTOR Input

add_instantiation_interface_port instruction_manager instruction_manager_rvalid rvalid 1 STD_LOGIC Input

add_instantiation_interface_port instruction_manager instruction_manager_rready rready 1 STD_LOGIC Output

add_instantiation_interface data_manager axi4 OUTPUT

set_instantiation_interface_parameter_value data_manager associatedClock {clk}

set_instantiation_interface_parameter_value data_manager associatedReset {reset}

set_instantiation_interface_parameter_value data_manager combinedIssuingCapability {1}

set_instantiation_interface_parameter_value data_manager issuesFIXEDBursts {true}

set_instantiation_interface_parameter_value data_manager issuesINCRBursts {true}

set_instantiation_interface_parameter_value data_manager issuesWRAPBursts {true}

set_instantiation_interface_parameter_value data_manager maximumOutstandingReads {1}

set_instantiation_interface_parameter_value data_manager maximumOutstandingTransactions {1}

set_instantiation_interface_parameter_value data_manager maximumOutstandingWrites {1}

set_instantiation_interface_parameter_value data_manager readIssuingCapability {1}

set_instantiation_interface_parameter_value data_manager trustzoneAware {true}

set_instantiation_interface_parameter_value data_manager writeIssuingCapability {1}

add_instantiation_interface_port data_manager data_manager_awaddr awaddr 32 STD_LOGIC_VECTOR Output

add_instantiation_interface_port data_manager data_manager_awsize awsize 3 STD_LOGIC_VECTOR Output

add_instantiation_interface_port data_manager data_manager_awprot awprot 3 STD_LOGIC_VECTOR Output

add_instantiation_interface_port data_manager data_manager_awvalid awvalid 1 STD_LOGIC Output

add_instantiation_interface_port data_manager data_manager_awready awready 1 STD_LOGIC Input

add_instantiation_interface_port data_manager data_manager_wdata wdata 32 STD_LOGIC_VECTOR Output

add_instantiation_interface_port data_manager data_manager_wstrb wstrb 4 STD_LOGIC_VECTOR Output

add_instantiation_interface_port data_manager data_manager_wlast wlast 1 STD_LOGIC Output

add_instantiation_interface_port data_manager data_manager_wvalid wvalid 1 STD_LOGIC Output

add_instantiation_interface_port data_manager data_manager_wready wready 1 STD_LOGIC Input

add_instantiation_interface_port data_manager data_manager_bresp bresp 2 STD_LOGIC_VECTOR Input

add_instantiation_interface_port data_manager data_manager_bvalid bvalid 1 STD_LOGIC Input

add_instantiation_interface_port data_manager data_manager_bready bready 1 STD_LOGIC Output

add_instantiation_interface_port data_manager data_manager_araddr araddr 32 STD_LOGIC_VECTOR Output

add_instantiation_interface_port data_manager data_manager_arsize arsize 3 STD_LOGIC_VECTOR Output

add_instantiation_interface_port data_manager data_manager_arprot arprot 3 STD_LOGIC_VECTOR Output

add_instantiation_interface_port data_manager data_manager_arvalid arvalid 1 STD_LOGIC Output

add_instantiation_interface_port data_manager data_manager_arready arready 1 STD_LOGIC Input

add_instantiation_interface_port data_manager data_manager_rdata rdata 32 STD_LOGIC_VECTOR Input

add_instantiation_interface_port data_manager data_manager_rresp rresp 2 STD_LOGIC_VECTOR Input

add_instantiation_interface_port data_manager data_manager_rvalid rvalid 1 STD_LOGIC Input

add_instantiation_interface_port data_manager data_manager_rready rready 1 STD_LOGIC Output

add_instantiation_interface timer_sw_agent avalon INPUT

set_instantiation_interface_parameter_value timer_sw_agent addressAlignment {DYNAMIC}

set_instantiation_interface_parameter_value timer_sw_agent addressGroup {0}

set_instantiation_interface_parameter_value timer_sw_agent addressSpan {64}

set_instantiation_interface_parameter_value timer_sw_agent addressUnits {SYMBOLS}

set_instantiation_interface_parameter_value timer_sw_agent alwaysBurstMaxBurst {false}

set_instantiation_interface_parameter_value timer_sw_agent associatedClock {clk}

set_instantiation_interface_parameter_value timer_sw_agent associatedReset {reset}

set_instantiation_interface_parameter_value timer_sw_agent bitsPerSymbol {8}

set_instantiation_interface_parameter_value timer_sw_agent bridgedAddressOffset {0}

set_instantiation_interface_parameter_value timer_sw_agent bridgesToMaster {}

set_instantiation_interface_parameter_value timer_sw_agent burstOnBurstBoundariesOnly {false}

set_instantiation_interface_parameter_value timer_sw_agent burstcountUnits {WORDS}

set_instantiation_interface_parameter_value timer_sw_agent constantBurstBehavior {false}

set_instantiation_interface_parameter_value timer_sw_agent explicitAddressSpan {0}

set_instantiation_interface_parameter_value timer_sw_agent holdTime {0}

set_instantiation_interface_parameter_value timer_sw_agent interleaveBursts {false}

set_instantiation_interface_parameter_value timer_sw_agent isBigEndian {false}

set_instantiation_interface_parameter_value timer_sw_agent isFlash {false}

set_instantiation_interface_parameter_value timer_sw_agent isMemoryDevice {false}

set_instantiation_interface_parameter_value timer_sw_agent isNonVolatileStorage {false}

set_instantiation_interface_parameter_value timer_sw_agent linewrapBursts {false}

set_instantiation_interface_parameter_value timer_sw_agent maximumPendingReadTransactions {2}

set_instantiation_interface_parameter_value timer_sw_agent maximumPendingWriteTransactions {0}

set_instantiation_interface_parameter_value timer_sw_agent minimumReadLatency {1}

set_instantiation_interface_parameter_value timer_sw_agent minimumResponseLatency {1}

set_instantiation_interface_parameter_value timer_sw_agent minimumUninterruptedRunLength {1}

set_instantiation_interface_parameter_value timer_sw_agent prSafe {false}

set_instantiation_interface_parameter_value timer_sw_agent printableDevice {false}

set_instantiation_interface_parameter_value timer_sw_agent readLatency {0}

set_instantiation_interface_parameter_value timer_sw_agent readWaitStates {1}

set_instantiation_interface_parameter_value timer_sw_agent readWaitTime {1}

set_instantiation_interface_parameter_value timer_sw_agent registerIncomingSignals {false}

set_instantiation_interface_parameter_value timer_sw_agent registerOutgoingSignals {false}

set_instantiation_interface_parameter_value timer_sw_agent setupTime {0}

set_instantiation_interface_parameter_value timer_sw_agent timingUnits {Cycles}

set_instantiation_interface_parameter_value timer_sw_agent transparentBridge {false}

set_instantiation_interface_parameter_value timer_sw_agent waitrequestAllowance {0}

set_instantiation_interface_parameter_value timer_sw_agent wellBehavedWaitrequest {false}

set_instantiation_interface_parameter_value timer_sw_agent writeLatency {0}

set_instantiation_interface_parameter_value timer_sw_agent writeWaitStates {0}

set_instantiation_interface_parameter_value timer_sw_agent writeWaitTime {0}

set_instantiation_interface_assignment_value timer_sw_agent embeddedsw.configuration.isFlash {0}

set_instantiation_interface_assignment_value timer_sw_agent embeddedsw.configuration.isMemoryDevice {0}

set_instantiation_interface_assignment_value timer_sw_agent embeddedsw.configuration.isNonVolatileStorage {0}

set_instantiation_interface_assignment_value timer_sw_agent embeddedsw.configuration.isPrintableDevice {0}

set_instantiation_interface_assignment_value timer_sw_agent qsys.ui.connect {data_manager}

set_instantiation_interface_sysinfo_parameter_value timer_sw_agent address_map {<address-map><slave name='timer_sw_agent' start='0x0' end='0x40' datawidth='32' /></address-map>}

set_instantiation_interface_sysinfo_parameter_value timer_sw_agent address_width {6}

set_instantiation_interface_sysinfo_parameter_value timer_sw_agent max_slave_data_width {32}

add_instantiation_interface_port timer_sw_agent timer_sw_agent_write write 1 STD_LOGIC Input

add_instantiation_interface_port timer_sw_agent timer_sw_agent_writedata writedata 32 STD_LOGIC_VECTOR Input

add_instantiation_interface_port timer_sw_agent timer_sw_agent_byteenable byteenable 4 STD_LOGIC_VECTOR Input

add_instantiation_interface_port timer_sw_agent timer_sw_agent_address address 6 STD_LOGIC_VECTOR Input

add_instantiation_interface_port timer_sw_agent timer_sw_agent_read read 1 STD_LOGIC Input

add_instantiation_interface_port timer_sw_agent timer_sw_agent_readdata readdata 32 STD_LOGIC_VECTOR Output

add_instantiation_interface_port timer_sw_agent timer_sw_agent_readdatavalid readdatavalid 1 STD_LOGIC Output

add_instantiation_interface dm_agent avalon INPUT

set_instantiation_interface_parameter_value dm_agent addressAlignment {DYNAMIC}

set_instantiation_interface_parameter_value dm_agent addressGroup {0}

set_instantiation_interface_parameter_value dm_agent addressSpan {65536}

set_instantiation_interface_parameter_value dm_agent addressUnits {SYMBOLS}

set_instantiation_interface_parameter_value dm_agent alwaysBurstMaxBurst {false}

set_instantiation_interface_parameter_value dm_agent associatedClock {clk}

set_instantiation_interface_parameter_value dm_agent associatedReset {reset}

set_instantiation_interface_parameter_value dm_agent bitsPerSymbol {8}

set_instantiation_interface_parameter_value dm_agent bridgedAddressOffset {0}

set_instantiation_interface_parameter_value dm_agent bridgesToMaster {}

set_instantiation_interface_parameter_value dm_agent burstOnBurstBoundariesOnly {false}

set_instantiation_interface_parameter_value dm_agent burstcountUnits {WORDS}

set_instantiation_interface_parameter_value dm_agent constantBurstBehavior {false}

set_instantiation_interface_parameter_value dm_agent explicitAddressSpan {0}

set_instantiation_interface_parameter_value dm_agent holdTime {0}

set_instantiation_interface_parameter_value dm_agent interleaveBursts {false}

set_instantiation_interface_parameter_value dm_agent isBigEndian {false}

set_instantiation_interface_parameter_value dm_agent isFlash {false}

set_instantiation_interface_parameter_value dm_agent isMemoryDevice {false}

set_instantiation_interface_parameter_value dm_agent isNonVolatileStorage {false}

set_instantiation_interface_parameter_value dm_agent linewrapBursts {false}

set_instantiation_interface_parameter_value dm_agent maximumPendingReadTransactions {2}

set_instantiation_interface_parameter_value dm_agent maximumPendingWriteTransactions {0}

set_instantiation_interface_parameter_value dm_agent minimumReadLatency {1}

set_instantiation_interface_parameter_value dm_agent minimumResponseLatency {1}

set_instantiation_interface_parameter_value dm_agent minimumUninterruptedRunLength {1}

set_instantiation_interface_parameter_value dm_agent prSafe {false}

set_instantiation_interface_parameter_value dm_agent printableDevice {false}

set_instantiation_interface_parameter_value dm_agent readLatency {0}

set_instantiation_interface_parameter_value dm_agent readWaitStates {1}

set_instantiation_interface_parameter_value dm_agent readWaitTime {1}

set_instantiation_interface_parameter_value dm_agent registerIncomingSignals {false}

set_instantiation_interface_parameter_value dm_agent registerOutgoingSignals {false}

set_instantiation_interface_parameter_value dm_agent setupTime {0}

set_instantiation_interface_parameter_value dm_agent timingUnits {Cycles}

set_instantiation_interface_parameter_value dm_agent transparentBridge {false}

set_instantiation_interface_parameter_value dm_agent waitrequestAllowance {0}

set_instantiation_interface_parameter_value dm_agent wellBehavedWaitrequest {false}

set_instantiation_interface_parameter_value dm_agent writeLatency {0}

set_instantiation_interface_parameter_value dm_agent writeWaitStates {0}

set_instantiation_interface_parameter_value dm_agent writeWaitTime {0}

set_instantiation_interface_assignment_value dm_agent embeddedsw.configuration.isFlash {0}

set_instantiation_interface_assignment_value dm_agent embeddedsw.configuration.isMemoryDevice {0}

set_instantiation_interface_assignment_value dm_agent embeddedsw.configuration.isNonVolatileStorage {0}

set_instantiation_interface_assignment_value dm_agent embeddedsw.configuration.isPrintableDevice {0}

set_instantiation_interface_assignment_value dm_agent qsys.ui.connect {instruction_manager,data_manager}

set_instantiation_interface_sysinfo_parameter_value dm_agent address_map {<address-map><slave name='dm_agent' start='0x0' end='0x10000' datawidth='32' /></address-map>}

set_instantiation_interface_sysinfo_parameter_value dm_agent address_width {16}

set_instantiation_interface_sysinfo_parameter_value dm_agent max_slave_data_width {32}

add_instantiation_interface_port dm_agent dm_agent_write write 1 STD_LOGIC Input

add_instantiation_interface_port dm_agent dm_agent_writedata writedata 32 STD_LOGIC_VECTOR Input

add_instantiation_interface_port dm_agent dm_agent_address address 16 STD_LOGIC_VECTOR Input

add_instantiation_interface_port dm_agent dm_agent_read read 1 STD_LOGIC Input

add_instantiation_interface_port dm_agent dm_agent_readdata readdata 32 STD_LOGIC_VECTOR Output

add_instantiation_interface_port dm_agent dm_agent_readdatavalid readdatavalid 1 STD_LOGIC Output

add_instantiation_interface_port dm_agent dm_agent_waitrequest waitrequest 1 STD_LOGIC Output

add_instantiation_interface dbg_reset reset OUTPUT

set_instantiation_interface_parameter_value dbg_reset associatedClock {clk}

set_instantiation_interface_parameter_value dbg_reset associatedDirectReset {}

set_instantiation_interface_parameter_value dbg_reset associatedResetSinks {none}

set_instantiation_interface_parameter_value dbg_reset synchronousEdges {DEASSERT}

add_instantiation_interface_port dbg_reset dbg_reset_reset reset 1 STD_LOGIC Output

save_instantiation

add_component sys_cpu_ram ip/sys/sys_cpu_ram.ip intel_onchip_memory sys_cpu_ram 1.3.0

load_component sys_cpu_ram

set_component_parameter_value AXI_interface {1}

set_component_parameter_value allowInSystemMemoryContentEditor {0}

set_component_parameter_value blockType {AUTO}

set_component_parameter_value clockEnable {0}

set_component_parameter_value copyInitFile {0}

set_component_parameter_value dataWidth {32}

set_component_parameter_value dataWidth2 {32}

set_component_parameter_value dualPort {0}

set_component_parameter_value enPRInitMode {0}

set_component_parameter_value enableDiffWidth {0}

set_component_parameter_value gui_debugaccess {0}

set_component_parameter_value idWidth {1}

set_component_parameter_value initMemContent {1}

set_component_parameter_value initializationFileName {software/app/build/app.hex}

set_component_parameter_value instanceID {NONE}

set_component_parameter_value interfaceType {0}

set_component_parameter_value lvl1OutputRegA {0}

set_component_parameter_value lvl1OutputRegB {0}

set_component_parameter_value lvl2OutputRegA {0}

set_component_parameter_value lvl2OutputRegB {0}

set_component_parameter_value memorySize {2000000.0}

set_component_parameter_value readDuringWriteMode_Mixed {DONT_CARE}

set_component_parameter_value resetrequest_enabled {1}

set_component_parameter_value singleClockOperation {0}

set_component_parameter_value tightly_coupled_ecc {0}

set_component_parameter_value useNonDefaultInitFile {1}

set_component_parameter_value writable {1}

set_component_project_property HIDE_FROM_IP_CATALOG {false}

save_component

load_instantiation sys_cpu_ram

remove_instantiation_interfaces_and_ports

set_instantiation_assignment_value embeddedsw.CMacro.ALLOW_IN_SYSTEM_MEMORY_CONTENT_EDITOR {0}

set_instantiation_assignment_value embeddedsw.CMacro.CONTENTS_INFO {""}

set_instantiation_assignment_value embeddedsw.CMacro.DUAL_PORT {0}

set_instantiation_assignment_value embeddedsw.CMacro.GUI_RAM_BLOCK_TYPE {AUTO}

set_instantiation_assignment_value embeddedsw.CMacro.INIT_CONTENTS_FILE {app}

set_instantiation_assignment_value embeddedsw.CMacro.INIT_MEM_CONTENT {1}

set_instantiation_assignment_value embeddedsw.CMacro.INSTANCE_ID {NONE}

set_instantiation_assignment_value embeddedsw.CMacro.NON_DEFAULT_INIT_FILE_ENABLED {1}

set_instantiation_assignment_value embeddedsw.CMacro.RAM_BLOCK_TYPE {AUTO}

set_instantiation_assignment_value embeddedsw.CMacro.READ_DURING_WRITE_MODE {DONT_CARE}

set_instantiation_assignment_value embeddedsw.CMacro.SINGLE_CLOCK_OP {0}

set_instantiation_assignment_value embeddedsw.CMacro.SIZE_MULTIPLE {1}

set_instantiation_assignment_value embeddedsw.CMacro.SIZE_VALUE {2000000}

set_instantiation_assignment_value embeddedsw.CMacro.WRITABLE {1}

set_instantiation_assignment_value embeddedsw.memoryInfo.DAT_SYM_INSTALL_DIR {SIM_DIR}

set_instantiation_assignment_value embeddedsw.memoryInfo.GENERATE_DAT_SYM {1}

set_instantiation_assignment_value embeddedsw.memoryInfo.GENERATE_HEX {1}

set_instantiation_assignment_value embeddedsw.memoryInfo.HAS_BYTE_LANE {0}

set_instantiation_assignment_value embeddedsw.memoryInfo.HEX_INSTALL_DIR {QPF_DIR}

set_instantiation_assignment_value embeddedsw.memoryInfo.MEM_INIT_DATA_WIDTH {32}

set_instantiation_assignment_value embeddedsw.memoryInfo.MEM_INIT_FILENAME {app}

set_instantiation_assignment_value postgeneration.simulation.init_file.param_name {INIT_FILE}

set_instantiation_assignment_value postgeneration.simulation.init_file.type {MEM_INIT}

add_instantiation_interface clk1 clock INPUT

set_instantiation_interface_parameter_value clk1 clockRate {0}

set_instantiation_interface_parameter_value clk1 externallyDriven {false}

set_instantiation_interface_parameter_value clk1 ptfSchematicName {}

add_instantiation_interface_port clk1 clk clk 1 STD_LOGIC Input

add_instantiation_interface s1 avalon INPUT

set_instantiation_interface_parameter_value s1 addressAlignment {DYNAMIC}

set_instantiation_interface_parameter_value s1 addressGroup {0}

set_instantiation_interface_parameter_value s1 addressSpan {2000000}

set_instantiation_interface_parameter_value s1 addressUnits {WORDS}

set_instantiation_interface_parameter_value s1 alwaysBurstMaxBurst {false}

set_instantiation_interface_parameter_value s1 associatedClock {clk1}

set_instantiation_interface_parameter_value s1 associatedReset {reset1}

set_instantiation_interface_parameter_value s1 bitsPerSymbol {8}

set_instantiation_interface_parameter_value s1 bridgedAddressOffset {0}

set_instantiation_interface_parameter_value s1 bridgesToMaster {}

set_instantiation_interface_parameter_value s1 burstOnBurstBoundariesOnly {false}

set_instantiation_interface_parameter_value s1 burstcountUnits {WORDS}

set_instantiation_interface_parameter_value s1 constantBurstBehavior {false}

set_instantiation_interface_parameter_value s1 explicitAddressSpan {2000000}

set_instantiation_interface_parameter_value s1 holdTime {0}

set_instantiation_interface_parameter_value s1 interleaveBursts {false}

set_instantiation_interface_parameter_value s1 isBigEndian {false}

set_instantiation_interface_parameter_value s1 isFlash {false}

set_instantiation_interface_parameter_value s1 isMemoryDevice {true}

set_instantiation_interface_parameter_value s1 isNonVolatileStorage {false}

set_instantiation_interface_parameter_value s1 linewrapBursts {false}

set_instantiation_interface_parameter_value s1 maximumPendingReadTransactions {0}

set_instantiation_interface_parameter_value s1 maximumPendingWriteTransactions {0}

set_instantiation_interface_parameter_value s1 minimumReadLatency {1}

set_instantiation_interface_parameter_value s1 minimumResponseLatency {1}

set_instantiation_interface_parameter_value s1 minimumUninterruptedRunLength {1}

set_instantiation_interface_parameter_value s1 prSafe {false}

set_instantiation_interface_parameter_value s1 printableDevice {false}

set_instantiation_interface_parameter_value s1 readLatency {1}

set_instantiation_interface_parameter_value s1 readWaitStates {0}

set_instantiation_interface_parameter_value s1 readWaitTime {0}

set_instantiation_interface_parameter_value s1 registerIncomingSignals {false}

set_instantiation_interface_parameter_value s1 registerOutgoingSignals {false}

set_instantiation_interface_parameter_value s1 setupTime {0}

set_instantiation_interface_parameter_value s1 timingUnits {Cycles}

set_instantiation_interface_parameter_value s1 transparentBridge {false}

set_instantiation_interface_parameter_value s1 waitrequestAllowance {0}

set_instantiation_interface_parameter_value s1 wellBehavedWaitrequest {false}

set_instantiation_interface_parameter_value s1 writeLatency {0}

set_instantiation_interface_parameter_value s1 writeWaitStates {0}

set_instantiation_interface_parameter_value s1 writeWaitTime {0}

set_instantiation_interface_assignment_value s1 embeddedsw.configuration.isFlash {0}

set_instantiation_interface_assignment_value s1 embeddedsw.configuration.isMemoryDevice {1}

set_instantiation_interface_assignment_value s1 embeddedsw.configuration.isNonVolatileStorage {0}

set_instantiation_interface_assignment_value s1 embeddedsw.configuration.isPrintableDevice {0}

set_instantiation_interface_sysinfo_parameter_value s1 address_map {<address-map><slave name='s1' start='0x0' end='0x1E8480' datawidth='32' /></address-map>}

set_instantiation_interface_sysinfo_parameter_value s1 address_width {21}

set_instantiation_interface_sysinfo_parameter_value s1 max_slave_data_width {32}

add_instantiation_interface_port s1 address address 19 STD_LOGIC_VECTOR Input

add_instantiation_interface_port s1 read read 1 STD_LOGIC Input

add_instantiation_interface_port s1 readdata readdata 32 STD_LOGIC_VECTOR Output

add_instantiation_interface_port s1 byteenable byteenable 4 STD_LOGIC_VECTOR Input

add_instantiation_interface_port s1 write write 1 STD_LOGIC Input

add_instantiation_interface_port s1 writedata writedata 32 STD_LOGIC_VECTOR Input

add_instantiation_interface reset1 reset INPUT

set_instantiation_interface_parameter_value reset1 associatedClock {clk1}

set_instantiation_interface_parameter_value reset1 synchronousEdges {DEASSERT}

add_instantiation_interface_port reset1 reset reset 1 STD_LOGIC Input

add_instantiation_interface_port reset1 reset_req reset_req 1 STD_LOGIC Input

save_instantiation

add_component sys_e_tile ip/sys/sys_alt_ehipc3_fm_0.ip alt_ehipc3_fm alt_ehipc3_fm_0 21.0.0

load_component sys_e_tile

set_component_parameter_value AIB_test_sl {0}

set_component_parameter_value AN_CHAN {0}

set_component_parameter_value AN_PAUSE_C0 {1}

set_component_parameter_value AN_PAUSE_C1 {1}

set_component_parameter_value AVMM_test {0}

set_component_parameter_value AVMM_test_sl {0}

set_component_parameter_value CR_MODE {1}

set_component_parameter_value DEV_BOARD {0}

set_component_parameter_value EHIP_LOCATION {0}

set_component_parameter_value ENABLE_ADME {1}

set_component_parameter_value ENABLE_ADME_PTP_CHANNEL {0}

set_component_parameter_value ENABLE_AN {1}

set_component_parameter_value ENABLE_ANLT {0}

set_component_parameter_value ENABLE_ASYNC_ADAPTERS {0}

set_component_parameter_value ENABLE_ASYNC_ADAPTERS_SL {0}

set_component_parameter_value ENABLE_JTAG_AVMM {0}

set_component_parameter_value ENABLE_LT {1}

set_component_parameter_value ENABLE_PPM_TODSYNC {1}

set_component_parameter_value ENABLE_PTP {0}

set_component_parameter_value ENABLE_PTP_PPM {0}

set_component_parameter_value ENABLE_PTP_RX_DESKEW {1}

set_component_parameter_value ENABLE_PTP_TOG {0}

set_component_parameter_value ENABLE_RSFEC {1}

set_component_parameter_value ENABLE_SYNCE {0}

set_component_parameter_value ENHANCED_PTP_ACCURACY {0}

set_component_parameter_value ENHANCED_PTP_DBG {0}

set_component_parameter_value EN_DYN_FEC {0}

set_component_parameter_value EXAMPLE_DESIGN {1}

set_component_parameter_value GEN_SIM {1}

set_component_parameter_value GEN_SYNTH {1}

set_component_parameter_value HDL_FORMAT {1}

set_component_parameter_value LINK_TIMER_KR {504}

set_component_parameter_value PHY_REFCLK {156.250000}

set_component_parameter_value PHY_REFCLK_sl_0 {156.250000}

set_component_parameter_value PPM_VALUE_RX {0}

set_component_parameter_value PPM_VALUE_TX {0}

set_component_parameter_value RECONFIG_1025 {0}

set_component_parameter_value REQUEST_RSFEC {1}

set_component_parameter_value RSFEC_CLOCKING_MODE {fec_dir_adp_clk_0}

set_component_parameter_value RSFEC_FIRST_LANE_SEL {first_lane0}

set_component_parameter_value SL_OPT {2}

set_component_parameter_value STATUS_CLK_MHZ {100.0}

set_component_parameter_value USE_PTP_PLLCH {1}

set_component_parameter_value XCVR_test {0}

set_component_parameter_value active_channel {0}

set_component_parameter_value additional_ipg_removed {0}

set_component_parameter_value additional_ipg_removed_sl_0 {0}

set_component_parameter_value adpt_multi_enable {1}

set_component_parameter_value adpt_recipe_cnt {1}

set_component_parameter_value adpt_recipe_data0 {}

set_component_parameter_value adpt_recipe_data1 {}

set_component_parameter_value adpt_recipe_data2 {}

set_component_parameter_value adpt_recipe_data3 {}

set_component_parameter_value adpt_recipe_data4 {}

set_component_parameter_value adpt_recipe_data5 {}

set_component_parameter_value adpt_recipe_data6 {}

set_component_parameter_value adpt_recipe_data7 {}

set_component_parameter_value adpt_recipe_select {0}

set_component_parameter_value cal_recipe_sel {NRZ_28Gbps_VSR}

set_component_parameter_value core_variant {2}

set_component_parameter_value cpri_ehip_rate_gui {2}

set_component_parameter_value cpri_enable_custom_sl_0 {1}

set_component_parameter_value cpri_include_alternate_ports {0}

set_component_parameter_value cpri_include_refclk_mux_sl_0 {0}

set_component_parameter_value cpri_number_of_channel {1}

set_component_parameter_value ctle_gs1_val_a {999}

set_component_parameter_value ctle_gs1_val_b {999}

set_component_parameter_value ctle_gs2_val_a {999}

set_component_parameter_value ctle_gs2_val_b {999}

set_component_parameter_value ctle_hf_max_a {999}

set_component_parameter_value ctle_hf_max_b {999}

set_component_parameter_value ctle_hf_min_a {999}

set_component_parameter_value ctle_hf_min_b {999}

set_component_parameter_value ctle_hf_val_a {999}

set_component_parameter_value ctle_hf_val_ada_a {adaptable}

set_component_parameter_value ctle_hf_val_ada_b {adaptable}

set_component_parameter_value ctle_hf_val_b {999}

set_component_parameter_value ctle_lf_max_a {999}

set_component_parameter_value ctle_lf_max_b {999}

set_component_parameter_value ctle_lf_min_a {999}

set_component_parameter_value ctle_lf_min_b {999}

set_component_parameter_value ctle_lf_val_a {999}

set_component_parameter_value ctle_lf_val_ada_a {adaptable}

set_component_parameter_value ctle_lf_val_ada_b {adaptable}

set_component_parameter_value ctle_lf_val_b {999}

set_component_parameter_value custom_pcs_PHY_REFCLK {250.000000}

set_component_parameter_value custom_pcs_ehip_mode_gui {PCS_Only}

set_component_parameter_value custom_pcs_ehip_rate_gui {25000}

set_component_parameter_value custom_pcs_enable_custom {1}

set_component_parameter_value custom_pcs_fibre_channel_mode {disable}

set_component_parameter_value custom_pcs_include_alternate_ports {0}

set_component_parameter_value custom_pcs_modulation {NRZ}

set_component_parameter_value custom_pcs_number_of_channel {1}

set_component_parameter_value design_environment {QSYS}

set_component_parameter_value dis_anlt_std_recipe {0}

set_component_parameter_value disable_internal_dr {0}

set_component_parameter_value dr_100g_nrz_pam4 {0}

set_component_parameter_value dr_25g_cpri {0}

set_component_parameter_value duplex_mode {enable}

set_component_parameter_value ehip_mode_gui {MAC+PCS+(528,514)RSFEC}

set_component_parameter_value ehip_mode_gui_sl_0 {MAC+PCS+RSFEC}

set_component_parameter_value ehip_rate_gui {100G}

set_component_parameter_value ehip_rate_gui_sl_0 {25G}

set_component_parameter_value enable_aib_latency_adj_ena_ports {0}

set_component_parameter_value enable_custom_sl_0 {0}

set_component_parameter_value enable_external_aib_clocking {0}

set_component_parameter_value enable_internal_options {0}

set_component_parameter_value enable_rsfec_rst_ports {0}

set_component_parameter_value enforce_max_frame_size_gui {0}

set_component_parameter_value enforce_max_frame_size_gui_sl_0 {0}

set_component_parameter_value flow_control_gui {No}

set_component_parameter_value flow_control_gui_sl_0 {No}

set_component_parameter_value forward_rx_pause_requests_gui {0}

set_component_parameter_value forward_rx_pause_requests_gui_sl_0 {0}

set_component_parameter_value include_alternate_ports_sl_0 {0}

set_component_parameter_value include_dlat_sl_0 {0}

set_component_parameter_value include_refclk_mux_sl_0 {0}

set_component_parameter_value link_fault_mode_gui {Bidirectional}

set_component_parameter_value link_fault_mode_gui_sl_0 {Bidirectional}

set_component_parameter_value number_of_channel {0}

set_component_parameter_value preamble_passthrough_gui {0}

set_component_parameter_value preamble_passthrough_gui_sl_0 {0}

set_component_parameter_value preserve_unused_xcvr_channels {0}

set_component_parameter_value rcp_load_enable {0}

set_component_parameter_value ready_latency {0}

set_component_parameter_value ready_latency_sl {0}

set_component_parameter_value rf_a_a {999}

set_component_parameter_value rf_a_b {999}

set_component_parameter_value rf_b0_a {999}

set_component_parameter_value rf_b0_ada_a {adaptable}

set_component_parameter_value rf_b0_ada_b {adaptable}

set_component_parameter_value rf_b0_b {999}

set_component_parameter_value rf_b0t_a {999}

set_component_parameter_value rf_b0t_b {999}

set_component_parameter_value rf_b1_a {999}

set_component_parameter_value rf_b1_ada_a {adaptable}

set_component_parameter_value rf_b1_ada_b {adaptable}

set_component_parameter_value rf_b1_b {999}

set_component_parameter_value rf_p0_val_a {999}

set_component_parameter_value rf_p0_val_ada_a {adaptable}

set_component_parameter_value rf_p0_val_ada_b {adaptable}

set_component_parameter_value rf_p0_val_b {999}

set_component_parameter_value rf_p1_max_a {999}

set_component_parameter_value rf_p1_max_b {999}

set_component_parameter_value rf_p1_min_a {999}

set_component_parameter_value rf_p1_min_b {999}

set_component_parameter_value rf_p1_val_a {999}

set_component_parameter_value rf_p1_val_ada_a {adaptable}

set_component_parameter_value rf_p1_val_ada_b {adaptable}

set_component_parameter_value rf_p1_val_b {999}

set_component_parameter_value rf_p2_max_a {999}

set_component_parameter_value rf_p2_max_b {999}

set_component_parameter_value rf_p2_min_a {999}

set_component_parameter_value rf_p2_min_b {999}

set_component_parameter_value rf_p2_val_a {999}

set_component_parameter_value rf_p2_val_ada_a {adaptable}

set_component_parameter_value rf_p2_val_ada_b {adaptable}

set_component_parameter_value rf_p2_val_b {999}

set_component_parameter_value rf_reserved0_a {999}

set_component_parameter_value rf_reserved0_b {999}

set_component_parameter_value rf_reserved1_a {999}

set_component_parameter_value rf_reserved1_b {999}

set_component_parameter_value rx_bytes_to_remove {Remove CRC bytes}

set_component_parameter_value rx_bytes_to_remove_sl_0 {Remove CRC bytes}

set_component_parameter_value rx_max_frame_size_gui {1518}

set_component_parameter_value rx_max_frame_size_gui_sl_0 {1518}

set_component_parameter_value rx_vlan_detection_gui {1}

set_component_parameter_value rx_vlan_detection_gui_sl_0 {1}

set_component_parameter_value source_address_insertion_gui {0}

set_component_parameter_value source_address_insertion_gui_sl_0 {0}

set_component_parameter_value strict_preamble_checking_gui {0}

set_component_parameter_value strict_preamble_checking_gui_sl_0 {0}

set_component_parameter_value strict_sfd_checking_gui {0}

set_component_parameter_value strict_sfd_checking_gui_sl_0 {0}

set_component_parameter_value tx_ipg_size_gui {12}

set_component_parameter_value tx_ipg_size_gui_sl_0 {12}

set_component_parameter_value tx_max_frame_size_gui {1518}

set_component_parameter_value tx_max_frame_size_gui_sl_0 {1518}

set_component_parameter_value tx_vlan_detection_gui {1}

set_component_parameter_value tx_vlan_detection_gui_sl_0 {1}

set_component_parameter_value txmac_saddr_gui {73588229205}

set_component_parameter_value user_bti_refclk_freq_mhz {156.250000}

set_component_project_property HIDE_FROM_IP_CATALOG {false}

save_component

load_instantiation sys_e_tile

remove_instantiation_interfaces_and_ports

add_instantiation_interface i_stats_snapshot conduit INPUT

set_instantiation_interface_parameter_value i_stats_snapshot associatedClock {}

set_instantiation_interface_parameter_value i_stats_snapshot associatedReset {}

set_instantiation_interface_parameter_value i_stats_snapshot prSafe {false}

add_instantiation_interface_port i_stats_snapshot i_stats_snapshot i_stats_snapshot 1 STD_LOGIC Input

add_instantiation_interface o_cdr_lock conduit INPUT

set_instantiation_interface_parameter_value o_cdr_lock associatedClock {}

set_instantiation_interface_parameter_value o_cdr_lock associatedReset {}

set_instantiation_interface_parameter_value o_cdr_lock prSafe {false}

add_instantiation_interface_port o_cdr_lock o_cdr_lock o_cdr_lock 1 STD_LOGIC_VECTOR Output

add_instantiation_interface o_tx_pll_locked conduit INPUT

set_instantiation_interface_parameter_value o_tx_pll_locked associatedClock {}

set_instantiation_interface_parameter_value o_tx_pll_locked associatedReset {}

set_instantiation_interface_parameter_value o_tx_pll_locked prSafe {false}

add_instantiation_interface_port o_tx_pll_locked o_tx_pll_locked o_tx_pll_locked 1 STD_LOGIC_VECTOR Output

add_instantiation_interface eth_reconfig avalon INPUT

set_instantiation_interface_parameter_value eth_reconfig addressAlignment {DYNAMIC}

set_instantiation_interface_parameter_value eth_reconfig addressGroup {0}

set_instantiation_interface_parameter_value eth_reconfig addressSpan {8388608}

set_instantiation_interface_parameter_value eth_reconfig addressUnits {WORDS}

set_instantiation_interface_parameter_value eth_reconfig alwaysBurstMaxBurst {false}

set_instantiation_interface_parameter_value eth_reconfig associatedClock {i_reconfig_clk}

set_instantiation_interface_parameter_value eth_reconfig associatedReset {i_reconfig_reset}

set_instantiation_interface_parameter_value eth_reconfig bitsPerSymbol {8}

set_instantiation_interface_parameter_value eth_reconfig bridgedAddressOffset {0}

set_instantiation_interface_parameter_value eth_reconfig bridgesToMaster {}

set_instantiation_interface_parameter_value eth_reconfig burstOnBurstBoundariesOnly {false}

set_instantiation_interface_parameter_value eth_reconfig burstcountUnits {WORDS}

set_instantiation_interface_parameter_value eth_reconfig constantBurstBehavior {false}

set_instantiation_interface_parameter_value eth_reconfig explicitAddressSpan {0}

set_instantiation_interface_parameter_value eth_reconfig holdTime {0}

set_instantiation_interface_parameter_value eth_reconfig interleaveBursts {false}

set_instantiation_interface_parameter_value eth_reconfig isBigEndian {false}

set_instantiation_interface_parameter_value eth_reconfig isFlash {false}

set_instantiation_interface_parameter_value eth_reconfig isMemoryDevice {false}

set_instantiation_interface_parameter_value eth_reconfig isNonVolatileStorage {false}

set_instantiation_interface_parameter_value eth_reconfig linewrapBursts {false}

set_instantiation_interface_parameter_value eth_reconfig maximumPendingReadTransactions {1}

set_instantiation_interface_parameter_value eth_reconfig maximumPendingWriteTransactions {0}

set_instantiation_interface_parameter_value eth_reconfig minimumReadLatency {1}

set_instantiation_interface_parameter_value eth_reconfig minimumResponseLatency {1}

set_instantiation_interface_parameter_value eth_reconfig minimumUninterruptedRunLength {1}

set_instantiation_interface_parameter_value eth_reconfig prSafe {false}

set_instantiation_interface_parameter_value eth_reconfig printableDevice {false}

set_instantiation_interface_parameter_value eth_reconfig readLatency {0}

set_instantiation_interface_parameter_value eth_reconfig readWaitStates {1}

set_instantiation_interface_parameter_value eth_reconfig readWaitTime {1}

set_instantiation_interface_parameter_value eth_reconfig registerIncomingSignals {false}

set_instantiation_interface_parameter_value eth_reconfig registerOutgoingSignals {false}

set_instantiation_interface_parameter_value eth_reconfig setupTime {0}

set_instantiation_interface_parameter_value eth_reconfig timingUnits {Cycles}

set_instantiation_interface_parameter_value eth_reconfig transparentBridge {false}

set_instantiation_interface_parameter_value eth_reconfig waitrequestAllowance {0}

set_instantiation_interface_parameter_value eth_reconfig wellBehavedWaitrequest {false}

set_instantiation_interface_parameter_value eth_reconfig writeLatency {0}

set_instantiation_interface_parameter_value eth_reconfig writeWaitStates {0}

set_instantiation_interface_parameter_value eth_reconfig writeWaitTime {0}

set_instantiation_interface_assignment_value eth_reconfig embeddedsw.configuration.isFlash {0}

set_instantiation_interface_assignment_value eth_reconfig embeddedsw.configuration.isMemoryDevice {0}

set_instantiation_interface_assignment_value eth_reconfig embeddedsw.configuration.isNonVolatileStorage {0}

set_instantiation_interface_assignment_value eth_reconfig embeddedsw.configuration.isPrintableDevice {0}

set_instantiation_interface_sysinfo_parameter_value eth_reconfig address_map {<address-map><slave name='eth_reconfig' start='0x0' end='0x800000' datawidth='32' /></address-map>}

set_instantiation_interface_sysinfo_parameter_value eth_reconfig address_width {23}