経済安全保障を見据えた(純国産または調達性のある)ドローンの周辺技術調査(日記)

はじめに:この記事の執筆背景

最近、ドローンが戦場やニュースに登場することが多くなりましたが、「果たして今の日本は、これをゼロから自分たちで作れるんだっけ?」という単純な疑問と、「もし海外から部品が入らなくなって『作れない』事態になれば、国家として大変なことになるかもしれない」という強い危機感から調べ、考えたエンジニアの「日記」です。

1. 序論およびドローンアーキテクチャの進化

無人航空機(UAV)、とりわけマルチコプター型のドローンシステムは、過去十年間でホビー用の玩具から、防衛、重要インフラ点検、災害対応、および高度な空間データ収集を担う産業用エッジコンピューティングプラットフォームへと急激な進化を遂げた。この進化の根底には、マイクロコントローラ(MCU)の演算能力の飛躍的な向上、MEMSセンサーの小型化、そして制御アルゴリズムの高度化が存在する。

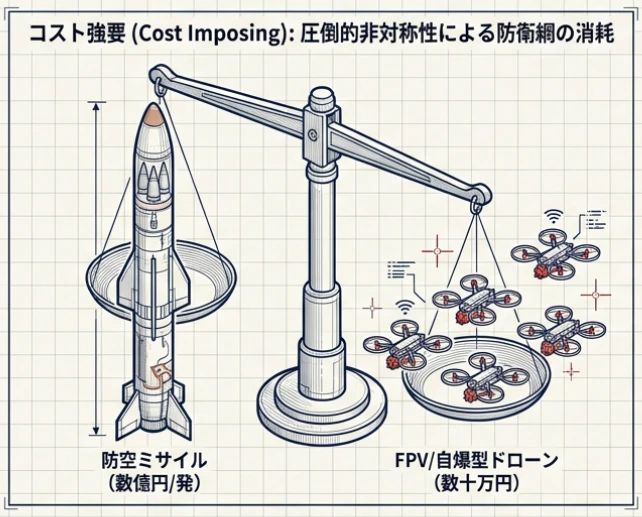

昨今の国際情勢において、我々はテクノロジーがもたらす残酷なまでの「非対称戦」を目の当たりにしている。わずか数十万円の自爆型ドローンを阻止するために、防衛側は一発数億円の防空ミサイルを消費せざるを得ない。あるいは、安価なFPVドローンが、その数万倍のコストを投じた主力戦車を破壊する。この圧倒的なコストパフォーマンスの格差は、従来の軍事バランスを根底から覆し、防衛側を経済的・物量的に疲弊させる「コスト・インポーズ(費用強要)」戦略として機能している。

一技術者として、こうした技術が実戦で投入される日が来ないことを切に願う。しかし同時に、地政学的リスクが顕在化した際、「喉から手が出るほど欲しくても、供給網が遮断され、海外製コンポーネントが一切手に入らない」という事態は、国家の存立を左右する致命的な脆弱性となり得る。この懸念は、単なる杞憂ではなく、日本の技術的自立(テクノロジー・ソブリンティ)を問う重大な問いである。

果たして、我々日本は、自律飛行システムの核心部を自らの手でゼロから構築し、防衛・インフラ・経済安全保障を担保し得る「純国産ドローン」を生み出すことができるのか。本調査はこの切実な問いを出発点とし、既存のグローバル・コモディティ技術を単に模倣するのではなく、次世代の制御言語や多重化通信といった周辺技術を統合し、真に強靭な国産システムを確立するための技術的要件を浮き彫りにすることを目的とする。

本記事では、ドローンシステムの基盤となるハードウェアの物理的特性から出発し、その中核をなすフライトコントローラ(FC)のソフトウェアアーキテクチャ、次世代のシステムプログラミング言語であるRustを用いた高信頼性制御系の設計、さらには5G/LTEや衛星通信を統合するマルチリンク通信ネットワークの構築手法に至るまでを網羅的に分析する。また、運用上の法規制と、経済安全保障の観点からみた純国産ハードウェアの重要性についても詳細な検証を行う。

2. ドローンシステムの物理層と動力変換メカニズム

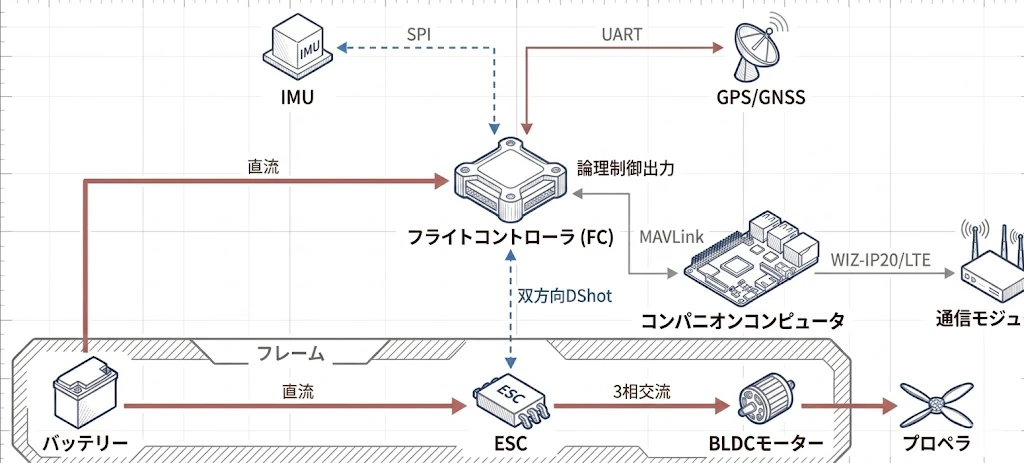

高度なソフトウェア制御を論じる前に、システムが全体としてどのような物理的・電子的コンポーネントによって構成されているかを俯瞰することが重要である。一般的な高度自律飛行ドローン(マルチコプター)を構成する主要なハードウェア要素(Consists of)を以下の表に示す。

| コンポーネント名 | 主要な役割とアーキテクチャ上の位置づけ | 記事内での関連・技術的要件 |

|---|---|---|

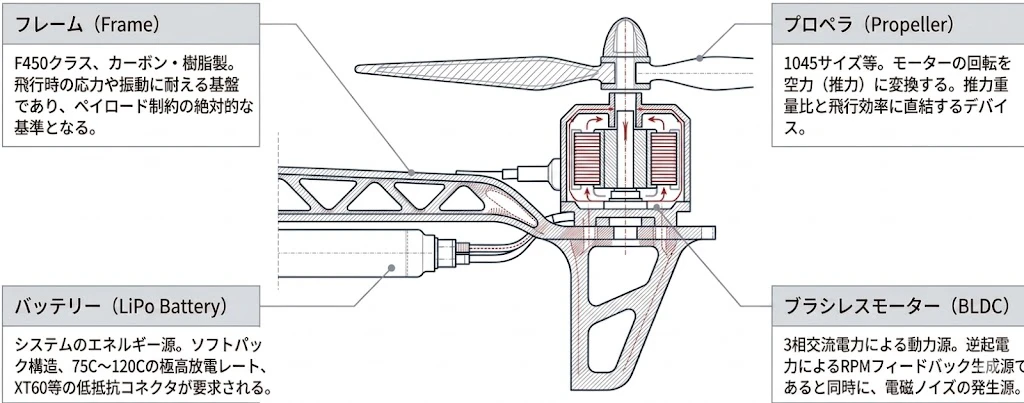

| フレーム (Frame) | 機体の骨格。各コンポーネントを固定し、飛行時の応力や振動に耐える物理層の基盤。 | F450/F550クラス、カーボン・樹脂製。ペイロード制約の基準となる。 |

| プロペラ (Propeller) | モーターの回転を推力(揚力)に変換する空力デバイス。 | 1045サイズ等。推力重量比と飛行効率に直結する。 |

| ブラシレスモーター (BLDC) | ESCからの3相交流電力により駆動し、プロペラを回転させる動力源。 | 逆起電力によるRPMフィードバック生成源。電磁ノイズの発生源でもある。 |

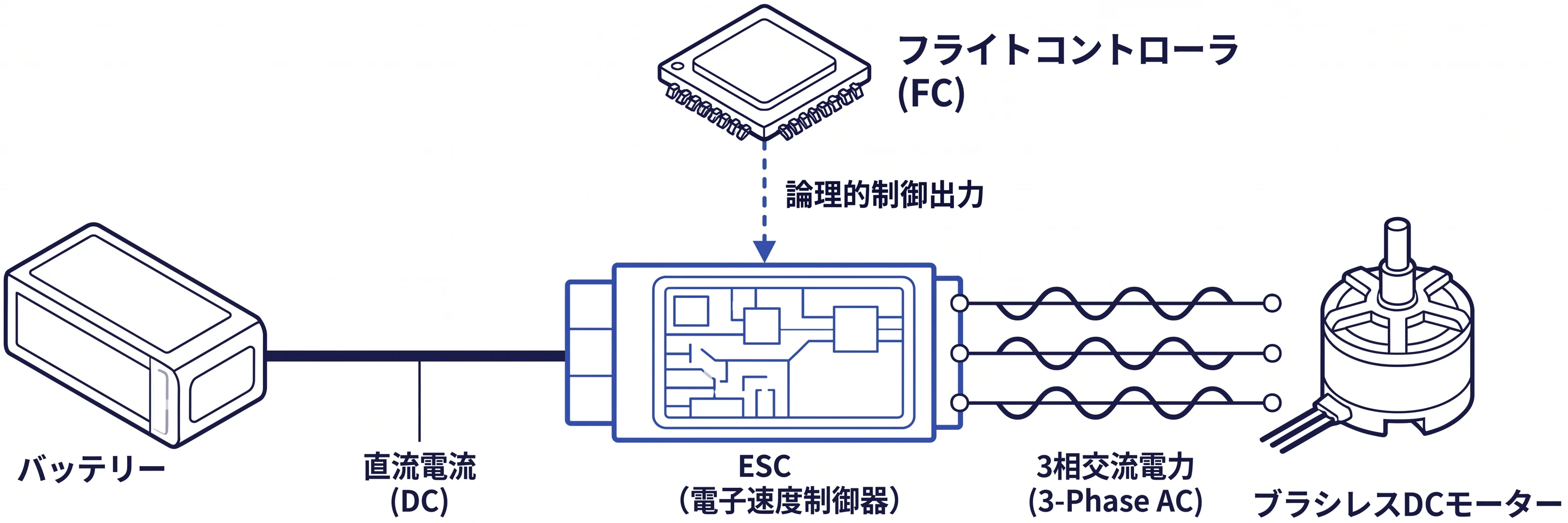

| ESC (Electronic Speed Controller) | FCからのデジタル指令を受け、直流電力を3相交流に変換しモーターを駆動する。 | 双方向DShotによる完全デジタル通信、RPMフィルタリングのためのデータ生成。 |

| フライトコントローラ (FC) | 機体の姿勢制御、センサーフュージョン、自律航法を司るシステムの「小脳・脊髄」。 | 32bit MCU、ベアメタルRust実装、ArduPilot、高信頼性の純国産基板(JAE JFB-100等)。 |

| GPS/GNSSアンテナ | 衛星信号を受信し、絶対的な自己位置(緯度・経度・高度)と速度ベクトルをFCに提供する。 | UART経由でFCと接続。EKFにおける相対誤差(ドリフト)の補正に必須。 |

| IMU (慣性計測装置) | 角速度(ジャイロ)と加速度を極めて高速に計測する。通常FC基板に内蔵される。 | SPI通信による超高速データの提供。EKFによる姿勢推定の主たる計算リソース。 |

| バッテリー (LiPo Battery) | システム全体へ電力を供給するエネルギー源。極めて高いエネルギー密度と放電能力が求められる。 | ソフトパック構造、75C〜120Cの極高放電レート、XT60等の低抵抗コネクタ。 |

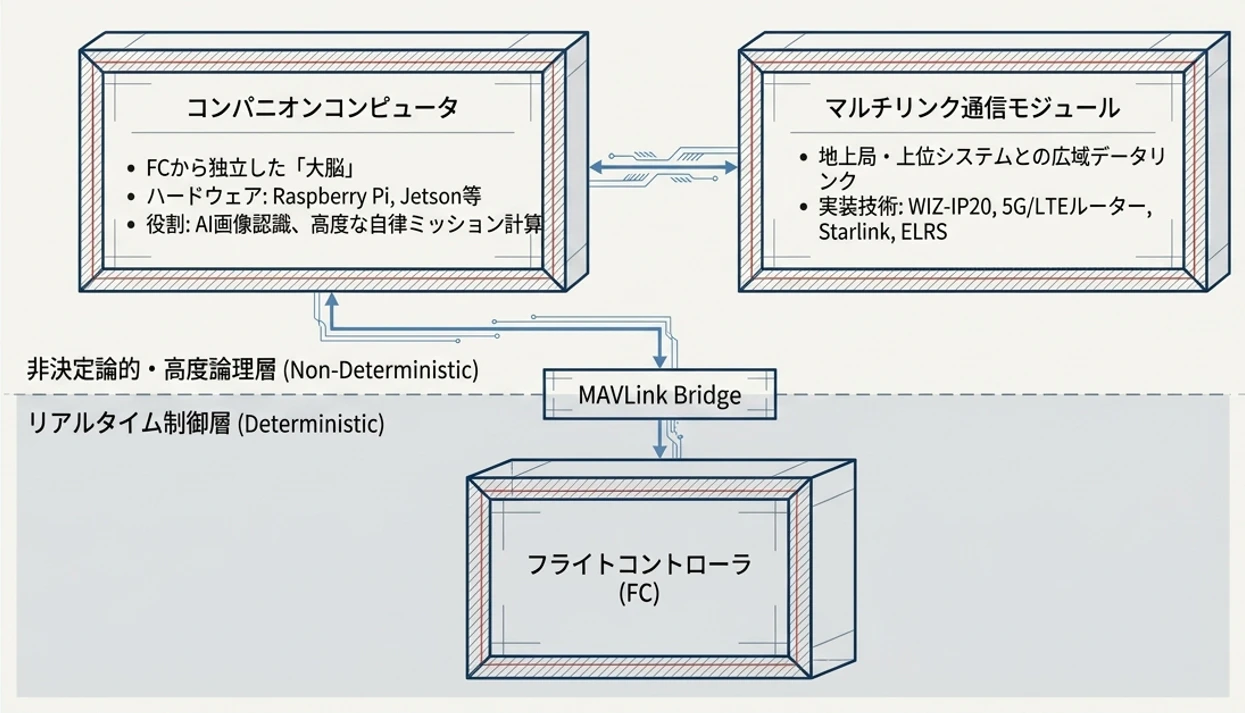

| コンパニオンコンピュータ | FCの制御系とは独立し、AI画像認識や高度なネットワークルーティングを行う「大脳」。 | Raspberry Pi、Jetson等。MAVLinkプロトコル経由でFCと論理的に通信。 |

| マルチリンク通信モジュール | 地上局や上位ネットワークとの広域データリンクを確立する統合通信基盤。 | WIZ-IP20(LAN-UART変換)、5G/LTEルーター、Starlink端末、ELRS受信機等。 |

システムが依存するこれら物理レイヤーの限界(電源供給メカニズム、推進システムの流体力学的および電気力学的特性、機体のペイロード制約)を完全に理解することが不可欠である。これら物理レイヤーの限界が、最終的なソフトウェアの実行可能領域を決定づけるからである。

2.1 エネルギー密度の要求と電源供給設計の相違

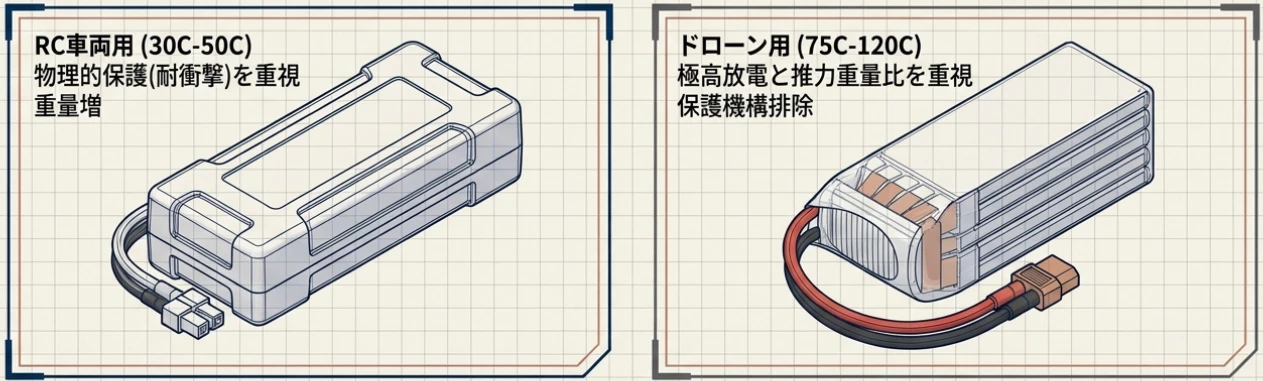

ドローンと陸上を走行するRC(ラジコン)車両とでは、動力源に求められる設計思想と物理的制約が根本的に異なる。両者ともにリチウムポリマー(LiPo)電池が広く使用されているものの、その内部構造とパッケージングには明確な差異が存在する。

陸上車両用のバッテリーは、転倒や衝突といった物理的衝撃から内部のセルを保護するため、プラスチック製の堅牢なハードケースに格納されていることが一般的である。このハードケースは重量の増加を招くが、接地して走行する車両にとっては致命的な欠点とはならない。対して、ドローンにおいて重量は推力重量比(Thrust-to-Weight Ratio)に直結する最もクリティカルなパラメータである。1グラムの重量増加が飛行時間の短縮や運動性能の低下に直結するため、ドローン用バッテリーは極限まで軽量化を図るべく、薄い熱収縮フィルム(シュリンクチューブ)のみでセルを保護したソフトパック構造が主流となっている。

さらに、電気的特性の面でも大きな違いがある。マルチコプターは、機体を空中に保持し続けるために4基以上のブラシレスモーターを同時に高速駆動する。突風への対応や急激な姿勢変化を行う際、システムは瞬間的に数十アンペアから百アンペアを超える膨大な電流を要求する。RCカー用バッテリーの放電能力(Cレート)が一般的に30Cから50C程度に設定されているのに対し、ドローン専用のバッテリーは75Cから120Cといった極めて高い急放電能力を持つように設計されている。能力不足のバッテリーをマルチコプターに流用した場合、モーターが要求する電力を供給しきれず、急激な電圧降下(Voltage Sag)を引き起こす。この電圧降下は、フライトコントローラのシャットダウンによる墜落を招くばかりか、過大な内部抵抗によるセルの異常発熱、膨張、最悪の場合は熱暴走による発火・爆発の危険性を伴う。したがって、大電流に耐えうるXT60やXT30といった低抵抗かつ大容量のコネクタの標準採用が必須条件となるのである。

2.2 動力変換メカニズム:ブラシレスモーターとESCの協調

フライトコントローラが演算した論理的な制御出力を、物理的な推力に変換する役割を担うのがESC(Electronic Speed Controller:電子速度制御器)である。ESCの役割は、バッテリーから供給される直流電流を、ブラシレスDC(BLDC)モーターを駆動するための3相交流電力に高速変換することである。

かつてのシステムでは、FCとESC間の通信にPWM(Pulse Width Modulation)やI2Cなどのプロトコルが使用されていた。しかし、モーター駆動時には数十アンペアの大電流が機体のアームに流れ、強烈な電磁ノイズ(EMI)が発生する。アナログ的なパルス幅で回転数を指示するPWMや、ノイズに弱いI2C通信では、この電磁ノイズによって信号が変調され、モーターの意図しない回転変動(ジッタ)を引き起こす原因となっていた。

| 特徴 | 従来方式 (PWM / ONESHOT / I2C) | 現代方式 (Bidirectional DShot) |

|---|---|---|

| 信号伝送形式 | アナログ(パルス幅) / 電圧変動の影響を受けやすい | 完全デジタル(16ビットパケット) / ノイズ耐性極高 |

| 通信速度と遅延 | 低速(数ミリ秒の遅延) | 極めて高速(DShot600で約26.7µs/パケット) |

| フィードバック機構 | 不可(オープンループ制御) | 可能(RPMデータによるクローズドループ制御) |

| ノイズフィルタリング | ハードウェアによる物理的防振に依存 | ソフトウェアによる動的RPMノッチフィルタリング |

現在の高度な機体制御においては、完全デジタルプロトコルである「DShot」がデファクトスタンダードとなっている。DShotは、指示値を16ビットのデジタルパケット(回転数データとCRCチェックサムを含む)として送信するため、電気的ノイズの影響を完全に排除できる。

さらに、近年では「双方向DShot(Bidirectional DShot)」という技術が実装され、飛行安定性が飛躍的に向上している。ブラシレスモーターの内部には、重量削減と信頼性向上のため、回転角を検知する物理的なホールセンサーが搭載されていない。その代わり、ESCはモーターが回転する際に生じる逆起電力(Back EMF)のパルス間隔を検知し、内蔵されたマイコンでリアルタイムに実際の回転数(RPM)を算出している。双方向DShotでは、FCから送られてくる制御信号のわずかな「隙間」を利用して、このRPMデータをFCへと送り返す。FC側は「指示した回転数」と「実際の回転数」の誤差を瞬時に把握することで、プロペラの接触異常を検知するだけでなく、特定のモーター回転周波数に起因する機体の機械的共振(ノイズ)をFC側で動的に計算し、打ち消す「RPMフィルタリング」を実行する。これにより、極めて高い姿勢安定性と滑らかな飛行特性が実現されるのである。

2.3 フレーム構造とペイロードの力学的な制約

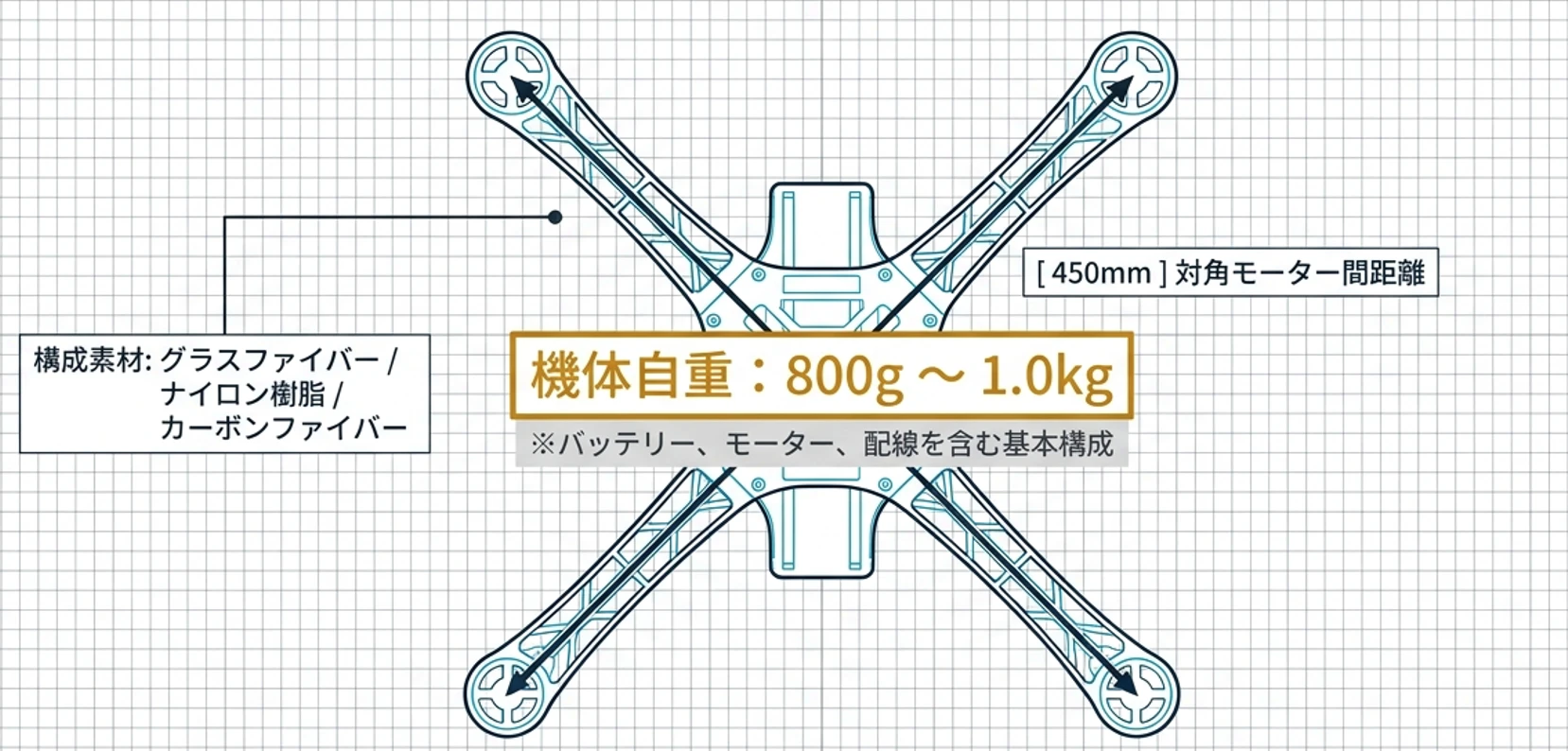

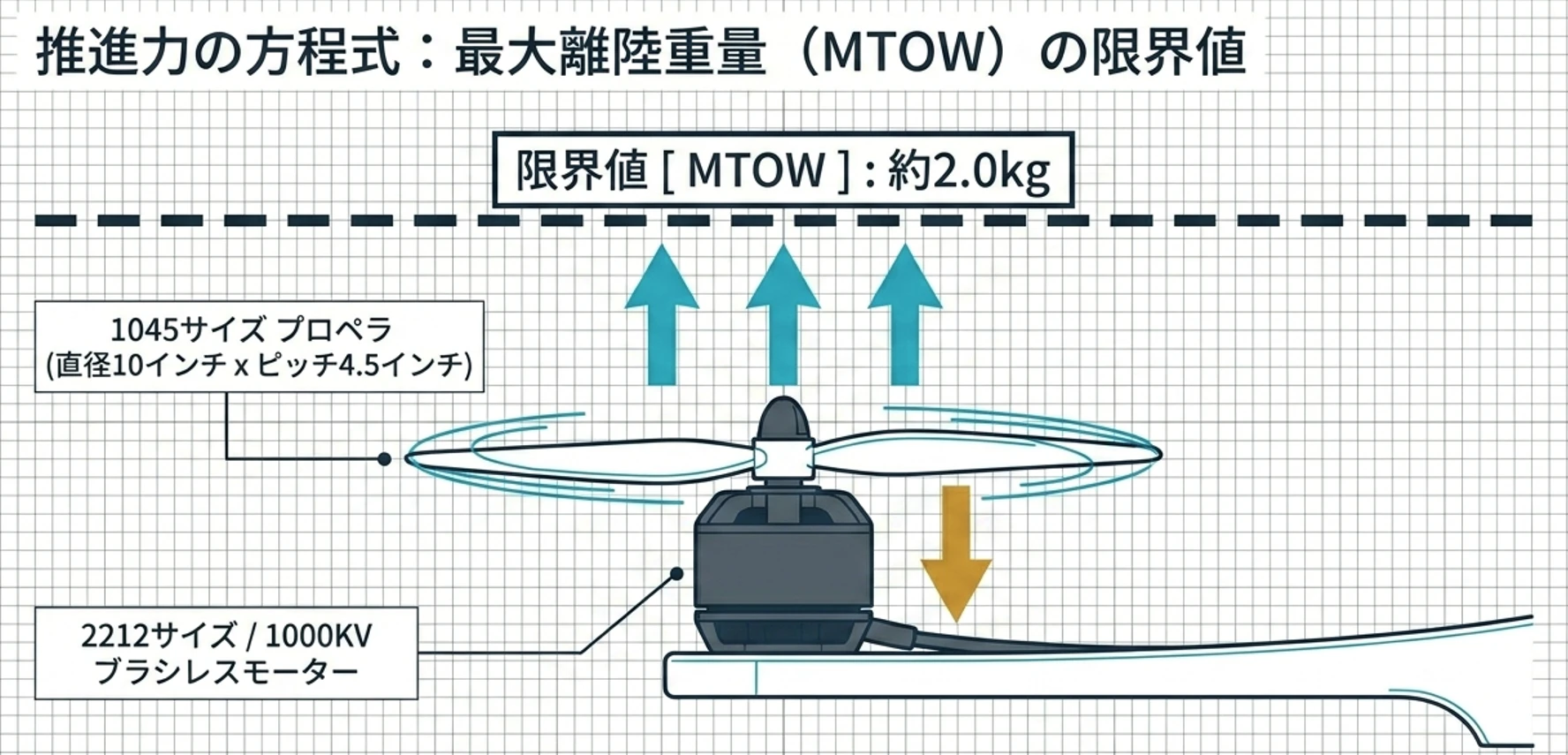

研究開発やプロトタイピングにおいて広く採用される標準的な機体として、対角モーター間距離が450mmの「F450」クラスのフレームが存在する。(ただし、「対角モーター間距離 550mm の F550 クラスもある」)このクラスの機体は、グラスファイバーやナイロン樹脂、あるいはカーボンファイバーで構成され、機体自重(バッテリー、モーター、配線を含む)は約800gから1.0kg程度に達する。

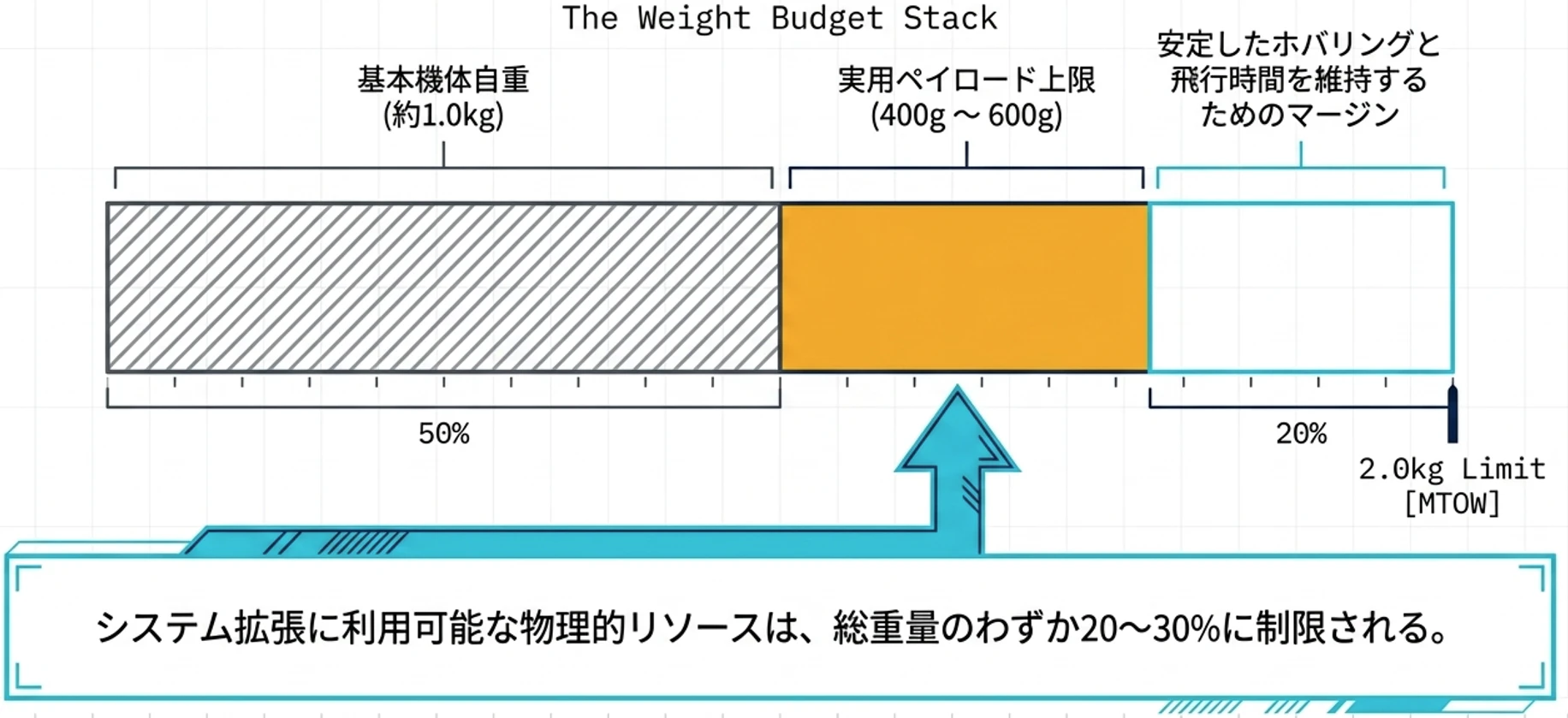

機体に搭載される2212サイズの1000KV(1ボルトあたりの無負荷回転数)ブラシレスモーターと、1045サイズ(直径10インチ、ピッチ4.5インチ)のプロペラの組み合わせは、効率と推力のバランスを重視した設定である。この構成における最大離陸重量(MTOW)は一般的に約2.0kg程度が限界となるため、安定したホバリングと適切な飛行時間を維持するための実用的なペイロード(積載量)は400gから600g程度に制限される。

この物理的な制約は、後述するミッション系の拡張(コンパニオンコンピュータ、5G/LTE通信モジュール、LAN-UART変換基板などの統合)において極めて重要な意味を持つ。システムアーキテクトは、高度な情報処理と通信機能を追加する一方で、これらペイロードの増加が引き起こす推力重量比の低下とバッテリー消費量の増大を精密に計算し、トレードオフを最適化しなければならないのである。

3. フライトコントローラ(FC)のソフトウェアアーキテクチャと制御理論

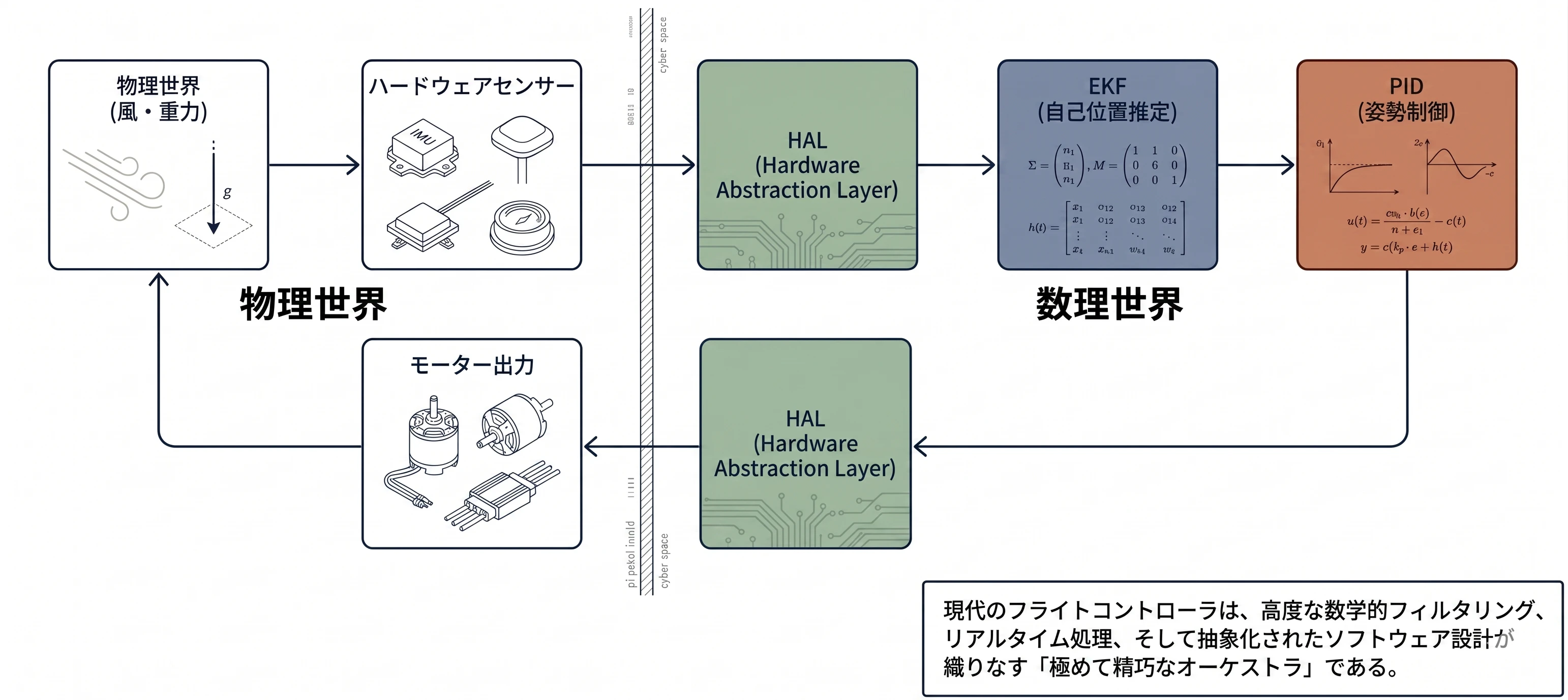

フライトコントローラは、機体の姿勢安定化から高度な自律ナビゲーションまで、膨大なセンサーデータを処理し、モーターへの指令を生成する「脳」として機能する。この領域では、高度な数学的フィルタリングとハードリアルタイムなタスクスケジューリングが要求される。

3.1 センサーフュージョンと拡張カルマンフィルタ(EKF)

機体が安定して空中に留まるためには、自身が空間内のどの位置にあり、どちらに傾いているかを正確に把握する自己位置推定(State Estimation)が不可欠である。FCは単一のセンサーに依存せず、複数の異なる特性を持つセンサーデータを数学的に統合(フュージョン)することで、ノイズや一時的なデータ欠損を補い合う。

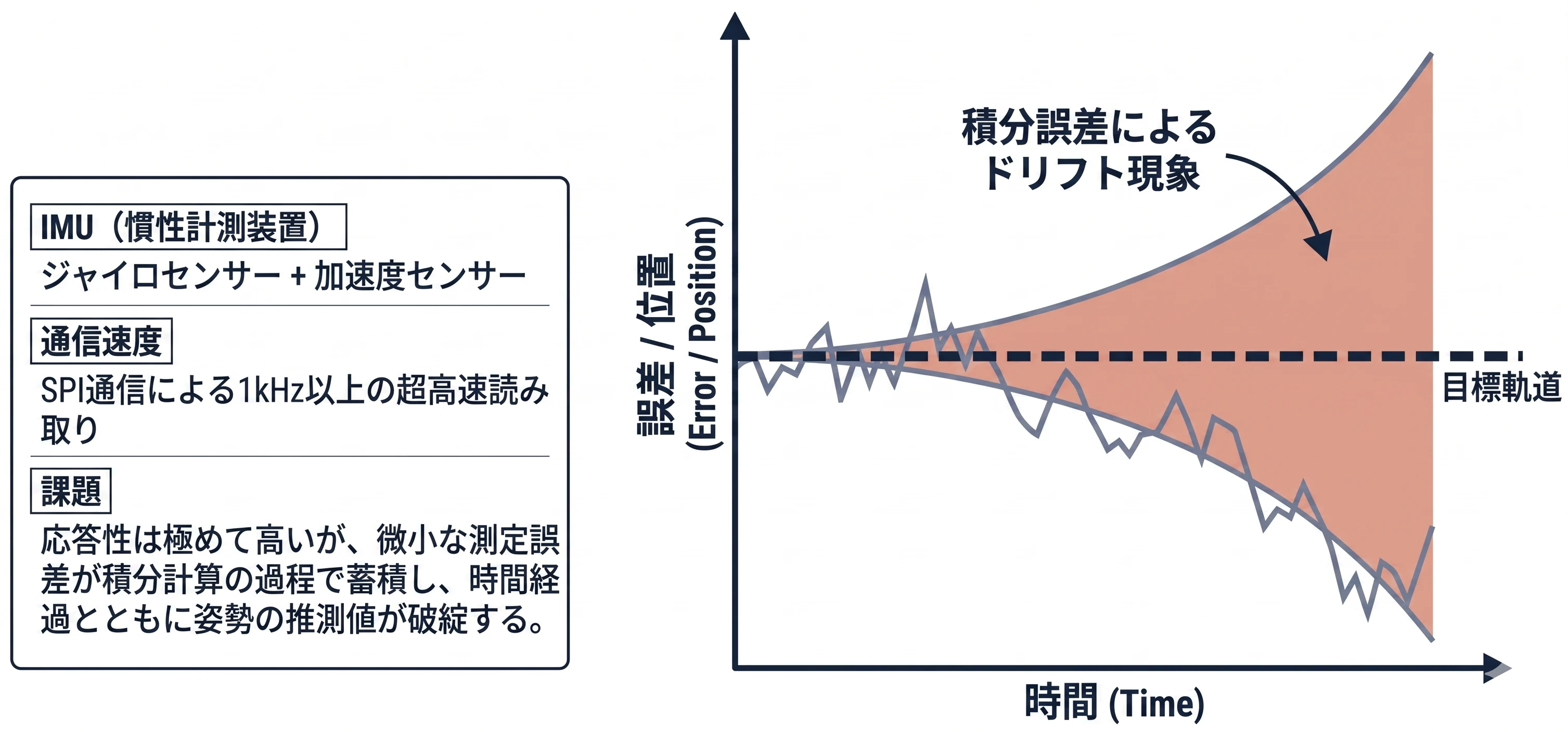

この処理の核心をなすのが「拡張カルマンフィルタ(EKF: Extended Kalman Filter)」である。FC基板上に実装されたIMU(慣性計測装置、主にジャイロセンサーと加速度センサー)は、SPI(Serial Peripheral Interface)通信を用いて1kHz以上の超高速で機体の角速度と加速度を読み取る。IMUは応答性に極めて優れているが、微小な測定誤差が積分計算の過程で蓄積し、時間経過とともに姿勢がズレていく「ドリフト現象」が避けられない。

このドリフトを補正するために、EKFはUART経由で取得するGPS(GNSS)の絶対的な位置座標や速度情報、さらにはI2C経由で取得する気圧計(Barometer)の高度データ、地磁気センサー(コンパス)の方位データを掛け合わせる。高速だが誤差が蓄積しやすいIMUの相対データと、低速だが長期的に安定したGPS等の絶対データを確率・統計的な手法で統合することにより、FCは突風などの外乱に対する即応性と、長時間の正確なホバリング精度を高い次元で両立させているのである。

3.2 リアルタイムPID制御と応答性のチューニング

EKFによって推定された現在の機体姿勢と、操縦者(あるいは上位の自律航法プログラム)から指示された目標姿勢との間に生じる偏差(エラー)を最小化するために、FCはPID(Proportional-Integral-Derivative)制御ループを実行する。

- Proportional(比例)制御: 現在の偏差の大きさに直接比例して修正力を出力する。このゲインを高めると機体の反応は俊敏になるが、過剰に設定すると目標値を行き過ぎて振動(ハンチング)を引き起こす。機体の「瞬発力」を決定する要素である。

- Integral(積分)制御: 過去から現在までの偏差の蓄積を計算し、継続的なズレを補正する。重心の偏りや、定常的に吹き付ける風による流されを防ぐ。機体の「持久力」と定常偏差の解消を担う。

- Derivative(微分)制御: 偏差の変化率(スピード)を計算し、目標姿勢に急激に近づいている場合には、行き過ぎを防ぐために逆方向のブレーキをかける。機体の挙動の「キレ」や「減衰性」を制御する。

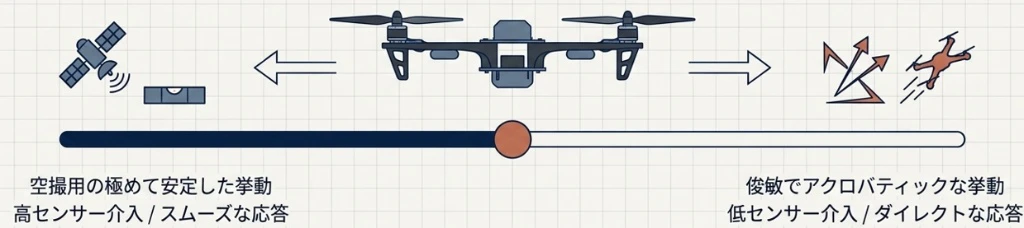

F450/F550キットに付属するPixhawkなどの高度なFCでは、PC上の設定ソフトウェア(Mission PlannerやQGroundControl)を通じて、これらPIDのパラメータを極めて細かく調整(チューニング)することが可能である。これにより、同一のハードウェア構成であっても、ソフトウェアのパラメータを変更するだけで、「GPSと気圧計をフル活用した空撮用の緩慢で極めて安定した挙動」から、「センサーの介入を最小限に抑え、パイロットの入力がダイレクトにモーター出力に反映される俊敏でアクロバティックな挙動」まで、機体の性格を自由自在に再定義できるのである。

3.3 ミドルウェアとしてのArduPilot/PX4の進化

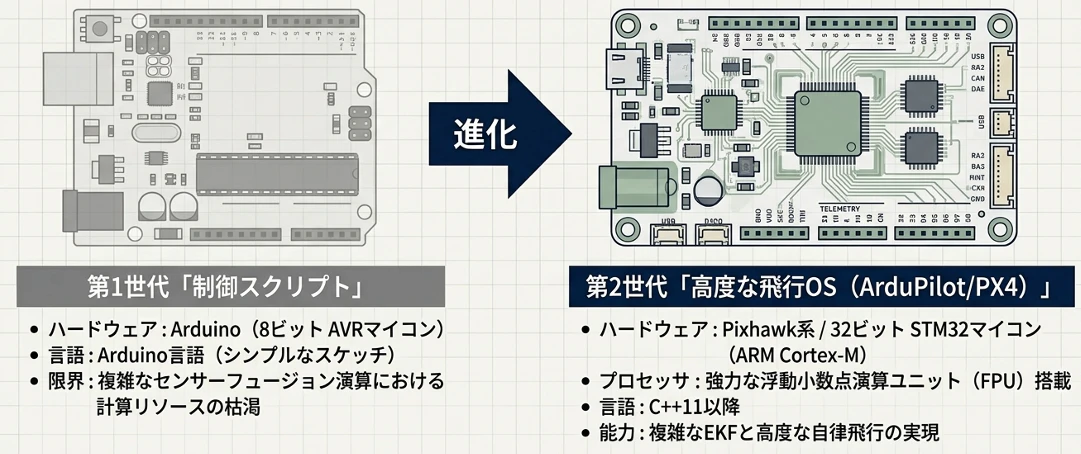

現在、産業用、研究用、および軍事用ドローンのデファクトスタンダードとなっている「ArduPilot」や「PX4」は、単なる制御スクリプトの域を脱し、高度に抽象化された「飛行OS(ミドルウェア)」として機能している。

歴史的に見れば、ArduPilotの初期バージョンはArduino(8ビットのAVRマイコン)上で動作するシンプルなスケッチとして開発がスタートした。しかし、自律飛行や複雑なセンサーフュージョン演算の需要が高まるにつれ、8ビットマイコンの性能限界に直面した。その結果、現在主流となっているPixhawk系のハードウェアは、強力な浮動小数点演算ユニット(FPU)を搭載した32ビットのSTM32マイコン(ARM Cortex-Mシリーズ)へと完全に移行し、ArduPilotのコードベースもArduino言語から高度なC++(C++11以降)へと書き換えられた。

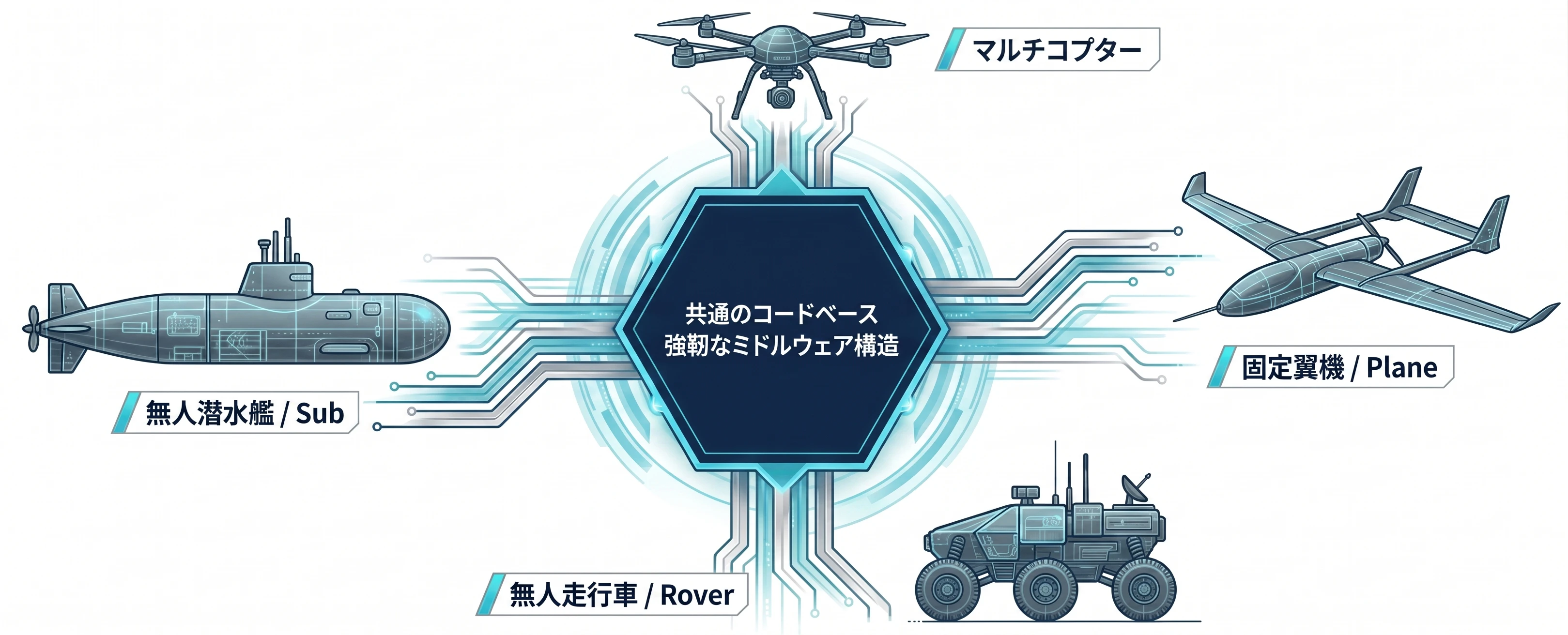

現在のArduPilotのアーキテクチャは、ハードウェア抽象化層(HAL)の上に構築されている。HALは、マイコンチップごとの特有のレジスタ操作を隠蔽し、コードが海外製の汎用基板から、後述する純国産の高信頼性基板まで、異なるハードウェア上でシームレスに動作することを可能にする。この強靭なミドルウェア構造は、マルチコプターだけでなく、固定翼機(Plane)、無人走行車(Rover)、さらには無人潜水艦(Sub)に至るまで、共通のコードベースで陸海空すべての自律ロボットを制御できる圧倒的な拡張性をもたらしている。

4. 学習のベースライン:なぜ「Pixhawk」と「PX4/ArduPilot」を選ぶのか

今回の調査では、私や初学者向けの学習用ステップとして「Pixhawk(ピクスホーク)」と、定番の機体フレームである「F450/F550」、そしてソフトウェアには「PX4」や「ArduPilot」を選定して手作りドローンの現在地を深堀することとした。

もしかしたら、これらを選定することに対し、疑問を持たれる向きもあるかもしれない。

「純国産ハードウェアの採用」や「ブラックボックスの排除」を掲げる本記事の趣旨において、海外製のコモディティ・ハードウェアやグローバルなオープンソースソフトウェアの採用は、一見すると矛盾しているように映るからだ。

しかしここで、筆者がこれらグローバルスタンダードのアーキテクチャとエコシステムについて徹底的な深掘り調査を行い、熟考の末にあえて「ベースライン」として選定したことを明確に宣言しておきたい。これから真のテクノロジー・ソブリンティを目指して独自制御系の開発に挑むエンジニアが、システムインテグレーションの基礎を固めるにあたり、これらを最初のステップとして選定した理由は以下の通りである。

4.1 巨人の肩に立つ:制御理論とアーキテクチャの「正解」を知る

ArduPilotやPX4は、過去十数年にわたり世界中の航空宇宙エンジニアや研究者が磨き上げてきた「叡智の結晶」である。機体を安定させるためのPID制御の挙動、センサーノイズを打ち消す拡張カルマンフィルタ(EKF)の収束プロセス、そしてフェイルセーフ発動時のシーケンスなど、自律飛行に求められるあらゆる論理がコードとして実装されている。

我々が将来的にRustを用いてベアメタルから制御系をフルスクラッチで再構築する(第9章参照)にしても、まずは「完成されたシステムがどのように物理世界と相互作用し、正しく飛ぶのか」というリファレンス(正解)を体感し、システム全体の振る舞いを完全に理解しなければならない。

4.2 ブラックボックスのない「むき出しの物理」との対話

市販の完成品ドローン(DJI製品など)は極めて優秀であるが、内部の通信プロトコルや制御ループは完全にブラックボックス化されており、エンジニアリングの学習対象としては不適切である。

一方、F450/F550 などの開発用フレームと個別のモーター、ESC、フライトコントローラを自らの手で結線し、組み上げるプロセスは「むき出しの物理」との対話である。プロペラの振動がどのようにFCのジャイロセンサーに悪影響を与えるか、電圧降下がいかにしてシステムを不安定にするかといった物理レイヤーの制約(第2章参照)を、机上の空論ではなく「手触り」として学ぶための最高の教材となる。もし技術者として、どこからどこまでもオープンであることが分かれば、サプライチェーンに与えるリスクを正確に評価できることにもつながる。

4.3 業界標準プロトコル(MAVLink等)の実装形態の体得

ドローンを単なるRC機器から「空飛ぶエッジサーバー」へと昇華させるためには、コンパニオンコンピュータや地上局(GCS)との論理的な通信が不可欠である。この標準プロトコルであるMAVLinkや、ESCとのデジタル通信規格であるDShotが、実際のシステム内でどのようにルーティングされ、処理されているかを既存のPixhawk環境で徹底的に解析する。

この標準インターフェースの仕様を体得しておくことで、将来的にFC基板を純国産のJFB-100に載せ替えたり、独自の暗号化通信モジュールを間に挟み込んだりする際にも、既存のエコシステム(地上局ソフトウェア等)との後方互換性を保ちながらシステムを拡張することが可能となる。

既存の「巨人の肩」に乗り、ドローンが飛ぶための物理的・電気的・論理的な要件を余すところなく形式知化して初めて、それを新たな言語や国産ハードウェアの上で「再定義」することが可能となるのである。

5. MAVLinkプロトコルとコンパニオンコンピュータの統合アーキテクチャ

単一のFC(マイコン)に、姿勢制御といったハードリアルタイム処理と、カメラ映像のエンコードやAI画像認識といった非リアルタイム処理の両方を担わせることは、計算リソースの枯渇とリアルタイム性崩壊のリスクを伴う。次世代ドローンの設計における「王道」は、機体の「小脳・脊髄」にあたる姿勢制御をFCが担い、「大脳」にあたる高度な情報処理と外部ネットワークとの通信をコンパニオンコンピュータ(Raspberry Pi、NVIDIA Jetson等)が担うという、明確な役割分担(Separation of Concerns)のアーキテクチャを採用することである。

5.1 階層間通信を担うMAVLinkプロトコル

FCとコンパニオンコンピュータは、物理的にはUART(シリアル通信)を介して接続され、論理的には世界標準の無人機用軽量通信プロトコルである「MAVLink」を用いて対話を行う。

5.2 制御権限の調停:RC Override vs. Guided Mode

コンパニオンコンピュータ側からMAVLinkを介してFCを操作し、機体を制御する場合、主に2つのアプローチが存在する。これらの使い分けが、システムの信頼性と遅延耐性を決定する。

第一のアプローチは、「RC Override(プロポ信号の乗っ取り)」である。これは、MAVLinkのRC_CHANNELS_OVERRIDEパケットを使用し、コンパニオンコンピュータからあたかも物理的なプロポのスティックを操作したかのようなPWM信号の仮想値をFCへ送信する手法である。既存の手動操縦モードをネットワーク越しに再現できるため実装が容易であるが、通信の遅延(レイテンシ)やパケットロスが直接機体の挙動の遅れとして現れるため、5Gのような極低遅延ネットワークが前提となる。

第二のアプローチは、「Guided Mode(目標値の直接指示)」である。これは、MAVLinkのSET_POSITION_TARGET_LOCAL_NEDやSET_ATTITUDE_TARGETパケットを使用し、「現在地から北へ5メートル、高度10メートルを維持せよ」あるいは「ピッチ角を前方に10度傾けよ」といった、より抽象度の高い指令をFCへ送り込む手法である。コンパニオンコンピュータ上のAIが画像認識によって算出した追尾ベクトルや、衛星通信経由で受信したウェイポイントをFCに渡す際、ネットワークの遅延やジッタの影響を最小限に抑えつつ、物理的な安定化処理はFC側の堅牢なPID制御に一任できるため、自律的なシステム構築において最も推奨されるアーキテクチャである。

6. マルチリンク通信システムの統合とネットワークアーキテクチャ

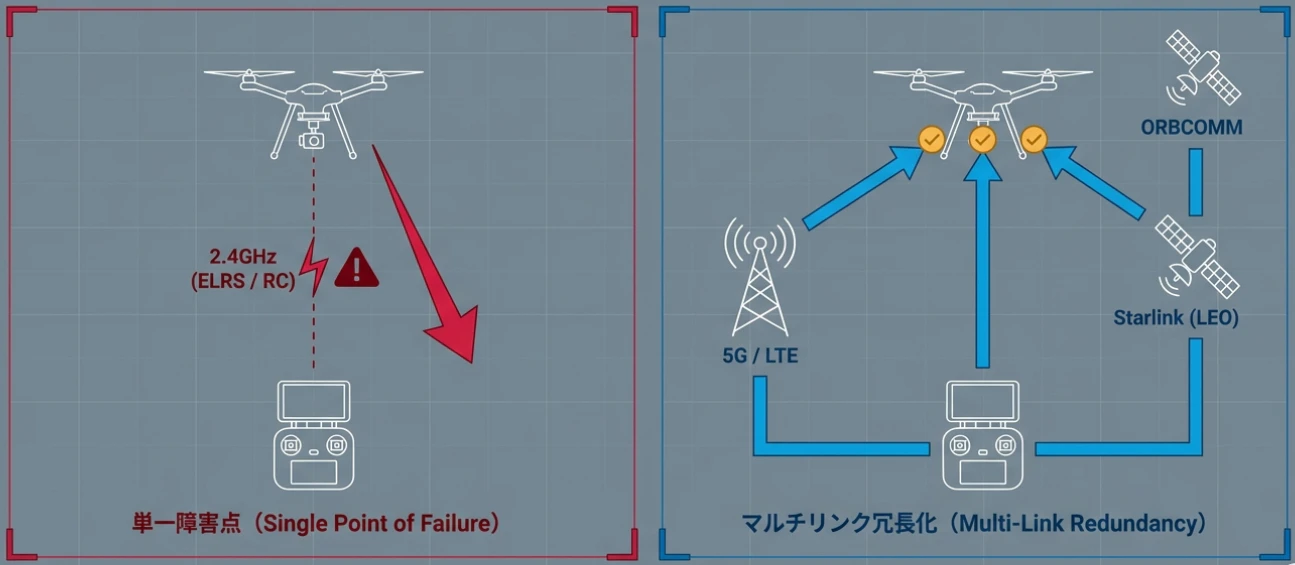

目視外飛行(BVLOS)や、電波状況が急変する極限環境下での運用を想定した場合、単一の2.4GHz帯プロポ信号(ELRSなど)に依存することは、リンク喪失による機体ロスのリスクを飛躍的に高める。したがって、物理的特性の異なる複数の通信インフラ(地上セルラー網、衛星通信、光ファイバ通信)を統合し、状況に応じて経路を動的に切り替えるマルチリンク通信システムの設計が必須の要件となる。

6.1 5G/LTE網による広域制御とLAN-UART変換モジュールの活用

地上モバイル回線(LTEや5G)を利用した制御は、低遅延(5GのuRLLC規格など)かつ広帯域であるため、遠隔操作や高解像度映像伝送の主軸となる。システム構成において、コンパニオンコンピュータ(Raspberry Piなど)を持たない軽量な機体、あるいはコンパニオンコンピュータとFC間のシリアル通信を直接IPネットワーク化したい場合、LAN-UART変換基板(シリアルデバイスサーバー)を利用してMAVLinkパケットをTCP/IPにカプセル化するアーキテクチャが極めて有効である。

この用途において、WIZnet社の「WIZ-IP20」あるいは「WIZ-IP75」などのシリアル-イーサネット変換モジュールが強力なソリューションとなる。WIZ-IP20は、RP2040(ARM Cortex-M0+デュアルコア)とハードウェアTCP/IPイーサネットコントローラ(W5500)を1つのパッケージに統合したW55RP20 MCUを中核とし、10/100 Mbpsのイーサネットインターフェースと、最大921.6 kbpsの高速UARTシリアルインターフェースをMAG-JACK型の極小フォームファクタ(32.5×16.5×17.3 mm)に収めた産業グレード(動作温度範囲 -40℃〜85℃)のモジュールである。

ハードウェア設計と実装において、極めて重大な留意点が存在する。WIZ-IP20およびWIZ-IP75の入力電圧(VCC)とシリアル信号レベルは、厳密にDC 3.3V(最小3.0V、標準3.3V、最大3.6V)に指定されている。一方で、PixhawkなどのFCのテレメトリポート(UART端子)から出力される電源(VCC)は一般的に5Vである。したがって、FCから供給される5Vを直接WIZ-IP20の電源ピンに接続すると、過電圧によりモジュールが即座に焼損・破壊される。システムインテグレータは、必ずLDO(低損失レギュレータ)等の降圧回路を介して3.3Vの安定した電源をWIZ-IP20のP11ピン(VCC)に供給しなければならない。なお、シリアル信号線(TXD, RXD)についてはロジックレベルが3.3V TTLであるため、FCのUARTピンと直結して双方向のデータ伝送が可能である。

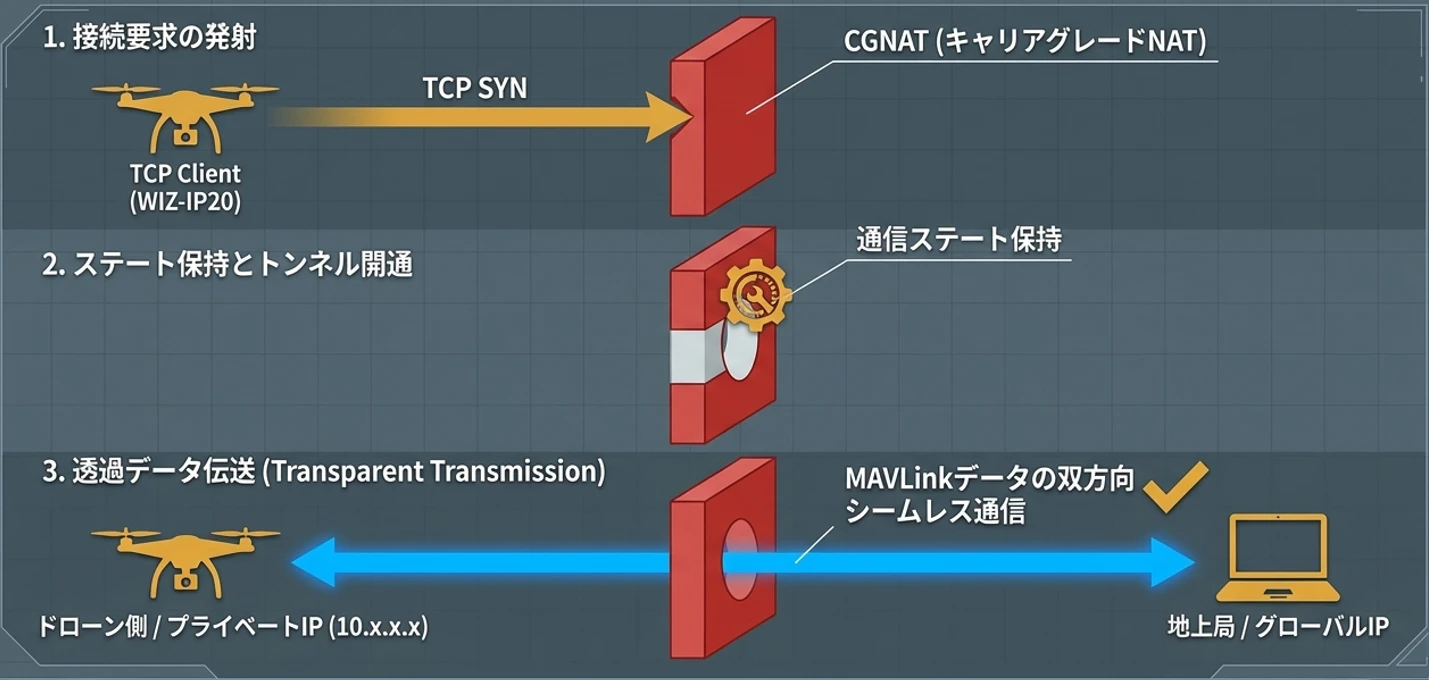

6.2 衛星通信の統合とCGNATを突破するネットワーク設計

地上波のセルラー電波が到達しない山間部や海上、あるいは災害によるインフラ断絶時においては、衛星通信網の統合が不可欠となる。通信帯域と遅延の特性に応じ、高速大容量のStarlink(LEO:低軌道衛星)をメインのミッションデータおよび操作リンクとして利用し、低速・極狭帯域のORBCOMMやGlobalstarなどを、メインリンク喪失時のバックアップテレメトリ(現在位置やクリティカルエラーの通知専用)としてUARTに直結する階層的アプローチが王道である。

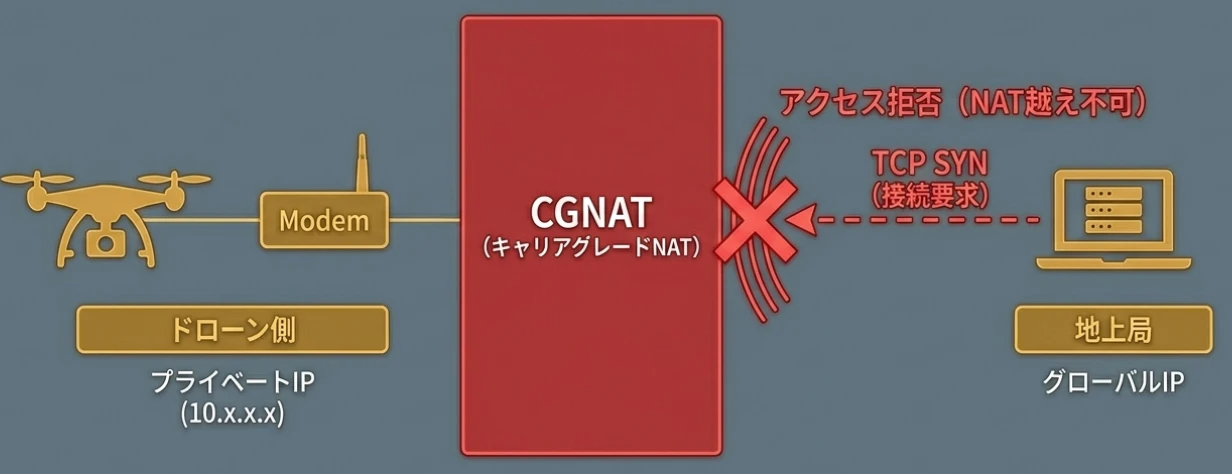

StarlinkやLTE/5Gのパブリックネットワークを利用する際、地味にネットワークエンジニアリング上の障壁となるのが、CGNAT(キャリアグレードNAT)の存在である。ドローン側に搭載された通信端末はNATの配下にプライベートIPアドレスを割り当てられるため、地上の操作局からドローンに対して直接IPアクセス(セッションの開始)を行うことはプロトコル上不可能である。

この「NAT越え」の問題を解決するためには、ドローン側から自発的に地上のグローバルIPを持つサーバーに対してセッションを開始する設計が必要となる。前述のWIZ-IP20モジュールを使用する場合、動作モードを「TCP Client」に設定することが解決策となる。WIZ-IP20はモジュール起動時、あるいはネットワーク復帰時に、あらかじめ設定されたリモートサーバーのIPアドレス(またはDDNSによるドメイン名)とポートに対して自動的に接続要求(SYNパケット)を送出し、セッションを確立する機能を持つ。一度TCPセッションが確立され「透過データ伝送(Transparent transmission)モード」に入れば、CGNATのルーター内に通信のステートが保持され、NATの壁を貫通してUARTから入力されたMAVLinkデータがシームレスに双方向伝送される。

ただし、TCPを用いた制御には注意が必要である。TCPはデータの到達を保証するためにパケットロス時に再送処理を行うが、これが原因で「ヘッドオブラインブロッキング」が発生し、リアルタイム性が命であるドローンの操作信号に致命的な遅延(レイテンシスパイク)を引き起こす懸念がある。このため、WIZ-IP20がサポートする「UDPモード」を活用し、コンパニオンコンピュータ側でUDPホールパンチングのロジックを実装することで、再送による遅延のない極低遅延なMAVLink通信経路を確立するアプローチが、制御系ネットワーク設計としてはより高度かつ堅牢な選択となる。

補足:IPv6による双方向性の確保とセッション制約の解消

昨今のStarlinkや主要キャリアのLTE/5G網においては、急速「IPv6 Ready」な通信環境が整いつつあります。地上側ドローン側両側でIPv6を利用すれば、地上の操作局からドローンへの直接アクセス、あるいはドローン間でのピア・ツー・ピア通信におけるセッション開始方向の制約は理論上解消されます。(適切なセキュリティ設定は必要です。)

| 通信プラットフォーム | 特性および帯域幅 | 遅延(Latency)の目安 | ドローンシステムへの実装と役割 |

|---|---|---|---|

| 2.4GHz プロポ (ELRS等) | 狭帯域(操縦信号に特化) | 極小(数ms〜数十ms) | 目視内(VLOS)での主操縦系。極めて高い応答性と信頼性を持つ。 |

| LTE / 5G モバイル網 | 広帯域(高解像度映像とデータ) | 小〜中(10ms〜50ms) | WIZ-IP20等を介したTCP Client/UDPによる広域制御。CGNATの突破が必須。 |

| Starlink (低軌道衛星) | 超広帯域(大容量データの高速伝送) | 中(20ms〜50ms) | コンパニオンPC経由のEthernet接続。地上インフラが存在しない環境下でのメイン回線。 |

| Globalstar / ORBCOMM | 極狭帯域(数十バイトのテキストのみ) | 大(数百ms〜分単位) | UART直結。完全自律のフェイルセーフ発動時に、現在座標を定期送信する最終生存信号。 |

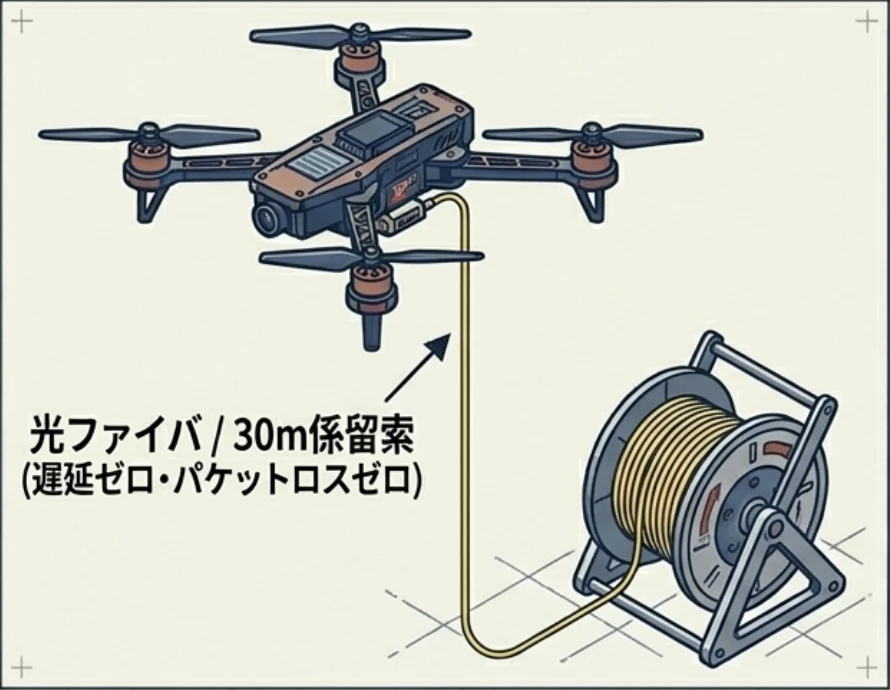

6.3 光ファイバを用いた有線通信と航空法上の係留飛行の優位性

光ファイバを利用した有線通信ドローンの価値が再評価されている。機体にSFPモジュール等の光電気変換器を搭載し、極細の光ドロップケーブルをボビンで巻き出しながら飛行することで、無線妨害(ジャミング)に対して原理的に強い、極低遅延・極低パケットロスの物理通信レイヤーが構築される。ただし、光電気変換器の信頼性、ファイバの機械的破断耐性、ボビンの巻き出し機構の安定性は、実装上の検証が必要な要素である。

(画像 Geminiで生成)

AliExpress を見るとこんな様な 10〜50kmの光ファイバがたくさん売っています。

特筆すべきは、日本国内において、十分な強度を有する物理的な紐を用いた「係留(けいりゅう)」飛行を行う場合、航空法上の極めて有利な特例措置(規制緩和)が適用される点である。

現行の日本の航空法および関連規則において、「30メートル以下の長さの紐などで機体を係留」し、かつ第三者がその範囲内に立ち入らないようカラーコーン等で「立入管理措置」を講じた場合、複数の重要な飛行禁止空域および飛行方法の制限が解除され、国土交通省への事前の個別許可・承認手続きが不要(または大幅に簡略化)となる。具体的に許可が不要となるのは、以下の項目である。

- 人口集中地区(DID)の上空における飛行

- 夜間飛行

- 目視外飛行(BVLOS: モニターのみを見た操縦)

- 第三者の人または物件から30m未満の距離での飛行

- 物件投下

この法改正は、次世代のドローンシステムを開発するエンジニアにとって計り知れない価値をもたらす。未検証の自作RustベアメタルFCコードや、開発中の5G・光通信を用いたマルチリンクMUX(多重化)の通信プロトコルを実際の屋外環境でテストする際、万が一のソフトウェアバグに起因する暴走(フライアウェイ)リスクを物理的な係留索によって完全に防止できると同時に、DID地区での実験や夜間におけるセンサーの挙動確認を合法かつ迅速(アジャイル)に反復できる環境が担保されるからである。

ただし、この特例措置を適用した場合であっても、空港等の周辺空域、地表から150m以上の高度、多数の人が集まる催し場所の上空、および危険物の輸送については、引き続き航空法に基づく厳格な許可が必要である点に留意しなければならない。

6.4 マルチリンク通信におけるセキュリティ要件と認証・暗号化設計

マルチリンク通信システムは、通信経路の冗長化により可用性を高める一方で、攻撃面(アタックサーフェス)を確実に拡大する。LTE/5G、Starlink、光ファイバ、ELRS の各経路に対して、認証・暗号化・鍵管理・フェイルセーフの設計を体系的に行わなければ、運用段階で深刻な脆弱性となる。本節では、ドローン通信における最低限のセキュリティ要件を整理する。

MAVLink2 signing の必須化と射程の正確な理解

MAVLink プロトコルの第 2 世代である MAVLink2 では、メッセージ署名(signing)機構が標準化されている。これは送信元検証(origin verification)のための仕組みであり、不正な送信元から注入されたコマンドの拒否、リプレイ攻撃の防止に有効である。PX4 の公式ドキュメントでも明示されている通り、MAVLink2 signing は origin verification の機構であり、ペイロード自体を暗号化するものではない。

つまり、MAVLink2 signing を有効化しただけでは、通信内容そのものは平文として公衆網に流れる。緯度・経度・速度・ミッション内容・カメラ映像のメタデータ等が、傍受可能な形で伝送される構造である。これは経済安保用途・防衛用途では許容できない。

したがって、MAVLink2 signing は「最低限の必須要件」であり、その上にトランスポート層の暗号化を重ねる二重構造が必要となる。

トランスポート層暗号化 ── VPN / WireGuard / IPsec / DTLS

LTE/5G、Starlink といった公衆網を経由する場合、ドローンと地上局の間に暗号化トンネルを構築する設計が必須である。具体的な選択肢は以下の通り。

- WireGuard: 軽量・高速・現代的暗号アルゴリズム(ChaCha20-Poly1305)採用。組込み Linux でも実装容易。コンパニオンコンピュータ(Raspberry Pi 等)上で動作させる構成が現実的である。

- IPsec: 業界標準で実績豊富。設定が複雑だが、エンタープライズ要件との親和性が高い。

- DTLS: UDP ベースのリアルタイム制御に向く。WebRTC の DataChannel もこれを使う。低遅延性が要求される操縦系に適合する。

選択基準としては、操縦系のような低遅延要求のチャネルには DTLS、テレメトリ・映像伝送には WireGuard、エンタープライズ統合が必要な場合は IPsec、という使い分けが妥当である。

チャネル分離 ── 操縦系・テレメトリ系・映像系の役割分担

マルチリンク通信では、すべてのトラフィックを単一の暗号化トンネルに流すのではなく、チャネル種別ごとに通信経路と暗号化方式を分離する設計が望ましい。

| チャネル種別 | 推奨経路 | 暗号化方式 | 遅延要件 |

|---|---|---|---|

| 操縦系(コマンド) | ELRS / 専用低遅延リンク | DTLS / 専用暗号 | 極小(< 50ms) |

| テレメトリ系 | LTE/5G / Starlink | WireGuard | 小(< 200ms) |

| 映像系 | LTE/5G / Starlink / 光ファイバ | DTLS / SRTP | 中(< 500ms) |

| フェイルセーフ | ORBCOMM / Globalstar | 軽量暗号(AES-128) | 大(数秒〜分) |

この分離により、ある経路の輻輳・遅延・断絶が他経路に波及しない設計となる。また、攻撃者が一経路を侵害しても、他経路の独立性が保たれる。

鍵管理 ── 配布・失効・更新の運用設計

暗号化と認証の運用において、最も困難かつ最も軽視されがちなのが鍵管理である。以下の運用設計が必須となる。

- 鍵の配布: 機体の出荷時に事前共有鍵を埋め込む。USB-TypeC 経由のセキュアブートストラップが現実的。

- 鍵の失効: 機体の喪失・捕獲・退役時に、地上局側で当該機体の鍵を失効させる手順を準備する。失効リスト(CRL)の運用、または短期鍵+定期更新の方式を設計する。

- 鍵の更新: 一定期間ごとの自動鍵更新(rekeying)を実装し、長期鍵の漏洩リスクを限定する。

- 鍵の階層化: マスター鍵・セッション鍵・デバイス鍵を分離し、一段の漏洩で全体が破綻しない構造とする。

経済安保用途では、鍵管理基盤(PKI)の構築と運用が、半導体国産化と並ぶ重要課題となる。

通信断時のフェイルセーフ定義

マルチリンクの本来の目的の一つは、通信断時の安全な機体挙動の確保である。フェイルセーフの動作モードを、明示的に定義しておく必要がある。

- 第一段階(操縦系断絶): 操縦系コマンドが N 秒以上途絶した場合、機体は事前定義のホバリング位置または直前のウェイポイントに自律保持する。

- 第二段階(テレメトリ系断絶): テレメトリ系も途絶した場合、機体は離陸点(RTH: Return To Home)への自律帰還を開始する。

- 第三段階(全経路断絶): 全経路が途絶した場合、ORBCOMM/Globalstar 等のフェイルセーフ経路で最終座標を地上に通知し、安全な不時着地点を選定して着陸する。

この三段階フェイルセーフは、ArduPilot / PX4 の標準機能として設定可能である。経済安保用途では、各段階の遷移条件・タイムアウト値・帰還経路を、ミッション仕様に応じて事前設計しておく必要がある。

平文 MAVLink を公衆網に流さない原則

最後に、最も基本的かつ最も守られにくい原則を強調しておく。平文 MAVLink を、暗号化トンネルなしで公衆網(LTE/5G/Starlink)に流してはならない。MAVLink は通信効率を重視した平文プロトコルであり、ヘッダ・ペイロード・チェックサムが容易に解析可能な構造を持つ。これを公衆網に直接流すことは、機体の位置・状態・ミッションを完全に公開するに等しい。

WIZ-IP20 等の TCP Client モードを使う場合、必ず WireGuard 等のトンネル内で MAVLink を流す設計とする。ローカル 5G 等の閉域網を使う場合でも、MAVLink2 signing は最低限有効化する。これは「念のため」ではなく、運用上の必須要件である。

7. 安全保障環境におけるドローン技術と国産ハードウェアの重要性

ドローン技術は、もはや純粋なホビーや学術研究の枠を超え、国家の安全保障や重要インフラの維持に直結する戦略的テクノロジーへと変貌を遂げた。この現実は、現在進行中のウクライナ紛争をはじめとする現代戦において、市販のコンポーネントとオープンソースのフライトコントローラが兵器体系の中核に組み込まれている事実からも明らかである。

7.1 電子戦環境下でのオープンソースミドルウェアの強靭性

ウクライナの戦場において、数千キロ先を自律飛行して目標に到達する長距離ドローンや、前線の戦術的偵察機の多くには、ArduPilotやPX4といったオープンソースのミドルウェアが搭載されている。これらが採用される理由は、単なるコストパフォーマンスの高さだけではない。

戦場においてロシア軍が展開する強力なGPSジャミング(電子戦)に直面した際、オープンソースであるArduPilotのコードベースは現地のエンジニアによって即座に書き換えられた。光学カメラの映像から地形の特徴点を抽出し、自己の移動量を計算するオプティカルフローやVisual Odometry(視覚的自己位置推定)のアルゴリズムが統合され、GPSの電波が一切届かない環境下でも慣性航法と画像認識を組み合わせて正確な自律飛行を継続する「GPSに依存しない飛行ロジック」が驚異的なスピードで実装・デプロイされたのである。この圧倒的な適応力とアップデートの俊敏性は、閉鎖的で固定化された軍用専用システムに対する、オープンアーキテクチャの明確な優位性を証明している。

7.2 サプライチェーンリスクと純国産ハードウェアへのデプロイ

オープンソースのソフトウェアが持つ強靭性の一方で、それを実行するハードウェア(FC基板)の製造元に関しては、経済安全保障上の重大な懸念が存在する。市場に流通している安価なFC基板の大部分は海外で製造されており、ファームウェアの奥深くに意図しない通信を行うバックドアが仕掛けられているリスク、あるいは有事の際にコンポーネントの供給が遮断されるサプライチェーンリスク(ディスコンティニュー)を排除することができない。インフラ点検、防衛、警備といった秘匿性の高い業務において、ブラックボックス化された海外製ハードウェアの使用は忌避される傾向が強まっている。

この課題を解決するため、日本国内のメーカーによる「純国産フライトコントローラ」の開発と採用が進んでいる。その代表的なソリューションの一つが、航空宇宙・防衛産業で豊富な実績を持つ日本航空電子工業(JAE)が開発した「Flight Brain™ JFB-100/JFB-110」シリーズである。

JFB-100(Basic モデル)および JFB-110(Standard モデル)は、航空機装備品と同等の厳格な設計基準で国内製造されており、極めて高いハードウェア信頼性を誇る国産フライトコントローラである。本ハードウェアは、オープンソースのフライトプログラム(ArduPilotやPX4)をそのまま搭載可能である点が最大の特長であり、ArduPilot では日本製フライトコントローラとして初めて公式認定を受けている。システムアーキテクチャとして、自動車向け高信頼性 IMU を複数搭載することでセンサーの冗長性を確保し、温度変動や激しい振動に対する高度な耐環境性(MIL-STD-810 および DO-160G 準拠)を実現している。動作温度範囲は -40℃ から +85℃ と極めて広く、過酷な環境下での運用が保証されている。JFB-100 の故障率は 166×10⁻⁶ という航空機装備品レベルの高い信頼性指標が公称されている。

両モデルの主要な仕様を以下に整理する。

| 項目 | JFB-100 (Basic) | JFB-110 (Standard) |

|---|---|---|

| プロセッサ | STM32F シリーズ (Flash 2MB / RAM 512kB) | STM32H シリーズ (Flash 2MB / RAM 1MB) |

| IMU(慣性計測装置) | 2 個 | 3 個 |

| 気圧計 | 1 個 | 2 個 |

| 磁気センサ | 1 個 | 1 個 |

| PWM 出力 | 8 ch | 16 ch |

| UART | 4 ch | 4 ch |

| I2C | 3 ch | 3 ch |

| SPI | 1 ch | 1 ch |

| CAN | 2 ch | 2 ch |

| USB | USB-TypeC (1 ch) | USB-TypeC (1 ch) + USB I/F (1 ch) ※同時使用不可 |

| 電源入力 | DC +5V / Power 入力 2 ch | DC +5V / Power 入力 2 ch |

| 外形寸法 | D67 × W88 × H17 mm | D67 × W88 × H17 mm |

| 質量 | 50 g | 60 g |

| 消費電力 | ≦ 3W | ≦ 3W |

| 動作温度範囲 | -40 〜 +85℃ | -40 〜 +85℃ |

| 耐環境性試験 | MIL-STD-810 / DO-160G 準拠 | MIL-STD-810 / DO-160G 準拠 |

| 故障率 | 166 × 10⁻⁶ | 176.1 × 10⁻⁶(参考) |

| 外部 I/F コネクタ | 車載用 MX77A シリーズ(防水) | 車載用 MX77A シリーズ(防水) |

| ファームウェア | ArduPilot / PX4 搭載可能 | ArduPilot / PX4 搭載可能 |

| 製造拠点 | 東京都昭島市 JAE 昭島事業所 | 東京都昭島市 JAE 昭島事業所 |

出典: 日本航空電子工業株式会社「Flight Brain™ JFBシリーズ」公式カタログ(2024年6月版)に基づき作成

両モデルとも外部 I/F コネクタには車載用の MX77A シリーズ(JAE 製の自動車向け防水コネクタ)が採用され、振動耐性と防水性を確保している。JFB-100 と JFB-110 の主な違いは、プロセッサのグレード(STM32F → STM32H)、センサー冗長性(IMU 2 個 → 3 個、気圧計 1 個 → 2 個)、PWM 出力数(8ch → 16ch)、および USB 拡張性であり、JFB-110 はより高い冗長性と拡張性が要求される産業用途に向けて位置付けられている。

すべての Flight Brain シリーズは、東京都昭島市にある JAE の昭島事業所で設計から製造まで一貫して行われており、品質マネジメントシステムの ISO9001 および航空宇宙分野の JIS Q 9100 認証を取得した国内製造体制を持つ。出荷する全数に対して X 線検査装置と人の目によるはんだ品質検査、温度・湿度・振動を含む環境試験が実施されており、サプライチェーンの透明性と製造品質の両面で、海外製汎用 FC とは一線を画している。なお、JAE は 2026 年春に Standard モデル JFB-110 の上位機種として、CubePilot の Cube ファミリと同様にセンサーモジュール(社内通称「オクタ」)と I/O ボードを分離した汎用性の高い「JFB-200」のリリースを予定している。

システムインテグレータは、開発の初期段階において安価な海外製の Pixhawk 等を利用して「Rust による独自制御ループの確立」や「WIZ-IP20等を用いた5G・光通信のルーティングロジックの構築」を行い、概念実証(PoC)を高速に回す。そして実運用フェーズへの移行にあたり、MAVLink ベースの上位運用設計、ミッション設計、地上局統合といった上位レイヤを再利用しつつ、JFB-100/JFB-110 への移植を行う。ただし、ボードサポートパッケージ(BSP)、ハードウェア抽象化レイヤ(HAL)、センサ構成、ピンマップ、ブートローダ、パラメータ、キャリブレーションは JFB シリーズ向けに個別に再検証が必要である。同一バイナリの無変更展開ではなく、上位アーキテクチャとミッション設計の継承による移植性確保が、現実的なアプローチとなる。このアプローチこそが、開発の俊敏性(アジリティ)を維持しつつ、最終製品におけるハードウェアレベルのセキュリティとサプライチェーンの透明性を完全に証明する、現代のエンジニアリングにおける最適解と言える。

7.3 コンポーネント別サプライチェーンリスクの評価と国産化のロードマップ

オープンソースソフトウェアの強靭性を確保した上で、次に直面するのが物理的なハードウェアの調達リスクである。有事や地政学的緊張が高まった際、特定の国や地域に依存するサプライチェーンは、文字通りドローンの「生産停止(=防衛・インフラ維持能力の喪失)」に直結する。

第2章で定義したマルチコプターの主要コンポーネントについて、現状のグローバル市場における調達構造と、特定の海外サプライヤーに依存する「サプライチェーンリスク度(経済安全保障上の脅威度)」を以下の表にマッピングした。

| コンポーネント名 | リスク度 | 主な依存要因・脅威と、国産化に向けた課題・解決策 |

|---|---|---|

| バッテリー (LiPo) | 極高 | 電池セル製造および原材料(リチウム、コバルト等)が特定国に圧倒的に偏在している。ドローン用の超高放電(ハイレート)セルの国内量産基盤は極めて乏しく、最も深刻なボトルネック。全固体電池など次世代技術へのパラダイムシフトが待たれる。 |

| 通信モジュール | 高 | 市場に流通する安価な5G/LTEモジュール(Quectel等)は特定国製が席巻しており、バックドアや情報漏洩リスクを排除しきれない。WIZnet(韓国等フレンドショアリング圏)の活用や、国内メーカーによるセキュアな通信モジュールの独自開発が急務である。 |

| ESC / FC | 高 | 汎用的なFCとESCは海外の安価なPCB製造とSTM32等のMCUに依存。特にESCはファームウェアのブラックボックス化が懸念される。解決策として、FCは前述のJAE JFB-100等へ移行し、ESCは独自実装あるいはFPGAによる国産ロジックへの置き換えが必要。 |

| GPS / GNSS | 高 | u-blox(スイス)等が主流だが、安価なモジュール基板は海外製に依存。また、GPSスプーフィング(電波欺瞞)への耐性も課題。日本の準天頂衛星「みちびき(QZSS)」の高精度測位(CLAS)にネイティブ対応する国産受信機の統合が防衛上不可欠である。 |

| コンパニオンPC | 中〜高 | Raspberry Pi(英)やJetson(米)など設計は同盟国圏だが、製造(ファウンドリ)が台湾等に集中しており、台湾有事の際の部品枯渇リスク(半導体チョークポイント)を抱える。調達網の多重化と国内ファウンドリ(Rapidus等)の成長が長期的な鍵となる。 |

| ブラシレスモーター | 中 | 強力な磁力を生むネオジム磁石など、レアアース(希土類)の採掘・精製における特定国依存が弱点。ただし、日本国内には日本電産(Nidec)やマブチモーターに代表される世界最高峰のモーター設計・製造基盤が存在するため、有事の技術転用は比較的容易。 |

| IMU (慣性計測装置) | 中 | Bosch(独)やTDK InvenSense(米/日)など欧米日メーカーが強い領域。ただし、コンシューマー向けの安価なチップは供給網が不安定になり得る。JAE製の高精度な産業用・防衛用IMU(SCHAシリーズ等)を採用することで、リスクの極小化が可能。 |

| フレーム / プロペラ | 低 | カーボンファイバー(東レ等)をはじめ、複合材料における日本の素材産業の優位性は圧倒的である。コスト競争の観点から現在は海外での成型加工が主流だが、有事の際に国内の町工場や3Dプリント設備等で代替生産を立ち上げるハードルは最も低い。 |

リスク度分類の基準:【極高】代替が極めて困難で即座に生産が停止する / 【高】半導体やブラックボックスを含み情報漏洩リスクがある / 【中】同盟国からの調達が可能だが地政学リスクを含む / 【低】国内の技術・素材基盤で比較的早期に代替可能

この評価から明らかなように、フレームやモーターといった「力学的・機械的要素」については、日本の分厚いモノづくり基盤によって十分に代替・国産化が可能である。一方で、致命的なアキレス腱となるのが「ハイレートLiPoバッテリー」と「通信・制御を司る半導体モジュール」である。

純国産ドローンの実現とは、すべての部品を直ちに日本国内で作ることではない。「どの部品が止まればシステム全体が成り立たなくなるか?」というチョークポイントを正確に見極め、戦略的に代替品(あるいはFPGA等を用いた独自の回路設計)を準備しておく「技術的な備え」に他ならない。FCのソフトウェアスタックをRustで掌握し、通信経路をマルチリンク化してブラックボックスを排除する我々のアプローチは、まさにこの最もリスクの高い領域(通信・制御モジュール)を技術的に迂回し、無害化するための必然的なステップなのである。

8. 結論

次世代ドローンのアーキテクチャ設計は、単なる「空を飛ぶRC機器」の組み立てから完全に脱却し、極限のリアルタイム性を要求される「空飛ぶエッジサーバー」としての高度なシステムインテグレーションの領域へと進化している。本研究の分析を通じて、以下の重要な結論が導き出される。

- 物理層と制御系の高度な融合: ブラシレスモーターの逆起電力を利用した双方向DShot通信によるRPMフィードバックは、ハードウェアの物理現象をデジタル領域で解析し、ソフトウェア的なノッチフィルタとして還元することで、ドローンの姿勢安定性を次元の異なるレベルへと押し上げている。

- **(妄想含む)Rustによる次世代制御アーキテクチャの確立: 既存のC++とRTOSによる複雑なミドルウェアから、メモリ安全性とゼロコスト抽象化を武器とするRustを用いたベアメタル開発への移行は、メモリ安全性違反やデータ競合に起因するシステムクラッシュのリスクを大幅に低減する(ただし unsafe ブロック、HAL、DMA、割り込み、電源異常、センサ異常、制御ロジックのバグ、リアルタイム締切超過の問題までは自動的に解決されない)。RTICフレームワークを活用し、ハードウェア割り込みに基づく厳格なタスクスケジューリングを実装することで、割り込み優先度と共有資源の設計・検証を体系的に行いやすくなり、異常時に安全側へ遷移する強靭な制御ループの構築が可能となる。

- ミッションと通信の抽象化およびマルチリンクの統合: コンパニオンコンピュータとMAVLinkを活用した権限の分離により、FCは機体の安定化という本質的タスクに専念する。その上位レイヤーでは、WIZ-IP20のようなRP2040ベースの変換モジュールを介し、TCP Clientモードを利用してCGNATを突破する5G通信、地球規模の接続を提供するStarlink、さらには遅延ゼロ・完全秘匿の光ファイバ通信が、動的かつシームレスにルーティングされる堅牢なネットワークアーキテクチャが実現する。

- 法規制の戦略的活用と経済安全保障への適応: 航空法における30m係留ルールの活用は、未検証のシステムに対する安全かつ合法的な実証実験の反復を可能にし、開発サイクルを劇的に加速させる。そして最終的に、ArduPilotのオープンアーキテクチャと、JAE JFB-100に代表される高信頼性・耐環境性を備えた純国産ハードウェアを結合することで、現代の安全保障環境において最も要求される「透明性の高いサプライチェーン」と「極限環境における動作保証」を両立した、次世代の無人航空機システムが完成する。

これら物理学、高度なソフトウェア工学、ネットワークアーキテクチャ、および運用上の法規制の全要素を俯瞰的に理解し、システム全体として最適化された設計思想を構築することこそが、未来の自律無人航空機開発を牽引するエンジニアに求められる不可欠な知見である。

9. 次回以降の予告:まずは「光ファイバ」「Starlink mini」「LTE回線」でPixhawkを動かしてみたい。

ここまで、純国産アーキテクチャやRustによる次世代制御系の構想といった「大風呂敷」を広げてきた。しかし、我々エンジニアの基本は「まず手を動かし、物理世界で動くものを証明する」ことである。

壮大な妄想を現実のものとするには、まずは既存のエコシステム上で通信インフラのハッキングを成功させる必要がある。そこで次回の記事では、手作りドローンのベースラインである「Pixhawk(ArduPilot)」環境に対し、とりあえず「光ファイバ通信」と「Starlink mini」と「LTE」を統合して実際に動かしてみる**という、泥臭い実証実験(ハンズオン)のプロセスを公開したいと思う。

- 上空のStarlink端末からCGNATを越えて地上局とセッションを張る具体的なルーティング手法

- ボビンから極細光ファイバを巻き出しながら、遅延ゼロ・完全秘匿でPixhawkのMAVLinkを叩く物理実装

机上の空論ではない、実戦的なシステムインテグレーションのリアルをお届けする予定だ。

10.【妄想】 高信頼性システムプログラミング:ベアメタルRustによるハードリアルタイム制御(次世代アーキテクチャの構想)

【筆者注】本章は現時点における筆者の「大いなる妄想(理想のアーキテクチャ)」を含みます

現在、ArduPilotやPX4といったC++/RTOSベースのミドルウェアがドローン業界の圧倒的なデファクトスタンダードであり、Rustを用いたベアメタルFCのフルスクラッチ開発は、世界的に見ても極めて挑戦的でクレイジーな未開拓領域(フロンティア)です。

本章で語る内容は、すでに完成したコモディティ技術の解説ではなく、「有事に際してブラックボックスを完全に排除し、極限の信頼性を担保するなら、我々はここまでやらなければならない」という一技術者の強烈な危機感と野望に基づく、**次世代アーキテクチャの要件定義(妄想)**としてお読みください。

既存のC++ベースのFCミドルウェア(ArduPilotやPX4)は極めて多機能であり、安定した飛行を提供する一方で、コードベースの肥大化に伴う実行遅延のリスクや、メモリアクセス違反に起因するシステムクラッシュの懸念を完全に排除することは難しい。このため、次世代の極限環境(防衛、宇宙、重要インフラ点検など)を想定したアーキテクチャとして、システムプログラミング言語であるRustを用いた「OSレス(ベアメタル)」のフライトコントローラ独自開発が、エンジニアリングの新たなフロンティアとして注目を集めている。

10.1 メモリ安全性とゼロコスト抽象化の適用

Rustの最大の特徴は、所有権(Ownership)と借用(Borrowing)という厳格なコンパイラールールにより、実行時のガベージコレクションを必要とせずにメモリ安全性を担保できる点にある。FCの内部では、IMUからのデータ読み取り、EKFによる行列演算、PIDの更新、そしてESCへの出力が、ミリ秒単位で同時並行的に処理される。C++環境で発生しがちなデータ競合やバッファオーバーフローは、ドローンの制御においては即座に墜落事故へと直結する。Rust の Safe Rust の範囲を用いれば、これらのメモリ由来のバグの多くをコンパイル時点で排除できるため、制御システムの信頼性が大きく向上する。ただし、ハードウェア直接操作や DMA 制御に必要な unsafe ブロックの内部、HAL クレートの実装、割り込みハンドラと共有資源のアクセスなど、Rust の所有権モデルの保証範囲外となる領域は依然として存在する。これらは設計と検証で個別に担保する必要がある。

さらに、Rustの「ゼロコスト抽象化」という設計思想は、リソースが限定されたマイクロコントローラ環境において絶大な威力を発揮する。宇宙空間や航空力学で必須となるクォータニオン(四元数)演算や複雑なカルマンフィルタの行列計算において、高度に抽象化された記述を用いても、コンパイラが最終的に生成するバイナリコードは、熟練したC言語プログラマが手書きで最適化したコードと同等かそれ以上に高速に動作する。これにより、可読性の高い安全なコードと、ミリ秒単位の応答速度を両立させることが可能となる。

10.2 RTICフレームワークによるハードリアルタイム性の保証

OSが存在しないベアメタル環境(標準ライブラリを持たない#![no_std]環境)において、ドローンの制御に不可欠な「ハードリアルタイム性」を保証するためには、タスクのスケジューリングと優先順位の管理が極めて重要になる。ハードリアルタイム性とは、「計算が速いこと」ではなく、「決められた時間(デッドライン)内に必ず計算を完了すること」を意味する。

Rustの組み込み開発エコシステムにおいて、この要件を満たすために最も強力なツールとなるのが、RTIC(Real-Time Interrupt-driven Concurrency)フレームワークである。RTICは、従来のリアルタイムOS(RTOS)のようなソフトウェア的なタスクスケジューラを持たない。その代わりに、STM32などのマイコンチップに物理的に組み込まれているハードウェア割り込みコントローラ(NVIC)を直接利用してタスクを管理する。

ドローンの制御ループの実装において、RTICは以下のように活用される。まず、「1kHz(1ms周期)」のハードウェアタイマー割り込みを設定し、この割り込みハンドラ内に「IMUのSPI読み取り」「PID演算」「DShotパルスの生成と出力」といった機体の生存に直結する最優先(Critical)タスクを定義する。一方で、フライトデータのSDカードへの書き込み(Logging)や、GPSの測位更新、コンパニオンコンピュータへのテレメトリ送信といった処理は、遅延が許容される低優先度タスクとして定義する。

RTICのコンパイル時の保証により、高優先度タスクが実行されている間は低優先度タスクは完全にブロックされ、高優先度タスクが終了した直後に、CPUの余白時間を利用して低優先度タスクが再開される。この仕組みにより、開発者は割り込み優先度と共有資源の競合関係をコンパイル時に検証可能となり、最悪実行時間(WCET: Worst-Case Execution Time)の解析と設計を体系的に行いやすくなる。ただし、WCET の実証的な担保には、各タスクの実行時間測定、スタック使用量の解析、DMA 完了タイミングの確認、センサ読み取り周期の検証といった、個別の測定と設計検証が必要である。RTIC は「締切違反を自動的に排除する魔法」ではなく、「締切違反のリスクを設計時に解析・検証しやすくするフレームワーク」として理解すべきである。

10.3 ハードウェアI/Oの論理的マッピングとデバッグ手法

ベアメタルRustでFCをフルスクラッチ開発する場合、STM32などのマイコンのピンアサインとペリフェラル(周辺機能)の選定、およびその抽象化がプロジェクトの成否を分ける。Rustのエコシステムでは、ハードウェア抽象化レイヤー(HAL)クレートが提供されており、これを用いることで型安全にハードウェアを操作できる。

- SPI (Serial Peripheral Interface): 姿勢制御の根幹となるIMU(ジャイロ・加速度センサー、例えばBMI270やMPU6000)との通信に使用される。I2C通信は配線数が少なく済むものの、バスの通信帯域幅が狭く、データ転送のレイテンシが制御ループのボトルネックとなるため、メガヘルツ帯での高速通信が可能なSPIの採用が必須である。

- UART (Universal Asynchronous Receiver-Transmitter): RC受信機からの操作信号(SBUSやCRSFプロトコル)の取得、およびGPSモジュールやコンパニオンコンピュータとのシリアル通信に使用される。

- Timer / PWM: ESCに対する制御信号(DShotプロトコル)の出力に使用される。Rustの強力な型システムを利用することで、出力数値を単なる整数ではなく「マイクロ秒のパルス幅」という明確な型として定義し、単位の誤認によるモーターの暴走を未然に防ぐことができる。

また、組み込み開発においてデバッグは非常にリソースを消費するタスクであるが、Rustのエコシステムにはdefmt(Deferred Formatting)という画期的なクレートが存在する。これは、マイコン側で文字列のフォーマット処理(printf等)を行わず、最小限のバイナリデータのみをデバッガ(probe-rs等)経由でPCへ送信し、PC側の豊富な演算能力を使ってログ文字列を復元する仕組みである。これにより、デバッグログの出力が制御ループのリアルタイム性に悪影響を与えることを防ぎつつ、システム内部の挙動を詳細に可視化することが可能となる。

11. 【妄言】OcuSync(映像送信技術) という戦略的死命線 ── 半導体問題としての再定義と全手段動員戦略

本章は今回の調査の中で、DJI社のコア技術体系である OcuSync が達成している偉業の技術的な高度さとそれを本邦が実現しようとする場合の事を戦略立てて考えるに当たり高度半導体技術のアプリケーションについてキャッチアップ方法の思索をするに当たり、私が経験の中で直面した技術的敗北感を感じた他の分野(APAA / LLM推論実行環境)でのキャッチアップにも有効と思われる戦略を提案したいので妄言として書き留めておきたい。

※本章はOcuSyncにどうやって追いつくかを考えた結果、半導体知財でのキャッチアップの方向に脱線します。

11.1 残された一つの空白(チョークポイント)か?

本記事ではここまで、フライトコントローラ、モーター、ESC、IMU、フレーム、コンパニオンコンピュータ、マルチリンク通信、そして経済安全保障観点から見た各コンポーネントの純国産化可能性について論じてきた。第7.3節のサプライチェーンリスクマッピングでは、機械的要素から半導体・ソフトウェア層に至るまで、リスク度の階層を整理した。

しかし、そこに意図的に置かなかった一つの行がある。長距離 RF 映像伝送、すなわち DJI が OcuSync ブランドで展開している 2.4/5.8 GHz 帯のドローン専用通信技術である。これを正面から論じれば、本記事の「純国産ドローンエコシステム」という主張は、たった一つの空白で完結を阻まれていることが浮き彫りになる。

本章は当初、この空白を「日本単独では構造的に獲得不能」「EU と組まなければ成立しない国家戦略」として論じる予定であった。しかし執筆の過程で2025年の地殻変動を直視し、論調は段階的に書き換えられた。さらに議論を深めると、より深い認識に至る。OcuSync 級の長距離 RF 映像伝送は、その技術的本質において、ドローン特化ベースバンド SoC という半導体の問題に集約される。そしてこの半導体は、ドローン産業の戦略的死命線である。日本が持つべき技術的資産・政策的予算・産業的能力の全てを、この一点に焦点化して投下することが、経済安全保障時代において必要かつ実装可能な戦略である——これが本章の最終的な主張である。

11.2 OcuSync が達成している数字

まず、何を相手にしているかを正確に把握する必要がある。

DJI が現行最新世代として展開している OcuSync 4(O4)の公称仕様を整理すると、DJI Goggles 3/N3 との組み合わせで、FCC 環境下 15 km、CE 環境下 8 km、SRRC 環境下 8 km の伝送距離を達成している。さらに上位機種である O4 Air Unit Pro では FCC 環境で 15 km の公称値を持つ一方、コミュニティの計測報告では 26 km 程度までの伝送が確認されている。これはハードウェアではなくソフトウェア的な制限とされる。

送信電力は 5.8 GHz 帯において FCC 環境で 33 dBm 未満(約 2 W)、CE 環境で 14 dBm 未満(約 25 mW)と、地域の電波法に応じて切り替わる。重要なのは、この数字である。FCC 環境での 33 dBm(2 W)という出力は、業務無線の世界では決して大きくない。LTE のマクロセル基地局が 40 W〜200 W 級であることを考えれば、DJI O4 の送信電力はマイクロセル相当に過ぎない。

それにもかかわらず、DJI O4 は FCC 環境で 15 km、実運用報告で 26 km という距離を達成している。遅延は DJI Goggles 3 と Racing モードの組み合わせで最小 15 ms、1080p/100fps の伝送品質を維持している。これは通信工学的に異常な数字である。WiFi 6 の規格上の最大有効距離が数百メートル、業務用 UHF 帯映像伝送機材が 5〜10 km 程度であることを比較対象とすれば、DJI O4 の達成は民生品として手のひらサイズの送受信機が、業務用機材を凌駕している状態である。

11.3 DJI の優位性の本質は出力電力ではない

ここで重要な誤解を解いておく必要がある。DJI O4 が 15 km 飛ばせる理由を「出力電力が大きいから」と理解するのは、技術的には誤りである。前述の通り、O4 の送信電力は 2 W に過ぎない。これは日本の自営無線局でも普通に許可される範囲の出力である。にもかかわらず DJI が独占的優位を保ってきたのは、出力電力以外の複数の独自最適化を統合実装しているからである。

これらの最適化を論じるにあたり、まず実証研究によって確認された事実と、業界の二次資料および技術的推論に基づく推定を明確に分離して記述する。

確認された事実(実証研究に基づく)

OcuSync の通信構造については、独立した実証研究による裏付けが存在する。2025年に韓国の漢陽大学と LIG Nex1(韓国防衛電子戦企業)の共同研究グループが、ICTC(IEEE 国際会議)で「Real-Time OcuSync Demodulator: A Software-Defined Radio Based Implementation」を発表した。彼らはソフトウェア無線(SDR)プラットフォーム(USRP B200-mini)を用いた実測スペクトログラム解析により、OcuSync 1.0 / 2.0 / 3.0 のアップリンク信号の構造を解明し、リアルタイム復調を実装した。

論文に示された実証データは以下の通りである。

| 項目 | OcuSync 1.0 | OcuSync 2.0 | OcuSync 3.0 |

|---|---|---|---|

| 変調方式 | QPSK / QAM(16〜64) | QPSK / QAM(16〜64) | QPSK / QAM(16〜64) |

| FFT サイズ | 128 | 128 | 256 |

| 占有サブキャリア | 73 | 73 | 145 |

| 総 OFDM シンボル | 6 | 7 | 7 |

| 復調ビット長 | 576 | 720 | 1,440 |

| サンプリングレート | 1.92 MHz | 1.92 MHz | 3.84 MHz |

論文の実証研究によって、以下が確認された事実として記述できる。

- OFDM ベース構造:OcuSync 1.0 / 2.0 / 3.0 の全バージョンで OFDM を採用

- 適応的変調:QPSK と QAM(16〜64)をチャネル条件に応じて切替

- Zadoff-Chu 同期信号:LTE の Primary Synchronization Signal と同じ方式を採用

- 世代ごとの帯域幅倍増:3.0 で FFT・サブキャリア・サンプリングレートが 2.0 から倍増する明確なスケーリング

- なお、論文の表に示された FFT サイズ(128/256)、サンプリングレート(1.92/3.84 MHz)、占有サブキャリア数(73/145)、総 OFDM シンボル数(6/7) といった具体的数値は、これらは論文の研究者が「OcuSync が LTE 系譜である」という仮定の下で復調器を構成するために選定したパラメータである。これらのパラメータで復調器を組んだ結果、コンステレーション図とビットストリームが正常に得られたため、LTE 系譜のスケーラブル設計であるという推定が間接的に裏付けられている、という性格の情報である。これは DJI 仕様書の入手やシリコン解析による直接確認とは異なる点に留意が必要である。

論文は明示的に「OcuSync は LTE システムの階層構造に類似した、スケーラブルな設計」と結論している。これは、本記事が論じてきた「DJI は Leadcore / Artosyn の LTE ベースバンド IP の系譜から OcuSync を派生させた」という認識を、独立した実証研究が裏付けたものである。

ただし、論文の射程は OcuSync のアップリンク信号の復調までであり、誤り訂正符号(FEC)の具体的方式、MIMO 構成、ACM の応答速度、選択的再送機構の有無、UEP の実装などは確認されていない。これらは論文の「Future work」として残されている。

業界資料および技術的推論に基づく推定

DJI O4 の独自最適化の本質を理解するためには、上記の確認された事実に加えて、業界の二次資料と通信工学的な推論に基づく推定を補完的に用いる必要がある。以下、各要素を「推定」として明示しながら整理する。

第一に、ACM(アダプティブ・コーディング・モジュレーション)の高速制御 ── 推定。DJI O4 はリンク品質をミリ秒単位で測定し、変調方式と前方誤り訂正レートを動的に調整していると推定される。これは LTE / 5G 規格にも存在する技術であり、標準実装の応答時間が 100 ms 単位であるのに対し、DJI は独自実装でこれを ms 単位にまで短縮していると業界資料では報告されている。ただし、応答速度の正確な数値は、DJI が公開していない独自仕様であり、SDR 実証研究でも未測定である。

第二に、MIMO(Multiple Input Multiple Output)の最適化 ── 推定。DJI O3+ 以降の機体は典型的に 2T4R アンテナ構成(送信2系統、受信4系統)を採用しているとされる。これは DJI 公式仕様および機体分解レポートに基づく推定である。送信機側と機体側のアンテナ配置は専用設計で、空力・電波特性の両面で最適化されていると推測される。ICTC 2025 論文は単一アンテナ受信での復調に限定されており、MIMO 構成は実証されていない。

第三に、動的周波数選択(DFS)の独自実装 ── 推定。DJI O4 は 5.170-5.250 GHz 帯と 5.725-5.850 GHz 帯の両方をスキャンし、干渉源を検出してリアルタイムにクリーンなチャンネルへ自動ホッピングするとされる。これは 5G NR の Listen-Before-Talk 機構と思想的には同じだが、DJI の実装速度と精度は規格を超えると推定される。具体的な切替アルゴリズムは公開されていない。

第四に、誤り訂正符号 ── 推定。DJI は LDPC(Low-Density Parity-Check)符号または Turbo 符号を採用しているとされる。これは LTE 派生のアーキテクチャから類推される標準的な選択であり、5G NR と同じレベルの符号化技術である。ICTC 2025 論文は復調までで止まっており、FEC 復号は未実装のため、具体的な符号方式と符号化率は実証されていない。

第五に、ビデオコーデックとの統合最適化 ── 部分確認。O4 Air Unit Pro が H.265 ビデオエンコーディングを採用していることは DJI 公式仕様から確認できる。1080p/100fps の高フレームレート伝送についても公称仕様として確認できる。しかし、エンコーダが伝送特性に合わせて誤り耐性のあるビットストリームを生成している点(Bフレーム不使用、PTS ベース締切管理等)は、機体分解レポートとビデオ品質の実測解析に基づく推定であり、ソースコードレベルでの確認はされていない。

第六に、選択的 ARQ と UEP(不均等誤り訂正保護)── 推定。フレーム種別ごとに異なる FEC 強度を適用する UEP の実装、および NACK ベースの選択的再送と PTS ベース締切管理の統合は、DJI O4 のグレースフル・デグラデーション挙動から逆推定される設計である。動画ストリームにおいて、I フレーム(独立復号可能な完全画像)の喪失は GOP(Group of Pictures)全体の崩壊を意味するが、B フレーム(双方向予測差分)の喪失は単一フレームの欠損に留まる。データ量比で見れば I フレームは GOP 全体の数%程度に過ぎない。この性質を最大限に活用するのが「重要度の高いフレームに強い FEC、重要度の低いフレームに弱い FEC」という不均等誤り訂正保護(UEP)の発想である。具体的には、LDPC 符号の符号化率を、I フレームには 1/3 程度の強保護、P フレームには 2/3 の中保護、B フレームには 5/6 の弱保護といった具合に動的に切り替える。母符号から重要度に応じてパリティビットを抜く Punctured LDPC や、変調シンボルの上位ビットと下位ビットで信頼度を分ける Hierarchical Modulation を組み合わせれば、平均ビットレートを犠牲にすることなく、I フレームの生存性を選択的に劇的に高めることができる。これに加え、DJI O4 はフレーム種別ごとの選択的 ARQ(再送要求)を統合し、NACK ベースで欠落パケットを名指しで要求する仕組みに、PTS(Presentation Time Stamp)ベースの締切管理を組み合わせていると推定される。これらは衛星通信業界(DVB-S2 等)の古典的手法を、ドローン映像伝送に統合した形と推定される。論考の説明力としては妥当であるが、公開されておらず、実証研究でも未確認である。

総括:確認された事実と推定の境界

整理すると、OcuSync について現時点で直接実測で確認された事実は、(i) OFDM ベース構造、(ii) QPSK / 16-64QAM の適応的切替、(iii) Zadoff-Chu 同期信号、(iv) 世代ごとの帯域幅拡大設計、の四点である。さらに、解析側仮定の下で間接的に裏付けられた構造として、LTE 系譜のスケーラブル設計が位置付けられる。これらは ICTC 2025 論文の実測解析と、その解析に用いられた復調器構成の妥当性によって示されている。

それ以外の DJI O4 独自最適化の詳細——ACM 応答速度、MIMO 構成、DFS アルゴリズム、誤り訂正符号、選択的 ARQ、UEP——は、業界資料と通信工学的推論に基づく推定である。これらの推定は、DJI O4 の観測される性能(15 km 伝送、15 ms 遅延、グレースフル・デグラデーション)を説明するために通信工学的に妥当な仮説であるが、独立した実証研究での確認は今後の課題として残されている。

しかし重要なのは、これらの推定が正しいか否かに関わらず、本章の主張の核心は変わらないという点である。OcuSync が LTE 派生のアーキテクチャを持ち、その上に独自の最適化レイヤを統合したシリコンとして実装されているという事実構造は、確認された情報だけでも十分に成立する。

そして、これらすべてに通底する事実がある。確認された事実と推定を併せて構成される DJI O4 の通信工学的優位の全要素は、シリコンに焼き込まれた専用ハードウェアアクセラレータとして実装されている。汎用 CPU でソフトウェア実装すれば、OS のスケジューラ・キャッシュミス・割り込み処理だけで数 ms〜数十 ms を消費し、glass-to-glass 15 ms という DJI O4 の達成は物理的に到達不可能である。同様に、汎用 CPU + GPU 構成では数十〜数百ワットの消費電力となり、ドローンに搭載できる SWaP-C(Size, Weight, Power, Cost)制約を満たせない。

つまり、DJI O4 の優位性とは、ベースバンド SoC の優位性そのものである。確認された LTE 派生アーキテクチャと、推定される独自最適化レイヤを、1チップに焼き込む設計能力こそが、DJI が10年以上かけて蓄積してきた本質的競争力である。

11.4 2025年の地殻変動 ── Artosyn / ArtLynk / OpenIPC、そして実測解析

OcuSync の独占を技術的に揺るがしている主体が、2025年に明確に複数現れた。順に整理する。

Artosyn AR-8030 と単一 SoC への統合

Artosyn(中国)は別名 Coolchip と呼ばれる、ファブレスの中国半導体ベンダーである。同社は 2011 年に合肥酷芯微电子(Hefei Coolchip Microelectronics)として設立され、画像信号処理(ISP)、ニューラルネットワーク処理(NPU)、そして無線通信ベースバンドの三領域に特化してきた。重要な歴史的事実として、Artosyn は DJI の Lightbridge / OcuSync の初代世代において、AR8001 DSP と AR8003 RF トランシーバを供給していた、まさに OcuSync の系譜のシリコン提供元である。後に DJI は Leadcore(LC1860C)と組んで P1 SoC を独自開発し独自路線を歩んだが、Artosyn 側もその後ほぼ同等のアーキテクチャ(ARM コア + Ceva LTE ベースバンド)を持つ AR8211 / AR-8030 を独立に発展させてきた。

その最新世代である AR-8030 は、RF ベースバンド・マルチプレクサ・プロトコルスタックを統合した1チップ SoC であり、150 MHz〜7 GHz の周波数対応、RISC-V 内部、低消費電力を特徴とする。これを採用した次世代デジタル VTX が 2025 年に一斉に市場投入された。Caddx Ascent(VTX 約 $35、ゴーグル約 $150)、BetaFPV ArtLynk(P1 Air Unit、6.5g、1080p60、glass-to-glass 約 60 ms、200 mW、公称距離 5 km 超)、STARTRC VT5、HGLRC Draco(公称 15 km、金属ハウジングによる高出力対応)、そして Walksnail Ascent までが同系列である。

これらに共通するのは、「DJI O3〜O4 と同等水準のデジタル映像伝送性能を、$30〜40 の VTX として量産化した」という事実である。HGLRC Draco の公称 15 km は、まさに DJI O4 の FCC 環境公称値と同水準である。

ArtLynk プロトコル ── マルチベンダー協調エコシステム

Artosyn AR803X チップセットの上位プロトコルとして、BetaFPV が主導する ArtLynk が事実上のマルチベンダー標準として浮上している。ArtLynk は「単一企業に属さない協調的 FPV エコシステム」を標榜し、KAP(Artosyn のコア技術提供子会社)が技術的下支えを提供する形で、複数ベンダーの製品が相互運用可能な仕様として整備されつつある。実例として、HGLRC Draco は当初独自仕様であったが、後に ArtLynk ファームウェア対応を発表し、BetaFPV 製品との互換性を獲得した。BetaFPV の P1 ファームウェア V2.0.5 以降では、明示的に他社 ArtLynk 機器との互換性が確保されている。

これは DJI の「閉じた専有プロトコル」とは本質的に異なる進化形態である。同一 SoC を複数ベンダーが採用し、上位プロトコル層で相互運用性を確保する、半導体業界では Wi-Fi や Bluetooth の生態系で見慣れた形であり、それがドローン映像伝送の世界に到来したわけである。

OpenIPC + WFB-NG ── 完全オープンソースの破壊的代替

しかし2025年の地殻変動の中で、本記事の経済安全保障論の文脈から最も重要なのは、OpenIPC + WFB-NG の存在である。

OpenIPC は、汎用 IP カメラ用 SoC を H.265 ビデオエンコーダとして転用し、改造 WiFi ブロードキャストスタック(WFB-NG: WiFi Forked Broadcast Non-Guaranteed)を組み合わせた、完全オープンソースのデジタル FPV 映像伝送システムである。受信側は標準的な USB WiFi アダプタを Linux PC に接続するだけで成立する。RTL8812au + 20dBi パッチアンテナで 20 km の伝送実績が報告されている。RunCam、EMAX、Eachine といった既存 FPV ベンダーが公式参加しており、ハードウェアとソフトウェアの両方が公開仕様である。

実装機能の精密な現状を整理する。OpenIPC + WFB-NG は、想像以上に高機能なオープンソーススタックである。具体的には以下の機能が標準実装済みである。

第一に、libsodium による完全な暗号化と認証。XSalsa20-Poly1305 等の現代的暗号アルゴリズムを採用し、drone.key と gs.key による事前共有鍵方式で全通信が暗号化される。これは標準機能であり、オプションではない。

第二に、動的 FEC と動的変調切替。リンク劣化に応じて、リンク中断なしで FEC 強度と変調方式を切替可能。リードソロモン系の FEC(デフォルトで 12 パケット中 4 パケット復元可、調整可能)を実装し、SIMD 最適化版は純 C 版の 5-10 倍高速。

第三に、自動 TX ダイバーシティ。複数 USB WiFi カードから RSSI ベースで最良のものを自動選択する。

第四に、双方向 MAVLink テレメトリと IPv4 トンネル。ビデオダウンリンクだけでなく、双方向のテレメトリと汎用 IP 通信が可能。トラフィックシェーパー対応で優先度制御も可能。

第五に、H.265 ネイティブエンコード。OpenIPC 対応カメラ(gk7205v200/300、IMX307/335/355 等)でハードウェアエンコードに対応している。

これらの機能は、業務用途・経済安保用途の基本要件をソフトウェアレベルでは既に満たしている。

DJI O4 と OpenIPC + WFB-NG の機能マップ ── 実証データに基づく精密比較

DJI O4 と OpenIPC + WFB-NG の機能ギャップを正確に評価するため、ICTC 2025 論文の実証研究結果を反映した機能マップを以下に整理する。各機能要素について、DJI O4 における根拠の性質(実測確認、解析仮定下での裏付け、業界資料・推論に基づく推定)を明示し、OpenIPC + WFB-NG の実装状況とギャップの深刻度を併記する。

| DJI O4 の機能要素 | DJI O4 における根拠 | OpenIPC + WFB-NG の実装状況 | ギャップの深刻度 |

|---|---|---|---|

| OFDM 変調 | 実測確認(ICTC 2025) | 実装(WiFi 標準) | 小 |

| Zadoff-Chu 同期信号 | 実測確認(ICTC 2025) | WiFi 標準同期(ZC ではない) | 中 |

| 適応的変調(QPSK / 16-64QAM) | 実測確認(ICTC 2025) | 実装(動的変調切替あり) | 小 |

| 世代ごとの帯域幅拡大設計 | 実測確認(ICTC 2025) | 該当なし(単一設計) | 参考情報 |

| LTE 系譜のスケーラブル設計 | 推定(解析側仮定で復調成功) | 該当なし(WiFi 系譜) | 参考情報 |

| ms 単位 ACM 高速制御 | 推定(業界資料) | 応答速度で劣る(秒単位) | 中 |

| 2T4R MIMO | 推定(DJI 公式仕様・分解レポート) | TX ダイバーシティのみ、真の MIMO なし | 大(HW 制約) |

| 動的 DFS(リアルタイムチャネルホッピング) | 推定(業界資料) | 未実装 | 大 |

| LDPC または Turbo 符号 | 推定(LTE 派生からの類推) | リードソロモン代替 | 中 |

| H.265 統合エンコード | 部分確認(DJI 公式仕様) | 実装済み | 小(ビットレート差は別問題) |

| 高ビットレート(25-50 Mbps) | 公称仕様確認 | 4-10 Mbps が上限 | 大(HW 制約) |

| 選択的 ARQ(NACK + PTS 締切管理) | 推定(挙動からの逆推定) | 未実装(ブロードキャスト型設計) | 極大 |

| UEP(Punctured LDPC + Hierarchical Modulation) | 推定(挙動からの逆推定) | 未実装(均等 FEC のみ) | 極大 |

| グレースフル・デグラデーション | 観測確認(実機挙動) | 限定的 | 大 |

| 暗号化・認証 | DJI 独自実装(公開されず) | 標準実装(libsodium) | 小(OpenIPC が透明性で優位) |

| MAVLink 統合 | DJI 独自プロトコル | 実装済み(双方向 + IPv4 トンネル) | 小(OpenIPC が汎用性で優位) |

この表の読み方として、以下の三つの分類が重要である。

第一に、ICTC 2025 論文で実測確認された機能は、OFDM 変調、Zadoff-Chu 同期信号、適応的変調、世代ごとの帯域幅拡大設計の四項目である。これらは OcuSync の本質的な信号構造として、確実な情報である。

第二に、解析側仮定の下で間接的に裏付けられた構造として、LTE 系譜のスケーラブル設計が位置付けられる。論文研究者が LTE 派生と仮定して復調器を組んだところ復調が成功したという、間接的な裏付けである。

第三に、業界資料・分解レポート・通信工学的推論に基づく推定として、ms 単位 ACM、MIMO 構成、動的 DFS、LDPC、選択的 ARQ、UEP、グレースフル・デグラデーションが残る。これらは DJI O4 の観測される性能を説明するための妥当な仮説であるが、独立した実証研究での確認はまだされていない。

そして、この表が示す DJI O4 と OpenIPC + WFB-NG のギャップは、二つの軸に明確に分けられる。

ハードウェア制約に起因するギャップ ── ソフトウェアでは突破不能

OpenIPC が DJI に追いつけていない領域の多くは、汎用 WiFi チップセット(RTL8812au 等)を流用しているハードウェア制約に起因する。具体的には、(i) 真の MIMO の不在、(ii) 高ビットレート(25-50 Mbps)の上限、(iii) ms 単位 ACM の不在、(iv) LDPC ハードウェアの不在、(v) 動的 DFS の不在——これらはすべて、汎用 WiFi チップ自体がドローン映像伝送に最適化された機能をハードウェアレベルで持っていないことが原因である。WFB-NG のソフトウェアスタックがどれだけ成熟しても、シリコンに存在しない機能は実装できない。

アーキテクチャ設計に起因するギャップ ── ソフトウェアで対応可能だが設計思想の再考が必要

一方、選択的 ARQ と UEP の未実装は、性質が異なる。WFB-NG はブロードキャスト型(受信側が複数想定)として設計されているため、選択的 ARQ(特定の受信側からの再送要求)とは設計上相性が悪い。UEP も、現状の均等 FEC 設計では対応していない。これらは技術的にはソフトウェアレベルで対応可能であるが、WFB-NG のブロードキャスト設計思想を再考する必要があり、コミュニティの設計判断と実装労力が課題となる。

OpenIPC が DJI を上回る領域 ── 透明性と汎用性

注目すべきは、OpenIPC + WFB-NG が DJI O4 を上回る領域も存在することである。

暗号化・認証は、OpenIPC が libsodium による現代的な暗号アルゴリズムを標準実装し、ソースコードレベルで透明性を確保しているのに対し、DJI は独自実装を採用しその仕様を公開していない。経済安保用途では、ソースコードで検証可能な OpenIPC の暗号化の方が、信頼性検証の観点で優位である。

MAVLink 統合も、OpenIPC が標準対応している双方向 MAVLink テレメトリと IPv4 トンネルにより、汎用的なドローン制御ソフトウェア(ArduPilot、PX4、QGroundControl 等)とそのまま連携できる。DJI は独自プロトコルを採用しているため、サードパーティ統合に制約がある。業務・経済安保用途では、OpenIPC の汎用性の方が運用上有利である。

戦略的含意 ── OSS スタック × 国産専用 SoC の組み合わせ

つまり OpenIPC + WFB-NG の現状は、こう整理できる。(i) 暗号化・認証・MAVLink 統合・基本伝送機能は実装済みで、業務用途の基本要件を満たし、一部領域では DJI を上回る透明性と汎用性を持つ。(ii) 画質・応答速度・MIMO の劣位は、汎用 WiFi チップ流用というハードウェア制約に起因し、ソフトウェアでは突破できない。(iii) 選択的 ARQ と UEP の未実装は、ソフトウェアレベルで対応可能だが、WFB-NG のブロードキャスト設計思想の再考が必要。

しかし重要なのは、この性能を数十人規模のオープンソースコミュニティが達成しているという事実である。Artosyn は中国の中堅ファブレス1社、OpenIPC は国際的なボランティア集団。いずれも、数十億ドル級の投資と数百人規模の専従エンジニアを抱えるとされる DJI の体制と比較すれば、桁違いに小さい主体である。OpenIPC が示しているのは、「ソフトウェアスタックの実装は数十人規模で可能、しかし完全な OcuSync 同等性能にはハードウェア専用化が必要」という、ハードウェアとソフトウェアの分担構造である。

この分担構造は、本章の戦略提言にとって決定的に重要である。日本が取るべき戦略は、(a) OpenIPC コミュニティへの組織的貢献(暗号化・認証・MAVLink 統合という既に優位な領域をさらに強化、選択的 ARQ と UEP のソフトウェア実装による補完)、(b) ドローン特化ベースバンド SoC の国産化(ハードウェア制約に起因するギャップを根本的に解消)、の二つの組み合わせである。これにより、OSS の透明性と国産シリコンの性能を両立する経済安保ドローン用通信基盤が、日本独自の経路として構築可能となる。

これは DJI のクローズドモデルにも、Artosyn のクローズド SoC モデルにも、純粋な OpenIPC モデルにも勝る、第三の経路である。経済安保時代の日本が選択すべき道筋として、論理的にも実装的にも整合する戦略構造を提示している。

実測解析という第三の地殻変動

そして本章で重要な認識を一つ加える。OcuSync はクローズドプロトコルではあるが、その通信構造は実測解析により把握可能である。前述の韓国 LIG Nex1 / 漢陽大学の研究グループは、OcuSync 1.0 / 2.0 / 3.0 のアップリンク信号を SDR で受信し、リアルタイム復調までを実装した。これは Korea Research Institute for defense Technology planning and advancement(KRIT)の防衛取得プログラム庁(DAPA)助成金(KRIT-CT-22-074)による国家防衛研究として実施されており、台湾有事や朝鮮半島有事を想定した、敵対勢力の DJI 系ドローンに対するジャミング、スプーフィング、信号傍受、コマンド乗っ取りを視野に入れた基礎研究である。

これはOcuSync の技術的優位が、絶対的なブラックボックスではなく、独立研究グループによる解析と再実装が可能な構造であることを示している。

Artosyn AR-8030 がシリコンレベルで OcuSync の代替を達成し、OpenIPC + WFB-NG が完全 OSS で類似機能を実装し、そして韓国の防衛研究グループが SDR でリバースエンジニアリングしている——これら 2025 年の地殻変動は、いずれも「OcuSync は再実装可能な技術である」ことを示している。問題は再実装の意思と組織的取り組みの有無であり、技術的不可能性ではない。

11.5 構造的不可能性の前提が崩れた

本章を当初、筆者は「目標A(通信主権の確保)はローカル5Gで現行達成可能、目標B(DJI O4の機動運用性能の超克)は日本単独では構造的に不可能、EU と組むしかない」という二段構造で書こうとしていた。

その「構造的不可能性」の根拠として挙げていたのは、(i) 投資規模 50億ドル累計、(ii) 数百人規模のエンジニアチーム、(iii) 量産規模の市場、(iv) 3GPP / ITU-R での標準化交渉力、の四つの障壁であった。しかし2025年の現実を直視すると、これらの障壁はいずれも実装的には突破されている。

| 当初想定した障壁 | 2025-2026 の現実 |

|---|---|

| 累計 50 億ドル投資が必要 | Artosyn が中堅ファブレス1社で AR-8030 を量産化、OpenIPC は OSS コミュニティで実装 |

| 数百人規模のエンジニアチームが必要 | OpenIPC コアコントリビューターは数十人規模 |

| 巨大市場による量産効果が必要 | $35 VTX として既に量産流通、価格競争力は分析的に成立 |

| 3GPP / ITU-R での標準化交渉力が必要 | ArtLynk はベンダー間のデファクトとして自律的に成立、3GPP 標準化を経ていない |

つまり、OcuSync 級の達成は、もはや国家戦略レベルの巨額投資・組織体制を必要とする領域ではなくなった。Artosyn は中国の中堅 SoC ベンダー1社が独力で達成し、OpenIPC は世界中のオープンソース貢献者数十人が達成している。これが2025年に起きた地殻変動の本質である。

11.6 三段階に分離された目標

これを踏まえると、経済安全保障の文脈で「DJI を超える」という議論は、二段階ではなく三段階に分離される必要がある。

目標A:通信主権の確保

DJI に依存しない通信経路を持つこと。ペイロードデータが特定国の事業者・サーバを経由せず、国内に閉じた経路で完結すること。サプライチェーン上の特定国依存の脱却を真面目に検討すること。これはローカル5G + WebRTC + マルチリンクの組み合わせで現行制度・技術下で達成可能であり、本記事の第6章および第7章で論じてきた領域である。なお、通信内容そのものの傍受耐性(暗号化強度、耐電子戦性能)は、より高度な要件として目標 B-2 で扱う。

目標B-1:民生品同等の高品質デジタル映像伝送

1080p、5〜15 km、低遅延(30〜60 ms 程度)、グレースフル・デグラデーションの実現。これには、(i) フレーム種別ごとの選択的 ARQ、(ii) Punctured LDPC + Hierarchical Modulation を組み合わせた UEP、(iii) ms 単位の ACM 制御、(iv) GOP 構造とプロトコル層の統合最適化が要求される。

これは2025年時点で Artosyn AR-8030 / ArtLynk / OpenIPC + WFB-NG によって既に技術的に実証され、量産価格 $30 台で市場流通している。日本がこれを獲得するために必要なのは、国家戦略レベルの長期投資ではなく、(a) 国内 SoC ベンダーの戦略的参入、(b) OpenIPC 等のオープンソースプロジェクトへの組織的貢献、(c) 業務用途特化の独自プロトコルレイヤの追加開発である。これは第11.9節で論じる戦略により、数年スパンの取り組みで実現可能である。

目標B-2:防衛グレードの暗号化・耐 EW・認証付き映像伝送

AES-GCM 暗号化、ファームウェア署名、QZSS L6E 統合、CRPA アンテナ対応、3GPP 標準準拠、純国産サプライチェーン、MIL-STD / DO-160 / EASA 等の型式認証を満たすシステム。Artosyn も OpenIPC も、ここには到達していない。Artosyn はクローズドな商用製品であってサプライチェーン透明性が無く、OpenIPC は WFB-NG レベルでは暗号化を実装しているがファームウェア署名や耐 EW 性能は未検証である。

この層は依然として国家戦略レベルの長期投資を必要とし、日本単独で完結させるのは困難である。本章で当初構想していた「日 EU 共同研究」の射程は、この目標B-2 に絞られる。Hexa-X-II、SNS JU、Drone Strategy 2.0 といった既存の EU 枠組みと連携する意義は、民生品レイヤ(B-1)ではなく、業務・防衛グレード(B-2)にある。

民間用途・産業用途・軽度の防衛運用では目標 A + B-1 で要件は満たされる。最高機密の作戦運用や電子戦環境での独立性が要求される領域でのみ、目標 B-2 が必要となる。

11.7 日本がやれていない、という別の問題

問題の所在は2025年に明確に変わった。「構造的に不可能だから諦める」ではなく、「技術的には十分可能なのに、ドローン特化ベースバンド SoC を設計する国内ベンダーが立ち上がっていない」という、極めて具体的な事業判断と産業政策の問題である。

デジタル FPV 映像伝送の市場プレイヤーを2026年時点で並べると、DJI、Walksnail(Caddx)、HDZero、BetaFPV、HGLRC、TJRC、STARTRC、Eachine、RunCam、EMAX、Skyzone、そして SoC レイヤの Artosyn / Coolchip まで、ほぼ全てが中国企業である。OpenIPC コミュニティには欧米の貢献者もいるが、製品化レイヤはやはり中国系ベンダーが厚い。一方、日本国内に該当領域のプレイヤーはほぼ存在しない。SoC レイヤのソシオネクスト・ルネサスエレクトロニクス・ソニーセミコンダクタソリューションズは民生 FPV 領域に参入していない。完成品メーカーの ACSL や ProDrone は、機体・FC 中心であり、独自 RF 映像伝送 SoC は持たない。OpenIPC への日本からの組織的貢献はほぼ皆無である。

なぜ立ち上がっていないか。理由は明確である。第一に、国内のドローン市場規模が SoC 専用設計の事業合理性を支えるほど大きくない。第二に、国内の経済安保ドローン市場がまだ政策的に立ち上がっていないため、需要保証が得られない。第三に、SoC 仕様を策定する側のシステム統合者(完成品メーカー)が国内に不在なため、要求仕様が定まらない。第四に、特定重要技術指定や K Program 対象化等の政策的後押しが無いため、リスクテイクの根拠が薄い。

これは半導体産業や家電産業で 1990 年代以降に繰り返してきたパターンの最新版の再演である。技術的には十分可能、ファウンドリも国内にある、しかし事業判断する企業が現れず、政策的後押しも無く、気がついたときには中国一強体制が成立する——この構図を、ドローン用ベースバンド SoC で再びなぞろうとしている。

11.8 半導体問題への収束 ── ファウンドリ三層構造

本章の主張を半導体の言葉で整理する。ドローン特化ベースバンド SoC を国産化するために、日本国内には既にファウンドリの三層構造が揃いつつある。

(i) 最先端ノード ── Rapidus

2027 年量産化目標の 2nm ノード。将来的なハイエンド版(高度な暗号エンジン、AI ペイロード統合、超低消費電力 SoC)の量産を担う。射程は 2027 年以降。

(ii) 量産成熟ノード ── TSMC 熊本工場(JASM)

2024 年稼働開始の 12-28nm ノード(2026年2月には熊本第二工場で3nmプロセスを投入すると発表している)。Artosyn AR-8030 が想定するプロセスノードと一致する。ドローン特化ベースバンド SoC の量産を担う中核ファウンドリとなる。

(iii) 少量多品種・試作 ── ミニマルファブ

産業技術総合研究所(AIST)が中心となり、ミニマルファブ推進機構を通じて日本国内で開発・産業化されている、従来の半導体メガファブとは根本的に異なるパラダイムの製造方式である。横河電機、アルゴグラフィックス、平田機工、岩谷産業ほか日本企業を中心に約140社のコンソーシアムが形成されている。

ミニマルファブの本質的革新は、(a) 0.5 インチ(12.5 mm)の極小ウエハーの採用、(b) クリーンルームを排除したシャトル方式(各装置を個別に密閉化)、(c) 装置1台が幅 30 cm 程度の小型化、(d) 1個から作れる究極の少量多品種への対応、にある。設置面積はオフィスビルの一室レベル、総額数十億円〜100億円程度で半導体製造ラインが構築できる。試作リードタイムは従来の数ヶ月から数日〜数週間に圧縮される。

ミニマルファブは現状成熟ノード(数百 nm 〜サブミクロン級)が中心であり、AR-8030 級の最終量産には対応していない。しかし、ドローン特化ベースバンド SoC の周辺 IC(電源管理、RF フロントエンド、暗号エンジン、防衛用途の特注 ASIC 等)の製造、設計試作・PoC、防衛少量生産には適合する。さらにミニマルファブは設置面積の小ささから、国内地理的分散配置が可能であり、台湾有事・地政学的危機による単一拠点リスクを物理的に回避できる、経済安保戦略として極めて意義の高いインフラである。

この三層構造を統合的に活用することで、ドローン特化ベースバンド SoC の国産化は、設計力・量産能力・少量多品種対応の全ての要件を国内で満たせる。設計力としては、ソシオネクスト、ルネサスエレクトロニクス、ソニーセミコンダクタソリューションズ、三菱電機(衛星通信由来の UEP 系譜)が候補となる。設計力もファウンドリも、国内に揃っている。

そしてここで決定的に重要な事実を加える。前節で論じた韓国 LIG Nex1 / 漢陽大学の実証研究が示した通り、OcuSync は LTE システムの階層構造に類似したスケーラブルな設計である。これは、日本国内の LTE / 5G ベースバンド研究の蓄積——情報通信研究機構(NICT)、NEC、富士通、三菱電機、KDDI 総合研究所、宇宙航空研究開発機構(JAXA)の衛星通信由来の知見——が、ドローン特化ベースバンド SoC の国産化に直接転用可能な要素技術であることを意味する。

つまり、本章で繰り返し論じてきた「要素技術は国内に蓄積されている」という主張は、もはや一般論ではない。OcuSync の構造が LTE 系譜であることが実証された以上、日本の LTE / 5G ベースバンド IP は、ドローン特化用途への転用が技術的に直結する。

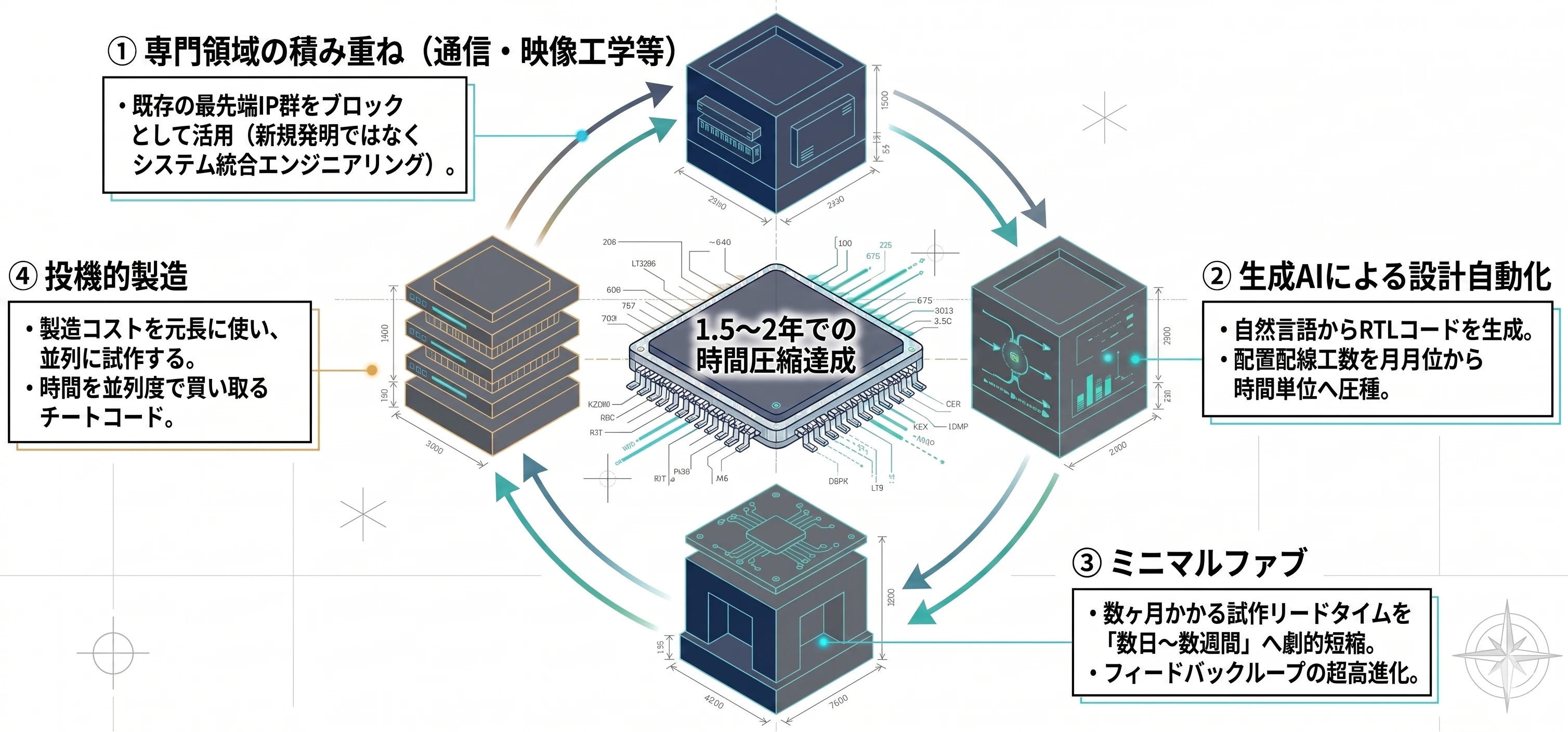

11.9 フィードバックループの高速化 ── 四位一体戦略

ここまでの論述で、ドローン特化ベースバンド SoC の国産化は技術的に可能であり、設計力もファウンドリも国内に揃っているという結論に至った。しかし正直に言えば、ここで一つの厳しい現実が立ちはだかる。それは時間である。

DJI と Artosyn / Coolchip が OcuSync 系のシリコンを完成させるまでに費やした時間は、およそ 10 年から 15 年である。LTE ベースバンドの IP 取得(Ceva、Leadcore 系譜)、シリコン量産化、OcuSync 独自最適化の継続的な蓄積、ファームウェア層の磨き込み——これらは連綿たる技術チェインの積み重ねであり、一足飛びに到達できるものではない。中国の半導体エンジニアリングコミュニティが、政策的支援と巨大な国内市場を背景に、地道にこの蓄積を進めてきた事実には、純粋に技術者として敬意を払うべきである。

問題は、日本が同じ道を 15 年かけて辿る時間的猶予を持たない、という一点にある。経済安全保障環境は急速に変化しており、台湾有事のリスク、サプライチェーン分断、地政学的危機の可能性は、5 年、10 年単位で待ってくれない。日本がいま追従の決断をしたとして、15 年後に同等水準に到達したのでは、その時には中国はさらに 2 世代先に進んでいる。通常のキャッチアップでは、構造的に追いつけない。

しかし、ここに本章の最終的な提言がある。2024 年から 2026 年にかけて、開発のフィードバックループを劇的に短縮し得る技術が同時に成熟期を迎えた。これらを通信工学の国内蓄積と組み合わせ、四位一体の戦略として統合する。

(i) 専門領域(通信工学)の要素技術 ── 国内蓄積の活用

OcuSync 級の機能を実現するために必要な要素技術は、いずれも既に確立された IP 群である。OFDM 変復調、MIMO 信号処理、LDPC 符号化、Punctured LDPC、Hierarchical Modulation、UEP、選択的 ARQ、ACM、H.265 統合——これらは衛星通信・放送通信・5G NR・宇宙通信の業界で長年研究され、IP として商用化されている技術である。日本国内の通信工学コミュニティ(情報通信研究機構、宇宙航空研究開発機構、NEC、三菱電機、東芝、KDDI 総合研究所など)は、その多くで世界最先端の知見を持つ。

要素技術自体は既に確立されており、「何の IP を引っ張ってきて、どう組み合わせれば OcuSync 級の機能が実現できるか」は、通信工学の専門家には想像可能な領域である。LDPC エンジンと UEP の組み合わせ、選択的 ARQ と PTS ベース締切管理の統合、MIMO 信号処理と動的アンテナ切替の協調——これらは未知の発明ではなく、確立された IP 群の最適な組み合わせと統合最適化の問題である。これは新規発明を必要とする分野ではなく、システム統合エンジニアリングの分野に属する。

中国が15年かけて連綿と積み上げてきたのは、まさにこの統合最適化の経験値である。その達成への敬意を払いつつ、しかし、生成 AI が要素技術の統合作業を劇的に加速させる時代には、同じ達成を15年かけずに実現できる経路が現れている。

(ii) 生成 AI による半導体設計自動化

NVIDIA の ChipNeMo、Synopsys の AI Copilot、Cadence の JedAI Platform、Google の AlphaChip 等、生成 AI を半導体設計に統合するツール群が 2024〜2026 年に商用化された。これらは以下を可能にする。

第一に、Verilog / VHDL コードの大規模言語モデル生成により、自然言語仕様から HDL コードへの自動変換が現実化した。RTL レベルで 3〜10 倍の高速化が観測されている。第二に、配置配線(Place & Route)の AI 最適化により、フィジカルデザインの工数が従来の数ヶ月から数日〜数時間に短縮された。AlphaChip 系で 20〜30 倍の短縮が達成されている。第三に、テストベンチ生成・カバレッジ解析・形式検証の AI アシストにより、検証工程が 2〜4 倍に加速している。第四に、HDL から対応するファームウェア API、デバイスドライバの自動生成も実用化が進みつつある。

ベースバンド SoC のように、シリコンとファームウェアが一体となって機能する領域では、生成 AI による統合設計の効果が特に大きい。LDPC エンジンの IP、OFDM 変復調 IP、MIMO 信号処理 IP、UEP のための Punctured LDPC エンジン、選択的 ARQ スケジューラ、H.265 統合エンコーダ——これらの既存 IP を自然言語仕様から AI が統合し、最適配置・配線まで自動化するという実装経路が、現実に組み立てられつつある。

(iii) ミニマルファブによる試作高速化

第11.8節で論じたミニマルファブの真価が、ここで発揮される。従来の TSMC 等のファウンドリでは、試作チップを起こすのに数ヶ月のリードタイムと数億円の試作費用が必要であった。これでは設計→試作→評価→修正のフィードバックループが年単位になり、生成 AI による設計高速化の効果が、製造リードタイムで完全に相殺されてしまう。

ミニマルファブは、シャトル方式による各装置の個別密閉化と 0.5 インチウエハーの採用により、試作リードタイムを数日〜数週間に圧縮する。1個から作れる経済性は、フィードバックループ1サイクルあたりのコストを劇的に下げる。生成 AI が短期間で新バージョンの RTL を生成し、数日〜数週間でミニマルファブから実物のシリコンが返ってくる。従来は 1 サイクル 6 ヶ月〜1 年だったものが、1 サイクル 1 ヶ月以下になる可能性がある。試作リードタイム単体では 5〜15 倍の高速化が見込める。

(iv) 投機的製造による並列探索

ここに、四つ目の戦略的概念を加える。投機的製造(Speculative Manufacturing)の導入である。

CPU 設計の世界には「投機的実行(Speculative Execution)」という概念がある。条件分岐の予測が成功するか失敗するかを事前に確定できないとき、両方の分岐先を並列に計算しておき、後で正しい方を採用し、誤った方は破棄する。計算リソースを冗長に使う代償として、実行時間の遅延を隠蔽する手法である。

この発想を半導体製造工程に持ち込んだのが「投機的製造」である。設計の分岐ポイント——LDPC 符号化率の選択、MIMO 構成の選択、アンテナ配置の選択、ARQ スケジューラのパラメータチューニング——これらの分岐を、逐次的に1版ずつ試作するのではなく、複数バージョンを並列に試作してしまう。実機評価の結果、最良版を採用し、他は破棄する。製造コストを冗長に使う代償として、開発期間を劇的に圧縮する。

従来の半導体製造では、1版あたりの試作コストが数百万〜数千万円規模であったため、複数バージョン並列試作は経済合理性が成立しなかった。しかし、ミニマルファブの登場で1版あたりの製造コストが1〜2桁低減すると、投機的製造が初めて経済合理的な戦略となる。生成 AI が設計バージョンを大量自動生成し、ミニマルファブが並列試作し、実機評価で最良版を選択する——これは半導体設計史上前例のない、生物進化のアルゴリズムに近い設計探索である。

戦略的に最も重要な点は、これが DJI / Artosyn の15年の連綿たる蓄積に対する、構造的な代替戦略となることである。中国は逐次試作で15年かけて経験値を蓄積した。日本は投機的製造により、並列度を時間軸の代替手段として動員することで、同等の探索空間を1〜2年で踏破する経路が開ける。「時間を並列度で買う」という、政策的予算と AI 設計能力と国内ミニマルファブインフラがあって初めて成立する戦略である。

経済合理性の構造を確認しておく。投機的製造で並列度を 5〜10 倍に上げた場合、製造コストは数千万〜数億円規模で増加する。一方、開発期間が1〜2年短縮されることの戦略的価値は、防衛調達・経済安保用途・輸出機会・地政学的優位性を含めれば、数百億円規模である。経済合理性は明らかに成立する。ただし、この差を民間企業単独で吸収するのは困難であり、経済安全保障推進法の特定重要技術指定と K Program 等の政策的予算が、投機的製造の経済構造を支える基盤となる。

四位一体による定量的効果

これら四要素を統合した場合のフィードバックループ短縮効果を、試算的に整理する。(筆者は半導体業界の経験は無く、調査の結果の想定・妄想で記述している事にご留意願いたい。)

| 開発フェーズ | 従来の所要時間 | 四位一体戦略 | 短縮率 |

|---|---|---|---|

| 仕様策定 | 3〜6ヶ月 | 1〜2ヶ月 | 3〜5倍 |

| アーキテクチャ設計 | 3〜6ヶ月 | 1〜2ヶ月 | 3〜5倍 |

| RTL 設計と検証 | 12〜18ヶ月 | 3〜6ヶ月 | 3〜5倍 |

| ハードウェアエミュレーション | 6〜9ヶ月 | 2〜4ヶ月 | 2〜3倍 |

| 物理設計 | 6〜9ヶ月 | 1〜2ヶ月 | 5〜10倍 |

| シリコン試作と評価(並列) | 12〜18ヶ月 | 3〜6ヶ月 | 5〜20倍 |

| ファームウェア統合と検証 | 6〜12ヶ月 | 3〜6ヶ月 | 2〜3倍 |

| 合計(動くシリコンまで) | 48〜78ヶ月(4〜6.5年) | 14〜28ヶ月(1.2〜2.3年) | 3〜6倍 |

楽観的シナリオ(並列度 5〜10 倍を最大限活用、複数サブブロック並列開発、政策予算最大投入)では、動くシリコン完成までを 8〜18 ヶ月(0.7〜1.5 年)まで圧縮できる可能性がある。

ただし、これは「動くシリコン」の達成までの期間であって、商用品質達成までは追加で 2〜3 年、DJI O4 級の独自最適化の完全達成までは追加で 3〜5 年を要する。最初の動くシリコンが手元にあれば、そこから先は実機運用しながらの継続的改良サイクルに入れる。中国が連綿と積み上げてきた実機改良の出発点に、日本は 1.5〜2 年で立てる可能性がある。勝負は「動くものを作る最初のフェーズ」にあり、ここに四位一体戦略が圧倒的な優位を持つ。

そして強調しておきたい。この戦略は、中国の技術的達成を侮るものではなく、むしろ深く敬意を払った上での代替経路の提案である。中国が連綿と積み上げた技術チェインの価値は、技術者として認めるべきである。日本が同じ道を15年かけて辿るのは時間的に不可能であり、また経済合理的でもない。異なる道筋——通信工学の国内蓄積 × 生成 AI × ミニマルファブ × 投機的製造——による独自のキャッチアップ戦略こそが、経済安全保障時代の日本に求められる解である。

11.10 リードタイムの絶対性 ── 半導体は危機を待てない

本記事の第7.3節では、サプライチェーンリスク評価において、ハイレート LiPo バッテリーを「リスク度:極高」、半導体・通信モジュールを「リスク度:高」として整理した。リスク度のラベルとしては素材の方が高いが、ここで本章の最終局面において、リスクの性質を時間軸の観点から再評価する必要がある。

素材問題と半導体問題は、経済安保危機顕在化時の対応可能性において、根本的に性質が異なる。

素材問題は、ある程度の在庫消費で時間稼ぎが可能であり、代替経路の探索が可能であり、緊急増産が部分的に可能、という特性を持つ。LiPo バッテリーの主要原材料が遮断されても、国内在庫で数ヶ月は凌げる。代替セル化学(全固体電池等)への移行は時間がかかるが、漸進的に進行する。素材問題は確かに深刻だが、危機顕在化後にも対応する余地がある性質の問題である。

しかし、半導体問題は構造的にこれと異なる。危機顕在化時の半導体不足は、在庫で凌ぐにも限界があり、緊急増産には物理的に短縮できないリードタイムが存在する。たとえ生成 AI と国内ミニマルファブと投機的製造を全動員し、政策的予算と人材を最大限集中投下したとしても、動くシリコンが完成するまでに最低 1.5〜2 年、商用品質達成までに合計 3.5〜5 年、配備可能な状態になるまでに 4.5〜6 年を要する。これが、半導体製造工程の物理的下限である。

一方、地政学的危機の進行速度は、半導体開発のリードタイムよりも遥かに速い。歴史的事例を見れば、ロシア・ウクライナ戦争は開戦から戦況の決定的変化まで数ヶ月単位で進行した。半導体規制のような経済的制裁措置でも、政策発動から影響の顕在化までは1〜2年単位。台湾有事を想定したシナリオ研究では、危機顕在化から決定的局面までは6ヶ月から2年程度と想定されることが多い。

つまり、危機顕在化を待ってから半導体開発を始めたのでは、危機の進行速度に対して構造的に間に合わない。危機顕在化時に「ドローン特化ベースバンド SoC が必要だ」と認識しても、その時点から開発を始めて配備されるのは早くて4〜5年後である。その頃には、危機は既に決定的な局面を超えている可能性が高い。

これが、半導体問題が経済安保において素材問題よりも優先度が高い構造的理由である。素材問題は深刻だが「危機が来てから対応する余地が部分的に残る」のに対し、半導体問題は「危機が来る前に手元に動くシリコンを持っておかなければ、構造的に間に合わない」という、絶対的なリードタイムの制約を持つ。

これは「将来の不確実な危機に備える」という抽象的な議論ではない。「危機顕在化時に、物理的に間に合わなさが確定している」という具体的な計算の問題である。経済安全保障推進法の特定重要技術指定、K Program 予算、国内ファウンドリの三層活用、生成 AI × ミニマルファブ × 投機的製造の四位一体戦略——これら全てを動員して、今、平時のうちに、ドローン特化ベースバンド SoC の国産化に着手しなければならない理由は、ここにある。

「いつ危機が来るか分からないから、念のため備える」のではない。「危機が来てからでは確定的に間に合わないから、危機が来る前に動くシリコンを手元に持っておかねばならない」のである。これは選択ではなく、リードタイム計算が要求する必然である。

中国の DJI / Artosyn が10〜15年かけて積み上げてきたのは、まさにこの「平時の蓄積」である。彼らは危機顕在化を待たず、平時のうちに連綿と開発を進めて、今の競争優位を確立した。そして韓国の LIG Nex1 / 漢陽大学のような同盟・友好国の防衛研究機関も、平時のうちに OcuSync のリバースエンジニアリングと電子戦応用研究を進めている。日本がこの遅れを取り戻すための窓は、依然として開いているが、その窓の幅は、半導体開発の物理的リードタイムによって規定されている。今着手すれば 4.5〜6 年後に配備可能、今着手しなければ未来永劫間に合わない——これが、半導体経済安保論の冷徹な算術である。

11.11 残された空白を直視するということ ── ドローンの戦略的死命線として

本章を執筆した動機を、最後に率直に述べる。

本記事の第1章から第8章までの本論は、純国産ドローンエコシステムの実装可能性を論じる、前向きで構築的な議論であった。各論点で純国産化の道筋を示してきた。

しかし、長距離 RF 映像伝送だけは、当初現状の日本に解がないと考えていた。執筆の過程で2025年の Artosyn / ArtLynk / OpenIPC を直視し、論調は変わった。構造的に不可能なのではない、技術的には十分到達可能な領域に降りてきている、問題は日本にこの領域を担う主体が立ち上がっていない、産業政策と業界構造の不作為である——こう論調を組み直した。

そして本章の最終的な結論として、もう一段深い認識に至る必要がある。

ドローンからの長距離安定映像伝送は、ドローンの価値を決定する核心的機能である。フライトコントローラの安定性、モーターの効率、フレームの空力——これらに性能差があっても、価格差で吸収可能な範疇に収まる。しかし、「どれだけ遠くまで、どれだけ安定して映像が見えるか」は、ドローンを玩具から業務機材へ、業務機材から経済安保デバイスへ、経済安保デバイスから軍事資産へと階層的に区分する決定的な軸である。DJI が世界市場の7〜8割を独占している直接的原因も、機体性能でも価格でもなく、OcuSync の通信品質に集約されている。

そして本章で繰り返し論じてきた通り、この決定的機能の優位の全要素は、ベースバンド SoC というシリコンに焼き込まれている。OFDM、MIMO、LDPC、UEP、選択的 ARQ、ACM、H.265 統合——通信工学の最先端の集積が、1〜2 個のチップに統合されている。ドローン特化ベースバンド SoC は、ドローン産業全体の戦略的死命線である。

加えて、本章で論じてきた「ドローン特化ベースバンド SoC の国産化」は、自軍ドローンの構築のみならず、対無人機(Counter-Drone)能力の獲得にも直結する。OcuSync の構造を実装的に理解できるからこそ、それを傍受・解析・無効化する電子戦能力も獲得できる。前述した韓国 LIG Nex1 サイバー電子戦 R&D 部門の OcuSync リバースエンジニアリング研究は、まさにこの両面戦略の体現である。日本の防衛装備庁(ATLA)、情報通信研究機構(NICT)、関連防衛企業が、同等の研究をどこまで進めているかは、公開情報からは判別困難である。しかし、本章で論じてきた半導体国産化戦略は、自軍ドローンの構築(攻撃側)と Counter-Drone 能力(防御側)の両面で同時に成立する戦略である。OcuSync 級プロトコルを設計できる能力は、それを破壊する能力と表裏一体である。経済安保半導体戦略は、純粋な産業政策論を超えて、実戦的な防衛能力の問題でもある。

日本がこの領域で遅れを取っているという事実を、改めて経済安保の観点から評価しなおす必要がある。これは「重要ではない領域で遅れている」のではない。これは「ドローンの価値を決定する最重要機能で遅れている」のである。経済安全保障推進法の特定重要技術指定、重要技術育成プログラム(K Program)、防衛省 ATLA との共同研究、TSMC 熊本工場・Rapidus・ミニマルファブの三層活用、生成 AI による設計自動化、投機的製造による並列探索——本章で提示してきたこれら全てのキャッチアップ手段は、この最重要機能を獲得するためにこそ動員される正当性を持つ。

中国が連綿たる15年の積み重ねでこの領域を達成したことには、純粋に技術者として敬意を払うべきである。彼らの戦略眼は正しかった。ドローンの価値を決定する機能だからこそ、15年を投じる価値があると判断した。日本は同じ戦略眼を15年遅れて持つことになる。しかし、その差を「同じ道を辿る」のではなく、「異なる戦略で代替する」ことは、生成 AI と国内ミニマルファブインフラと投機的製造の組み合わせによって、技術的に可能になっている。

提示してきたキャッチアップ手法は、それぞれ単独では補完的な意味しか持たない。生成 AI だけでは試作リードタイムを圧縮できない。ミニマルファブだけでは設計自動化はできない。投機的製造だけでは経済合理性が成立しない。通信工学の国内蓄積だけでは、シリコンに焼き込む実装力にならない。しかし、これら全てを組み合わせ、ドローン特化ベースバンド SoC という極めて焦点化された対象領域に集中投下するならば、それぞれの手段が相互補完的に機能し、全体として圧倒的な効果を生む。

これは「全ての手段を動員する」という総花的な提言ではない。これは「ドローン産業の戦略的死命線という、極めて焦点化された一点に、全ての手段を集中投下する」という、対象領域の特定とリソース集中の論理である。リソースは常に有限であり、政策の本質はどこに集中投下するかの判断である。ドローン特化ベースバンド SoC は、その集中投下に値する戦略的価値を、議論の余地なく持っている。

そして本章の前節で論じた通り、この投資判断には絶対的なリードタイムの制約がある。素材問題と異なり、半導体問題は危機顕在化を待っては構造的に間に合わない。今、平時のうちに着手しなければ、未来永劫間に合わない。これは選択ではなく、リードタイム計算が要求する必然である。

筆者にも 7〜8 年前に「DJI Mavic 2」を飛ばした経験がある。当時の操作時、数 km も遠くの機体の映像が手元で HD 品質ではっきりと見えた。多少なりとも無線や映像伝送の心得があった筆者の経験の中でも、この映像伝送の技術は他のシステムと比較して群を抜いていた。なぜこんなことができるのか本当に驚いたことを思い出す。今思えば、OcuSync の恩恵をその時に受けていたのだと、本調査を通して深く理解した。

そして本章を書き終えた今、深く理解したことがある。あの驚きの正体は、DJI が10年以上かけて磨き上げた通信工学の集大成であり、シリコンに焼き込まれた IP の統合最適化であった。同時に、もう一つ理解したことがある。あの驚きを再現する技術は、もはや DJI だけのものではない。Artosyn が同等のシリコンを $30 台で量産している。OpenIPC が完全 OSS で類似機能を実装している。韓国の防衛研究機関が SDR でリバースエンジニアリングしている。生成 AI が設計を加速する。ミニマルファブが試作を加速する。投機的製造が並列探索を可能にする。通信工学の知見は国内に蓄積されている。OcuSync が LTE 派生であることが実証された以上、日本の LTE / 5G ベースバンド IP は直接転用可能である。

問題は、これらを統合してドローン特化ベースバンド SoC の国産化を主導する主体が、国内に立ち上がるかどうか、その一点である。設計力もファウンドリも国内に揃っている。生成 AI ツールも国際的に利用可能である。ミニマルファブは産業技術総合研究所と横河電機等の連携で実用化フェーズに入っている。経済安全保障推進法の枠組みも整備されている。欠けているのは、この最重要機能を国内で獲得するという意思だけである。

OcuSync という空白は、半導体問題として、戦略的死命線の問題として、再定義された。埋めるかどうかは、技術の問題ではなく、意思の問題である。本章はその意思を呼び起こす一文として書いた。

そしてその意思を呼び起こすことは、残された時間との競争でもある。リードタイム計算が示す通り、今着手すれば窓は開いている、今着手しなければ窓は閉じる。これは抽象的な未来論ではなく、半導体製造工程の物理的下限が要求する具体的な算術である。

筆者は本記事の冒頭で「研究仲間募集」と書いた。本章を書き終えた今、この呼びかけの射程は以下のように決定的に明確になった。ドローン特化ベースバンド SoC の国産化に、共に挑む仲間を探している。半導体設計エンジニア、生成 AI 開発者、通信工学研究者、ミニマルファブ運用者、経済安保政策研究者、防衛・産業界の意思決定者——あらゆるレイヤで、この一点に集中投下する戦略への参画者を募りたい。本論考が誰か別の口から、別の筆から展開され、現実の半導体国産化として実装される日が来ることを、本記事は最後に願って閉じる。

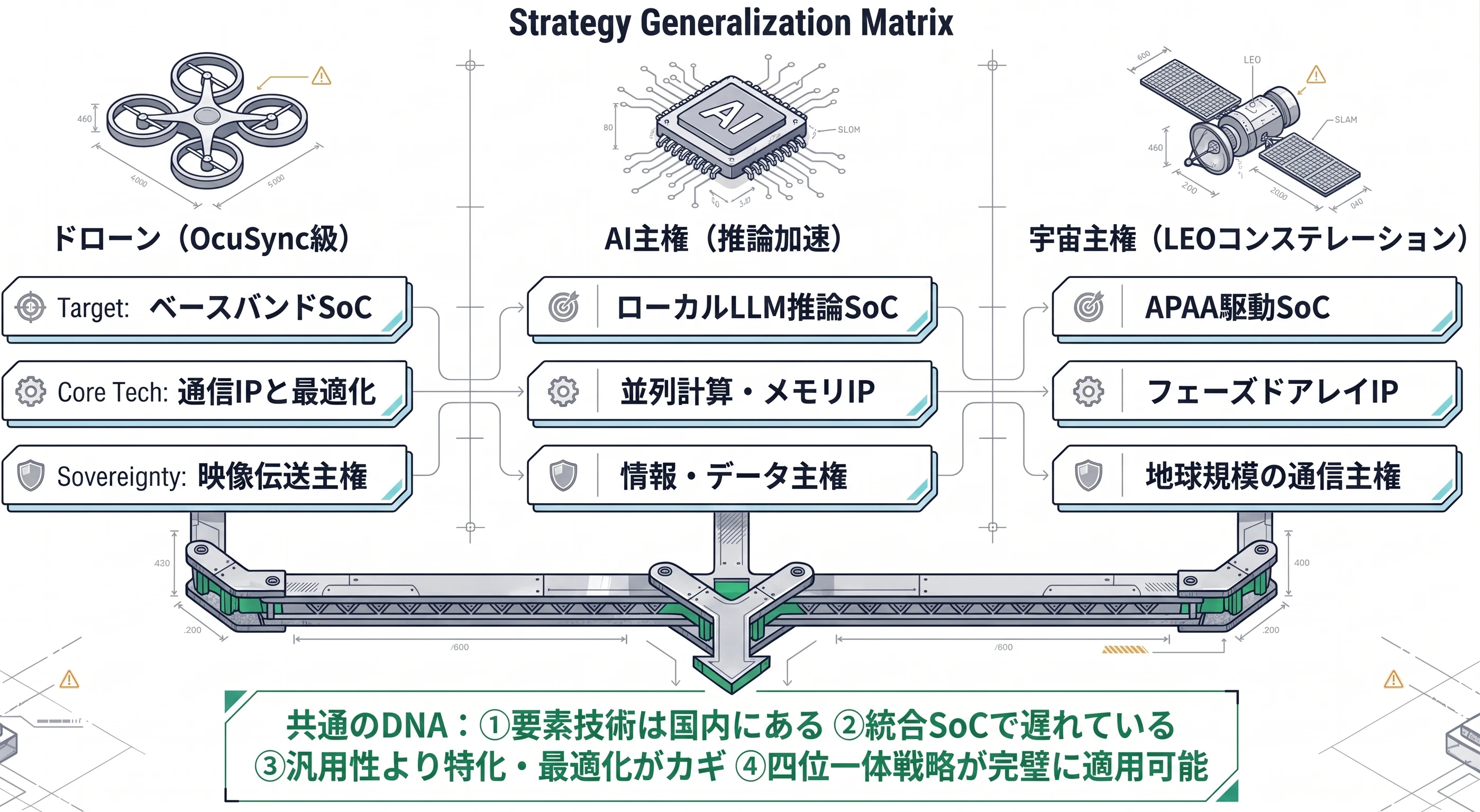

11.12 補論 ── 四位一体戦略の一般化と、AI 主権・通信主権への含意

本章で提示してきた四位一体戦略——通信工学の国内蓄積 × 生成 AI × ミニマルファブ × 投機的製造——は、ドローン特化ベースバンド SoC に固有の戦略ではない。より一般的に、日本が戦略的死命線で遅れを取っている半導体領域全般に適用可能な、汎用的なキャッチアップ方法論である可能性がある。

この戦略が適用可能な条件を抽象化すると、(i) 対象領域が戦略的死命線であること、(ii) 要素技術が国内に蓄積されていること、(iii) 統合 SoC レベルで海外依存が成立していること、(iv) 逐次キャッチアップでは間に合わない時間的制約があること、の四点に整理できる。これらの条件を満たす半導体領域として、ドローン特化ベースバンド SoC 以外にも複数の候補が想定される。自動運転特化 SoC、量子古典ハイブリッド制御 SoC、暗号アクセラレータ SoC、5G/6G ベースバンド SoC、AI 推論エッジ SoC——これら全てが、要素技術は国内にあり、統合 SoC で遅れを取り、戦略的死命線である、という構造を共有している。

しかし、これらの中で特に直近で戦略的重要性が急速に高まっているのは、二つの領域である。一つはローカル LLM 実行特化 SoC(推論加速 SoC)、もう一つは APAA(Active Phased Array Antenna)駆動 SoC である。前者は AI 主権の実装基盤、後者は通信主権の物理レイヤーを構成する。本補論では、これら二つを例として、四位一体戦略がもたらす含意を、半導体産業論を超えた AI 主権・通信主権論まで拡張して論じる。

AI 半導体産業の構造変化 ── CUDA の呪縛が解かれた

ローカル LLM 推論 SoC への日本の参入を論じる際、これまで暗黙の前提として存在していた最大の障壁は、NVIDIA の CUDA エコシステムであった。CUDA の真の強さは、ハードウェア性能ではなく、10年以上の蓄積による開発者基盤、ライブラリ群、最適化ノウハウの総体である。日本が AI 半導体に参入しても、この CUDA エコシステムに対抗するソフトウェア資産を構築するのは現実的に不可能、というのが2010年代の業界認識であった。

しかし、2022〜2026年の AI 産業の劇的な変化により、この認識は構造的に書き換えられた。

2010年代の AI 産業は、用途が多様で予測困難な状態であった。画像認識、音声認識、自動運転、レコメンドエンジン、ゲーム AI、機械翻訳——どれが本命か誰にも分からず、研究者は新しいアルゴリズムを試行し、エンジニアは特殊なネットワーク構造を実装した。「あらゆる AI 用途に対応する汎用基盤」としての NVIDIA GPU が圧倒的優位を持った理由は、この用途多様性に対応できる汎用性にあった。CUDA エコシステムの広範さこそが、NVIDIA の経済的堀を構築していた。

しかし2022年の ChatGPT 登場以降、状況は決定的に変わった。**生成 AI、特に LLM 推論が、AI の経済価値の大部分を占める「キラーアプリ」**として確定した。OpenAI、Anthropic、Google、xAI、Meta、Mistral、DeepSeek の収益構造、企業の AI 投資先、エンドユーザの AI 利用パターン——すべてが LLM 推論を中心に再編されている。2026年現在、AI ハードウェアへの需要の大部分は、Transformer アーキテクチャの推論ワークロードに集約されている。

この構造変化の戦略的含意は決定的である。用途が LLM 推論に集約されると、必要な演算パターンは極めて限定的になる。Transformer アーキテクチャの行列乗算、KV キャッシュ管理、アテンション計算、INT8 / INT4 / FP4 量子化推論、連続バッチング(continuous batching)——これらだけ高速に実行できれば、汎用性は不要である。CUDA の堀の本質であった「広範な汎用性」が、用途集約により構造的に不要になった。

この変化を実証する形で、CUDA に依存しない推論専用 SoC が2024〜2026年に次々と市場で成功している。Groq LPU は独自の Tensor Streaming Processor アーキテクチャで CUDA を全く使わず、LLM 推論において NVIDIA H100 比較で10倍以上のスループットと遅延性能を達成、Groq Cloud として商用化された。Cerebras WSE-3 はウエハースケールエンジンの独自設計で、Llama 70B の推論を NVIDIA を凌駕する速度で提供している。Etched Sohu は Transformer アーキテクチャに完全特化した ASIC で、汎用性をほぼ捨てて H100 比較で20倍以上の推論性能を主張する。SambaNova、Tenstorrent も同様の方向性で企業向け LLM 推論市場に食い込んでいる。

これらの成功事例は、CUDA エコシステムへの対抗が、もはや AI 半導体参入の必須条件ではないことを示している。LLM 推論に特化した SoC を作り、vLLM、TensorRT-LLM、SGLang 等のオープンソース推論フレームワークから直接呼べるようにし、PyTorch / Hugging Face エコシステム、ONNX / OpenXLA 等の中間表現への対応さえ確保すれば、CUDA を一切使わずに LLM 推論市場に参入できる。

これが日本の AI 半導体参入にとって持つ意味は決定的である。これまで日本が AI 半導体に参入できなかった最大の障壁——CUDA エコシステムへの対抗ソフトウェア資産の構築——が、構造的に不要になった。LLM 推論に特化した SoC を、PyTorch / vLLM 等の標準推論スタックに対応させるだけで、市場参入が可能である。これは2010年代には想像もできなかった、産業構造の根本的な変化である。

さらに、この構造変化は日本の半導体産業の歴史的強みと整合する。日本の半導体産業は、1990年代以降、「汎用化と巨大化」の競争では米国・台湾に敗北してきたが、「特化と最適化」の競争領域では伝統的に強い。センサ(ソニーCIS)、アナログ・ミックスドシグナル(ローム、ルネサス)、パワー半導体(東芝、ロームの SiC)、車載特化 SoC(ルネサス R-Car)——これらはいずれも、汎用性ではなく特化と最適化で世界市場に存在感を持つ領域である。

LLM 推論特化 SoC は、まさにこの「特化と最適化」の競争領域である。汎用性で勝負しない、Transformer アーキテクチャの推論だけに特化する、低消費電力と高スループットを最適化する——これらは日本企業の伝統的強みが活きる設計戦略である。CUDA の呪縛が解かれたことにより、日本の半導体産業の歴史的強みが、AI 時代に再び活きる文脈が成立した。

ローカル LLM 推論 SoC が AI 主権に持つ意味

クラウドベースの大規模言語モデル(OpenAI、Anthropic、Google 等)に依存することは、データ主権の喪失、地政学的危機時の遮断リスク、推論コストの構造的高止まり、モデル選択の不自由といった経済安保上のリスクを伴う。ローカル LLM 実行は、これらのリスクを根本的に回避し、自社サーバないしエッジデバイスで LLM 推論を完結させる構造を実現する。経済安保時代における情報主権の核心的要件である。

この領域の現在の市場プレイヤーを並べると、NVIDIA(H100、B200、GB200)、Apple(M シリーズ Neural Engine)、Qualcomm(Snapdragon AI Engine)、Cerebras(Wafer-Scale Engine)、Groq(LPU: Language Processing Unit)、Tenstorrent、SambaNova、Etched、Huawei(Ascend)、Alibaba(含光 800)——ほぼ全てが米中企業である。日本国内に該当領域の SoC ベンダーはほぼ不在であり、Preferred Networks の MN-Core が例外的に存在する程度である。

しかし、要素技術としては国内に十分な蓄積がある。並列計算アーキテクチャ(東芝、ルネサス、ソシオネクスト)、低消費電力設計(ソニーセミコンダクタ)、メモリ統合技術(キオクシア)、AI アクセラレータ研究(産総研、理研、Preferred Networks)——これらの要素技術が、統合 SoC として日本国内で焼き上げられていない、ただそれだけの状況である。ドローン特化ベースバンド SoC と全く同じ構造の問題が、ローカル LLM 特化 SoC でも成立している。

蒸留経路の再発見 ── 巨大化競争を超えて

ここで、本補論の核心の一つに触れたい。ローカル LLM 推論 SoC が国内に大量供給される状態(以下「ジャブジャブ」と表現する)は、単に推論の自前運用を可能にするだけではない。それは、独自 LLM 構築のコスト構造そのものを根本から書き換える。

これまでの AI 主権論は、概ね二つの極に分かれてきた。一方は「日本も独自の巨大基盤モデルを作るべき」という独自開発論であり、ABCI や富岳での日本語 LLM 訓練に代表される。他方は「米国製 LLM を使えば良い、独自開発は不要」という受容論である。前者は米中との計算資源・データ規模の差で実現困難、後者はデータ主権と国家戦略の喪失を許容することになる。

しかし、推論半導体がジャブジャブに供給される状態が成立すると、第三の経路が現実化する。それは「蒸留(Distillation)による独自モデル構築」である。

蒸留とは、大規模な「教師モデル」(既存の OSS 基盤モデル、Llama、Mistral、Qwen、DeepSeek 等)から、軽量で用途特化された「生徒モデル」を訓練する技術である。教師モデルの推論結果を大量に生成し、それを学習データとして使う。蒸留の本質的なコスト構造は、教師モデルへの大量推論コストが支配的であり、軽量モデルの訓練コストは相対的に小さい。つまり「推論を大量に回せるか」が蒸留の経済合理性を決める。

推論半導体がジャブジャブにあれば、教師モデルに対する大量推論が低コストで可能となり、蒸留による独自モデル構築のコストが劇的に下がる。具体的には、年間数千億トークン規模の推論を、国産推論 SoC の集積で経済合理的に処理できるようになる。これにより、業界・ドメイン・用途・組織ごとに最適化された独自 LLM を、日本国内で大量に派生・運用することが可能になる。

これは AI 産業論として極めて重要な転換を意味する。OpenAI / Anthropic / Google が「巨大化競争」を続ける中で、日本は「特化と最適化の競争」に転じる、という戦略的方向転換である。基盤モデルをゼロから作る必要はない。OSS モデルを教師として活用し、国産推論 SoC で大量に蒸留する。これにより、米国汎用モデルを「特化と最適化において」凌駕する独自モデル群が、国内産業全体として構築できる。

実は、この戦略の有効性は2024〜2025年に既に実証されている。中国の DeepSeek は、米国の最先端モデルに対してコスト効率で圧倒的な優位を達成した。彼らが採用したのは、まさに「巨大さで勝負せず、効率と最適化で勝つ」戦略である。本補論で提示する日本の戦略経路は、この DeepSeek 的戦略を、推論半導体の国産化と蒸留の経済化で更に進化させたものとして位置付けられる。

APAA 駆動 SoC と LEO コンステレーション量産化

ローカル LLM 推論 SoC と並んで、四位一体戦略の最重要適用先として位置付けるべき領域がもう一つある。Active Phased Array Antenna(APAA:アクティブ・フェーズド・アレイ・アンテナ)駆動 SoCである。これは、LEO(低軌道)衛星コンステレーションの量産化を可能にする鍵となる半導体であり、日本の通信主権と宇宙産業競争力の両面で戦略的死命線である。

APAA 駆動 SoC とは何か

APAA は、多数のアンテナ素子を電子的に位相制御することで、機械的な可動部なしにビーム方向を瞬時に切替可能とするアンテナ技術である。各アンテナ素子に T/R モジュール(送受信モジュール)を配置し、それぞれの位相と振幅を独立制御することで電子的なビームフォーミングを実現する。伝統的に APAA は防衛・宇宙領域の超高コスト技術であり、一基あたり数億〜数十億円のオーダーであった。

しかし2020年代に入り、APAA 駆動 SoC の登場によりコスト構造が劇的に変わりつつある。Anokiwave(米)、SatixFy(イスラエル)、Analog Devices、Renesas 等が、5G mmWave および衛星通信向けの APAA 駆動 IC を商用化している。これにより、従来は防衛・宇宙の専有領域であった APAA が、民生通信機器および小型衛星のレベルで実装可能な技術になりつつある。

LEO コンステレーション量産化との接続

この技術変化が決定的な意味を持つのは、LEO 衛星コンステレーションの領域である。従来の衛星製造は、1機あたり数十〜数百億円、製造期間数年、個別職人芸的な開発、静止軌道(GEO)の少数大型衛星が中心であった。これに対し、SpaceX が確立した Starlink モデルは、1機あたり数千万円〜1億円、製造期間1機あたり数日〜数週間、量産ライン化された製造、LEO の数千〜数万機規模のコンステレーションを実現している。

このコスト構造の変革を可能にした最大要因が、APAA 駆動 SoC の量産化である。Starlink の各衛星は地上局およびユーザ端末との通信に APAA を搭載しており、これが従来は衛星コストの相当部分を占めていた。APAA 駆動 SoC の量産化が、衛星本体のコストを劇的に下げ、コンステレーション規模での量産経済性を成立させた。

すなわち、APAA 駆動 SoC があれば、LEO 衛星をトヨタ車のような量産モデルで製造し、コンステレーションを構成することができる。これは衛星産業の根本的な変革であり、Starlink、OneWeb、Amazon Kuiper、中国 Guowang、欧州 IRIS² といった大規模プロジェクトが既にこの方向で進行している。

日本の戦略的位置と機会

日本の宇宙産業は、長らく「個別大型衛星」のモデルで進んできた。三菱重工、IHI、NEC、三菱電機——いずれも大型衛星の個別開発で世界水準であるが、量産モデルへの転換は遅れている。しかし、LEO コンステレーション市場は今後 10 年で爆発的に拡大すると予測されており、ここで日本が遅れを取ると、通信主権・経済安保・民生市場競争力のすべてで決定的な構造的劣位に陥る。

戦略的重要性を整理すると、APAA 駆動 SoC と LEO コンステレーションは以下の四つの観点で死命線である。

第一に、通信主権の物理レイヤー獲得。LEO コンステレーションは地上の通信インフラに依存しないグローバル通信網である。Starlink への依存は、米国一国への通信主権の譲渡を意味する。日本が独自の LEO コンステレーションを持つことは、地上 5G・ローカル5G を超える、究極の通信主権の確保である。

第二に、経済安保の実装基盤。防衛、災害対応、離島通信、海洋監視、北極圏監視——これらは LEO コンステレーションでしか経済合理的に実現できない領域である。日本独自のコンステレーションは、これらの戦略的能力の基盤となる。

第三に、民生市場での競争力。衛星インターネット、IoT、自動運転車向け衛星通信、農業・物流の遠隔監視——これらの巨大市場は、APAA 駆動の小型ユーザ端末で初めて経済合理的になる。日本企業がこの市場で参入するには、APAA 駆動 SoC が必須である。

第四に、量産インフラの戦略的価値。LEO 衛星を「トヨタ車のように」量産できる能力は、平時には民生市場、有事には防衛・経済安保用途への即応的転換を可能にする。半導体国産化と同様、平時に整備しておかなければ危機時に間に合わない種類のインフラである。

日本の蓄積資産との接続

ここで重要なのは、日本がこの領域に必要な要素技術と産業基盤を、すでに持っているという事実である。

APAA 設計力としては、三菱電機が伝統的に世界水準の能力を持つ。同社は防衛省 ATLA や JAXA の衛星通信プロジェクトで、APAA を継続的に開発してきた。NEC、富士通、東芝も、フェーズドアレイ技術と通信 SoC の双方で蓄積を持つ。

量産技術としては、日本は世界最高峰の自動車量産技術(トヨタ生産方式、カイゼン、JIT)を持つ。LEO 衛星の量産化は、この自動車製造の知見を衛星に転用する戦略であり、SpaceX のアプローチを日本の産業構造の上で再構築するものである。三菱重工、川崎重工、IHI——これらの大型製造業者は、量産ライン化への転換能力を持つ。

そして、本章で論じてきた半導体国産化戦略がここに直結する。APAA 駆動 SoC は、ドローン特化ベースバンド SoC やローカル LLM 推論 SoC と同様、四位一体戦略の対象領域として完璧に整合する。三菱電機の APAA 設計力 + 日本の自動車量産方式 + 国内ファウンドリ(JASM、Rapidus、ミニマルファブ)+ 生成 AI による SoC 設計 + 投機的製造による並列探索——これらの組み合わせにより、APAA 駆動 SoC の国産化と、それを基盤とする LEO 衛星量産能力の確立が可能となる。

ドローン用ベースバンド SoC との戦略的相乗効果

この領域への展開は、本章の主論であるドローン特化ベースバンド SoC との戦略的相乗効果を持つ。LEO コンステレーションは、ドローンのマルチリンク通信における究極のバックボーンとなる(第6章のマルチリンク戦略参照)。すなわち、ドローン用ベースバンド SoC と APAA 駆動 SoC の両方を国産化することで、地上から低軌道まで貫く、完全に国産化された通信主権インフラが構築される。これは経済安保時代の日本が獲得すべき、最も野心的かつ実装可能な技術主権の姿である。

そして、APAA 駆動 SoC は、ローカル LLM 推論 SoC と並んで、「特化と最適化」の競争領域である。汎用性で勝負しない、衛星通信および 5G mmWave 用途に特化する、低消費電力と高指向性ビームフォーミングを最適化する——これらは日本企業の伝統的強みが活きる設計戦略である。

リードタイムの絶対性は、ここでも適用される。LEO コンステレーション市場の競争は、2020年代後半に決定的局面を迎える。今、平時のうちに APAA 駆動 SoC の国産化に着手しなければ、Starlink、OneWeb、中国 Guowang による寡占構造が固定化し、日本が参入する余地は失われる。これは半導体問題と同じ、リードタイム計算が要求する必然である。

経済安保半導体戦略から AI 主権・通信主権実装戦略へ

そして、四位一体戦略はこれら全てに適用可能である。並列計算・メモリ統合・低消費電力設計の国内蓄積を IP として動員し、生成 AI が SoC アーキテクチャを高速設計し、ミニマルファブで試作サイクルを圧縮し、投機的製造で複数アーキテクチャを並列探索する——これにより、ローカル LLM 推論 SoC の国産化も、APAA 駆動 SoC の国産化も、本章で論じたドローン特化 SoC と同様のリードタイムで実現可能性が見えてくる。動くシリコンまで 1.5〜2.5 年、商用品質達成まで 3.5〜5 年。この時間軸で、日本の AI 主権と通信主権の実装基盤が同時並行的に整う可能性がある。

つまり、本章で提示してきた四位一体戦略は、ドローン産業の文脈で具体的に論じてきたが、その射程は経済安保半導体戦略全般、さらには AI 主権と通信主権の実装方法論にまで及ぶ。各領域に固有の要素技術(通信工学、並列計算、暗号、センシング、量子制御、APAA フェーズドアレイ等)を、共通の戦略要素(生成 AI、ミニマルファブ、投機的製造)と組み合わせることで、複数の領域で同時並行的に国産化を進めることができる。

そして、これらの領域は単独ではなく、相互補完的な戦略チェインを構成する。ドローン特化ベースバンド SoC が地上のドローン運用基盤を確保し、ローカル LLM 推論 SoC が AI 主権の実装基盤を確保し、APAA 駆動 SoC が LEO コンステレーション量産化を通じて宇宙の通信主権を確保する。これら三つを四位一体戦略で同時並行的に獲得することは、経済安保時代の日本が技術主権を保つための、統合された総合戦略として位置付けられる。

これは政策的に極めて重要な含意を持つ。経済安全保障推進法における特定重要技術指定、重要技術育成プログラム(K Program)の予算配分、防衛省 ATLA の研究開発契約、TSMC 熊本工場・Rapidus・ミニマルファブの三層活用——これら政策手段を、ドローン用 SoC 単独ではなく、ローカル LLM 推論 SoC・APAA 駆動 SoC を含む複数の戦略的死命線 SoC の同時並行的国産化として運用すべきである。共通の設計インフラ(生成 AI ツールチェーン、ミニマルファブ施設、投機的製造の経済支援枠組み)を整備することで、領域横断的な効率性が生まれる。

そして、リードタイムの絶対性は、ドローン用 SoC だけでなく、これら全ての半導体領域に適用される。半導体は危機を待てない。AI 主権の実装基盤も、通信主権の物理レイヤーも、危機顕在化を待っては構造的に間に合わない。今、平時のうちに、戦略的死命線として認識された複数の半導体領域に、四位一体戦略を体系的に適用する産業政策が必要である。

本章の主題はドローン特化ベースバンド SoC の国産化であったが、その背後にある戦略構造は、経済安保半導体戦略の一般理論として、さらには AI 主権・通信主権の統合実装方法論として、より広範な適用可能性を持つ。読者がこの論考を、ドローン産業の文脈に限定せず、各々の専門領域に適用していただければ、本論考の射程は更に拡張される。

ドローンと AI と LEO 衛星、半導体と主権、技術と意思——これらは別々の問題ではなく、経済安全保障時代における日本の戦略的選択という、一つの統合された問いとして立ち現れている。本論考はその問いに対して、技術的に実装可能な答えの一つを提示するものである。

本記事の背景と目的

筆者が所属するクイックイタレート株式会社では、15年以上にわたる衛星・無線通信・ネットワークエンジニアとしての知見を活かし、次世代の「技術自立(テクノロジー・ソブリンティ)」を支えるドローンアーキテクチャの研究開発に着手しています。地政学的リスクが顕在化し、海外製コンポーネントの供給網が遮断される事態を想定したとき、我々日本は自らの手で次世代の鍵となる「ドローン」の制御システムを構築できるのか。本シリーズでは、マルチリンク衛星通信、そして経済安全保障を担保する純国産(または同盟国産)ハードウェアの必要性について、実戦的な技術要件を解説し、共に研究する仲間を募ります。次回以降はもっともっと泥臭いところでの実装になると思いますが、是非ご連絡ください!!