PC-8001は6000Hから7FFFHまでが増設用のROM領域になっていて、ここにSRAMを増設してみます。

まずGALにアドレスのデコードとメモリのRD/WRを追加します。

title CH376S IO UNIT

pattern CHIO

revision A

author yamori813

date 07/13/21

chip chio gal6001

; The following pin list order mustly be followed strictly:

; 1. device pins 1 to 24

; 2. slmc 7 to slmc 0

; 3. buried feedback (OLMC 14) to buried feedback (OLMC 23)

; pins 1 2 3 4 5 6 7 8 9 10 11 12

i1 i2 i3 i4 i5 i6 i7 i8 i9 i10 i11 gnd

; pins 13 14 15 16 17 18 19 20 21 22 23 24

oclk o14 o15 o16 o17 o18 o19 o20 i21 i22 i23 vcc

; slmc7 slmc6 slmc5 slmc4 slmc3 slmc2 slmc1 slmc0

nc nc nc nc nc nc nc nc

; buried feedback to AND array from OLMCs.

; bur14 bur15 bur16 bur17 bur18 bur19 bur20 bur21 bur22 bur23

nc nc nc nc nc nc nc nc nc nc

; specify the User Electronic Signature (UES)

@ues chio

; 8 ues bits are used per character.

equations

; ILMC : asynchronous inputs.

; IOLMC : asynchronous feedback to AND array.

; SLMC : not used.

; OLMC 14-18 : asynchronous outputs (output always enabled).

; OLMC 19-23 : D-type registered outputs (output always enabled).

; buried feedback of OLMCs not used.

; asynch reset : not used (default is registers cannot be reset).

; RESET

;o14 = /i1

; RD = RD | IORQ

o14 = i2 | i3

; WR = IORQ | WR

o15 = i3 | i4

; CE ADDRESS A1-A7 FC(252),FD(253) 11111100 11111101

/o16 = /i5 & i6 & i7 & i8 & i9 & i10 & i11

; RD = RD | MREQ

o17 = i2 | i1

; WR = MREQ | WR

o18 = i1 | i4

; a13 a14 a15 6000H 0110 0000

o19 = i21 & i22 & /i23

; end of example 5

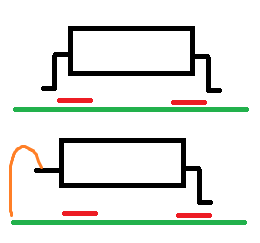

何かの基板から剥がしたSOP28のHY6264を変換基板で使おうと思ったのですが、変換基板のパターンより足が大きくハンダ付けできません。

いろいろ試して、片側はパターンでハンダ付けして、片側はワイヤーを張ることにしました。(後日追記:いろいろいじってたら、片側のパターンがはがれ、結局両方ワイヤー張ることになりました)

電源を入れる前には必ずVCCとGNDがショートしていない事を確認します。

DataバスがショートしているとPCが起動しません。起動するようになってもちゃんと接続されてないかもしれません。とりあえず最初はmonで増設領域に書き込みをして読み込んで正常か確認します。

後日追記:秋月の変換基板のAE-SOP28-DIP-Aはパターンが広くハンダ付けしやすいです。

手動での確認では全領域のテストはできないので、テストプログラムを書いて確認しました。ロジックは「マイコンのためのBASICの使い方」のRAMテスター(P125)を参考にしています。

MEMSTART EQU 6000H

MEMEND EQU 8000H

PUT MACRO C

LD A, C

RST 18H

ENDM

TEST_00:

LD HL,MEMSTART

LOOP1

LD (HL), 0

INC HL

LD A, MEMEND SHR 8

CP H

JP NZ, LOOP1

PUT '0'

PUT '0'

LD HL,MEMSTART

LOOP2:

LD A,(HL)

AND A

JP NZ, ERR

INC HL

LD A, MEMEND SHR 8

CP H

JP NZ, LOOP2

PUT ':'

PUT 'O'

PUT 'K'

TEST_BW:

PUT '-'

PUT 'B'

PUT 'W'

LD HL,MEMSTART

LOOP4:

LD D, 1

LOOP3:

LD (HL), D

LD A, (HL)

CP D

JP NZ, ERR

RLC D

JP NC, LOOP3

INC HL

LD A, MEMEND SHR 8

CP H

JP NZ, LOOP4

PUT ':'

PUT 'O'

PUT 'K'

TEST_FF:

LD HL,MEMSTART

LOOP5

LD (HL), 0FFH

INC HL

LD A, MEMEND SHR 8

CP H

JP NZ, LOOP5

PUT '-'

PUT 'F'

PUT 'F'

LD HL,MEMSTART

LOOP6:

LD A,(HL)

CP 0FFH

JP NZ, ERR

INC HL

LD A, MEMEND SHR 8

CP H

JP NZ, LOOP6

PUT ':'

PUT 'O'

PUT 'K'

END:

JP 05C66H

ERR:

PUT ':'

PUT 'E'

PUT 'R'

PUT 'R'

JP 05C66H

本体にROMを増設している場合はROMDS3#で無効にできるようです。これはPC-8011などで64Kフルメモリや外部のROMのサポートのためにあったと思われます。

CP/Mを利用するためには64Kフルメモリが必要で、ブート時にROMDS0-3ですべてのROMを無効にしてRAMを有効にして、フロッピーのIPL部分をメモリに貼り付ける必要がありました。

結構苦労しました。

ちなみにPC-8001のメモリはDRAMですが、これはSRAMに比べて部品が小さかったことと価格が安かったためです。PC-8001の16K増設メモリは9800円でしたが、1979/12号のRAMの秋月の広告ではSRAMのHM472114P-4が1000円で4ビットなので1Kバイト2000円で、16Kバイトだと32000円になりました。

90年代のデジタル系家電の基板にはSRAMが乗っていることがよくあります。SOPだったりしますが、ヒートガンを使うと簡単に剥がせるので、捨てる前に剥がして再利用がお勧めです。

N-BASIC 1.0のバグ

6000HにAB"があるとその後の処理を実行するはずなのですが、何故か動きません。

monのディスパッチのほうは動きます。

MON

*S7FFC

7FFC 00-C9 00-00 00-00 00-55

8000 E6-

*^B

MON

Ok

仕方が無いので0000H-2000Hをモニターでセーブして、DumpListEditorで逆アセンブルしてみます。

ROMのチェックルーチンは183EHからあり以下のようなコードです。

1:

2: - 0000' START:

3: 0+10 0000' 210060 LD HL, 6000H

4: 10+7 0003' 7E LD A, (HL)

5: 17+7 0004' FE41 CP 'A'

6: 24+6 0006' 23 INC HL

7: 30+10 0007' C21000 JP NZ, END

8: 40+7 000A' 7E LD A, (HL) ; N-BASIC 1.0 BUG

9: 47+7 000B' FE42 CP 'B'

10: 54+10+7 000D' CC0260 CALL Z, 6002H

11: - 0010' END:

12:

二つ目のLD A,(HL)がありません。これでは6000Hに"AB"があっても絶対に呼ばれません。

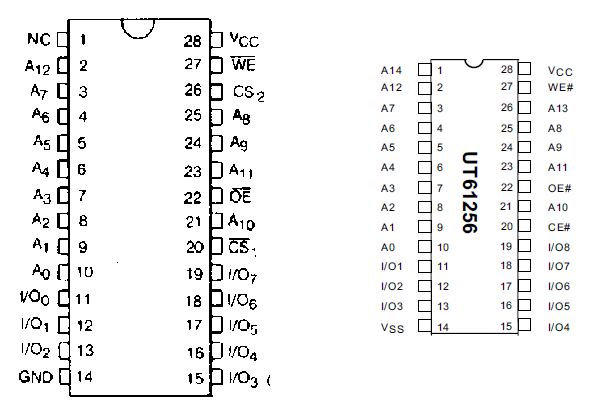

32K対応

フルRAMにするため32Kにする方法を考えて見ます。

8Kも32Kも28Pinなのでそのままでいけます。

1,26ピンがアドレスに変わっているので、接続します。

8K増設のときにCS1(20)はGNDにしてCS2(26)をつかっていたのでGALのデザインを変える必要があります。

/o19 = i21 & i22 & /i23

ROMDS0-3の制御も考える必要があります。内蔵でROMは増設してないのでROMDS0-2を一括で処理しても良いかもしれません。

PC-8011などではIOポートでROMDSの制御ができたようです。

6000からの8Kは常時読み書き可能、0000からの24Kはスイッチで、ROMDS0-2をHiの時は読み込み不可で、書きこみ可にします。そうすると同じアドレスの読み書きをするとRAMにROMがコピーされます。フルRAM化するときは、ROMDS0-2をLoにしてRAMをすべて読み書き可能にします。

ROMDS0-2を物理スイッチ(ジャンパー)にして、その出力をGALでももらって、上のデコードを実現するのがよさそうです。

バッテリーバックアップも付けたいです。あと空いているところになにか載せたいな。

と思って調べていたら8Kの32Kでは仕様がちょっと違うことに気がつきました。