PC watchで連載されている「後藤弘茂の海外ウイークリーニュース」は、CPU、メモリ周りの業界動向をチェックする上で非常に面白い。Intel、AMD、Apple、Sumsungといった半導体ベンダの製品発表・ロードマップについて、深く考察されている良記事が多い。

ちょっと思い立って2014年の記事を眺め直してみた。

ムーアの法則が減速していると言われて久しいが、CPUもメモリもまだまだ進化を続けていることが伺える。

以下、CPUとメモリについて一つずつ気になった記事についてまとめた。

ウェアラブル・デバイス向けのCPU

記事URL

http://pc.watch.impress.co.jp/docs/column/kaigai/20141022_672381.html

(ARM. http://www.arm.com/files/event/B2_Building_Ultra-Low_Power_Wearable_SoCs__Using_High_Efficiency_Processors.pdf よりスライドを抜粋.)

昨年、Apple Watchの発表で一気に注目度が上がった、ウェアラブル・デバイス。

ウェアラブル・デバイスが流行るかかどうかは、バッテリーの持ちがどれくらい長くなるか、といった話は良く聞かれるが、ARMがこの問題に対してどう取り組んでいるか、という話だ。

面白いのと思ったのは、実は現状のARMのCPU製品の中に、ウェアラブル・デバイスで想定されている消費電力のレンジと機能を実現するのに最適化されたCPUは、今のところ存在していない、という指摘だ。言い換えると、半導体設計、CPUアーキテクチャ設計の観点から言えば、ウェアラブル・デバイス向けのSoCの電力効率はまだまだ改善の余地が大きい、と見ることもできるわけだ。

例えば、2007年に発売されたiPhoneの性能は(ベンチマークにもよるが)7年間で数十倍に伸びた。ちなみに、同じ時期にデスクトップPCの性能はほとんど伸びていない。

当時は、デスクトップPC向けに最適化されたCPUが主流であり、その設計は電力を(発熱が許す限り)いくらでも使えることを前提に最適化されていた。このため、バッテリー駆動のスマートフォン上で動作することを想定し最適化されたCPUは存在していなかった。しかしスマートフォンの普及に伴い、電力制約の厳しいモバイル端末向けのCPU設計の最適化に多額の研究開発費をかけることが可能になると一気にスマートフォンの性能は向上していったわけだ。

この状況は、見方によっては、現在のウェアラブル・デバイス向けのCPUを取り巻く状況に似ていなくもないと思う。

スマートウォッチが一定数売れ、ウェアラブル・デバイス向けのSoCの開発に多額の研究開発費用がかけられるようになるとすれば、ウェアラブル・デバイスのバッテリー寿命や機能に関しても大きなブレークスルーが起きうるのかもしれない。

High Bandwidth Memory (HBM)

記事URL

秒読み段階に入った広帯域メモリ「HBM」

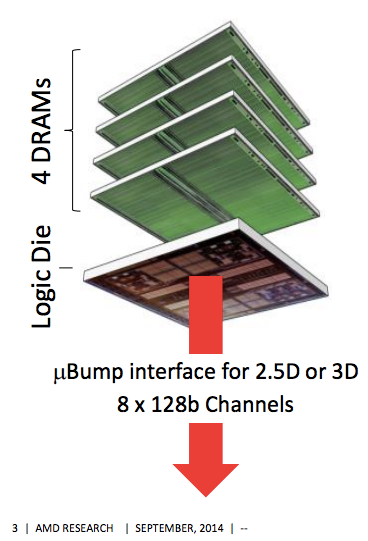

(AMD Research, https://hpcuserforum.com/presentations/seattle2014/IDC_AMD_EmergingTech_Panel.pdf より図を抜粋.)

ざっくり言うと、CPU <-> メモリ間の帯域性能が大幅が向上にしますよ。という話。

例えば、数年前にスパコン性能で世界一になった神戸の京コンピュータの1CPUあたりのメモリ帯域は64GB/secだが、これが次世代のHBMでは最大で1TB/secまで高性能化する。スペック的には、10倍以上の性能向上である。

HBMを実現する技術の原理は直感的に分かりやすく、半導体チップに対して垂直方向に電気信号を送るビアを突き刺し、これを使ったデータへの並列アクセスを実現する(AMD Researchの図が分かりやすかったので載せています)。つまり、チップの辺からだけでなく面全体で、データ転送が可能になるので、メモリ帯域性能が大幅に向上するわけだ。これはThrough Silicon Via(TSV)と呼ばれる技術で、2000年代後半から世界的な研究開発競争が繰り広げられてきたもので、ついに実用・普及段階に入る、ということもあり注目度は非常に高い。

まずは、HPCアプリケーション(気象シミュレーションやFFTなどのメモリ帯域で性能が決まるアプリケーション)がターゲットとなり、コストが下がればGPU向けのメモリとしてもコンシューマー向けに展開されると思うが、これがどの程度商業的に成功するかは2015年〜16年のホットトピックだろう。