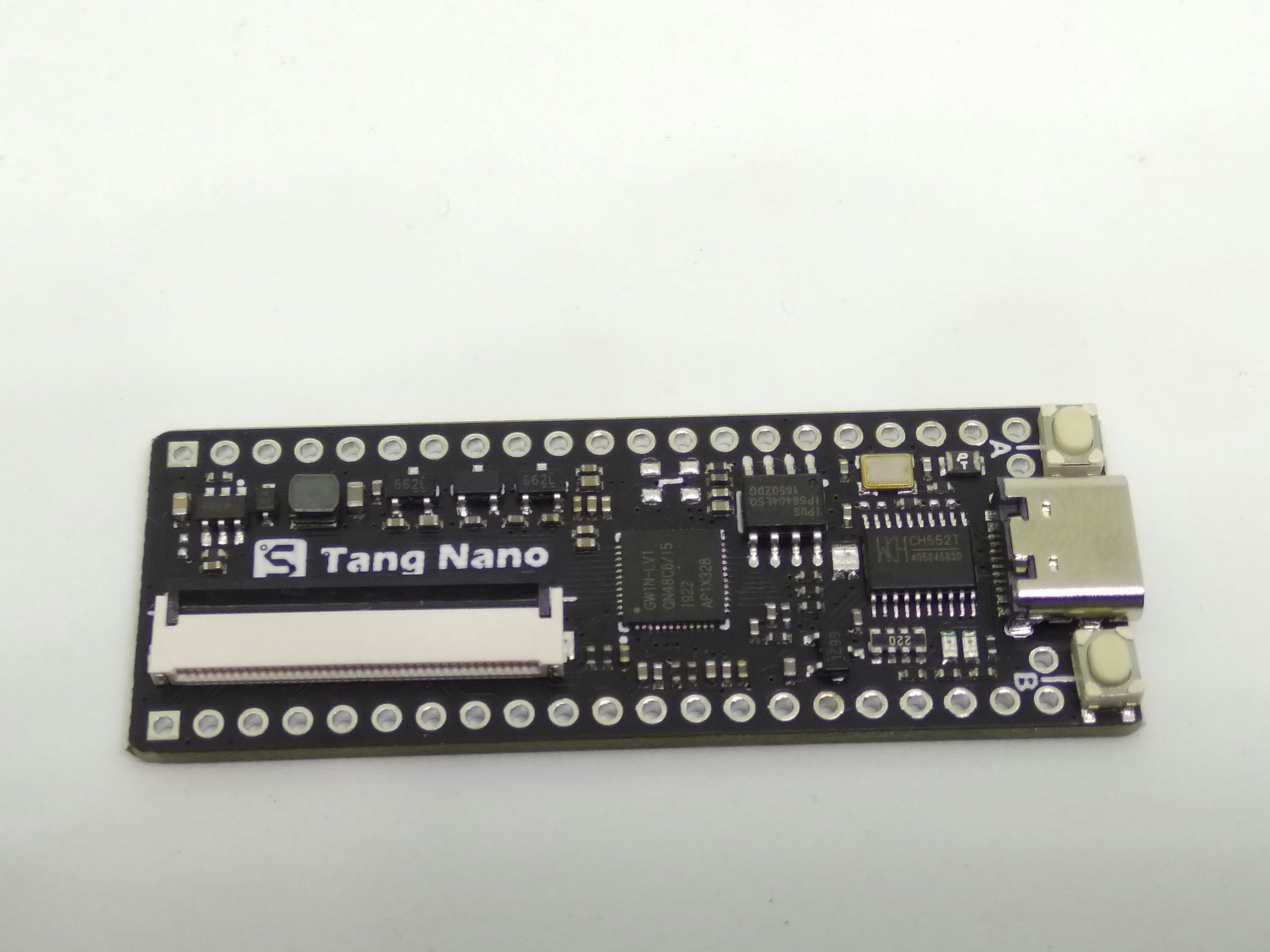

秋葉原のSigezone で 深圳矽速科技有限公司(https://www.sipeed.com/ , 以降SiPeed) 製のFPGAボード**「Tang Nano」**を入手できましたので、早速動かしてみました。税込800円という超ロープライスなFPGAボードです。

【追記】

Linux版は @ciniml さんがプロジェクトの作り方とかも詳しく書かれているのでこちらを参考にしてください。

Tang Nanoとは

Tang Nanoは中国 广东高云半导体科技股份有限公司 (http://www.gowinsemi.com.cn/ , 以降GOWIN) のFPGAであるGW1N-1を搭載したボードです。

中国ではSeeedが取り扱っています。

https://www.seeedstudio.com/Sipeed-Tang-Nano-FPGA-board-powered-by-GW1N-1-FPGA-p-4304.html

ドキュメントの入手先

ボードの開発元のSiPeedとチップの開発元のGowinよりドキュメントが公開されています。

SiPeed Tang Nano Document

Gowin 云源软件用户指南

この手順に従い、Windowsでの開発環境構築と動作確認のための「Lチカ」をやってみました。

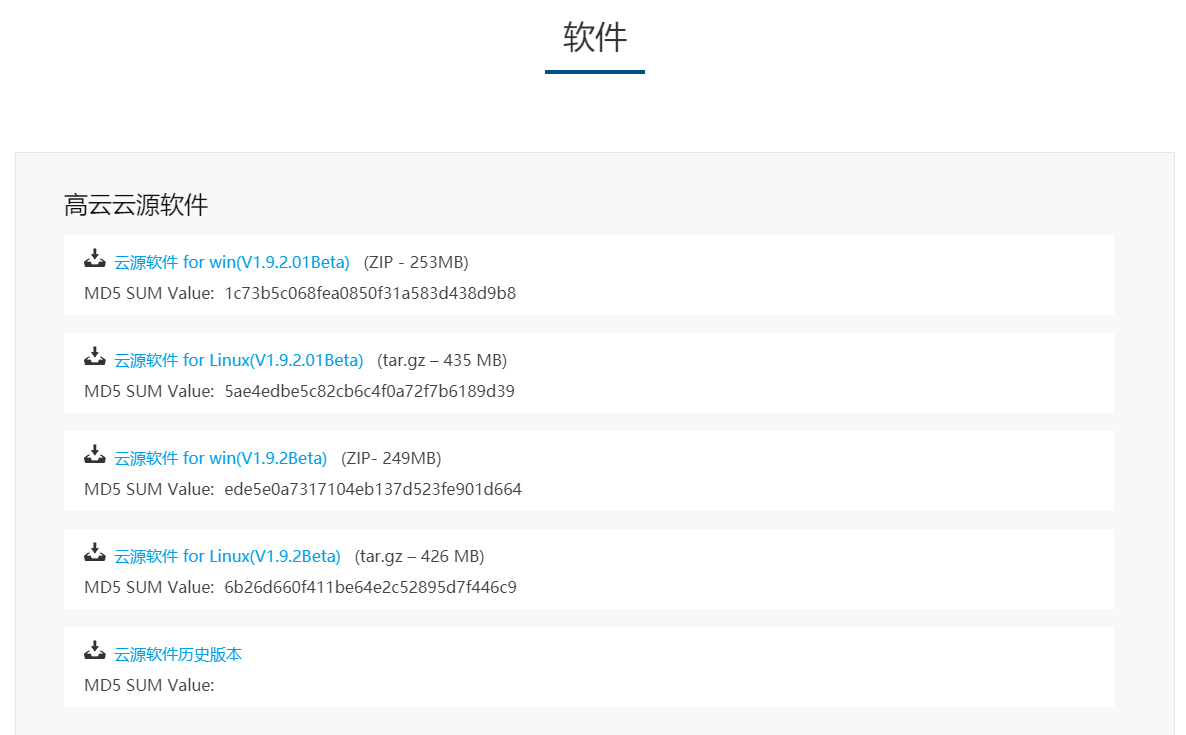

IDEの設定

まずは以下よりIDEを入手します。今回は確認時点(2019/11/13)での最新版(V1.9.2.01Beta)を使用しました。

高云云源软件

2020.4.21追記

現時点の最新版の1.9.5.01ベータでは書き込みで失敗するという報告がありました。

その場合は以下から旧バージョンを入手して使ってください。

云源历史文件

IDEのインストール

ダウンロードしたZIPファイルを解凍して出来た実行ファイルをダブルクリックしてインストールします。

画面の手順に従って進めればOKです。途中でダウンロードケーブルのドライバのインストールの確認を要求されますので、チェックを入れます。

USBチップは南京沁恒微电子股份有限公司(http://wch.cn/) のUSBマイコンCH552を使用したFTDI互換です。手順に従っていくとFTDIのドライバがインストールされます。

ここは正直ライセンス的にアレなので気になる人は他のOS版を使ってください

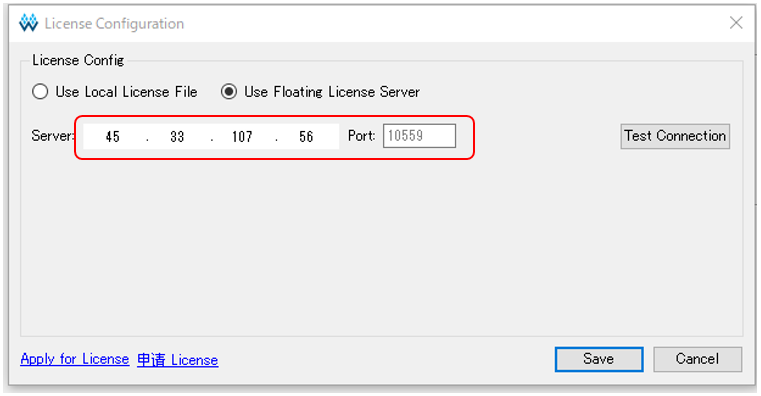

ライセンス設定

IDEを起動するにはSynopsysのライセンスが必要です。ライセンス設定は以下の2つの方法が提供されています。

- Stand-Alone版ライセンス

- SiPeedのサーバーを使ったNetwork activation

1.は「Networkカードのmacアドレスを変えてライセンスファイルを導入する」という色々とアレな方法なので、今回は2.の方法で対応しました。

インストールしたIDEを最初に起動すると"License Configuration"画面が表示されますので、

- server address 45.33.107.56

- port: 10559

を入力します。なお、SiPeedのドキュメントでは本文と図で異なるサーバアドレスが記載されているので、必ず本文に記載されているアドレスを入力してください。

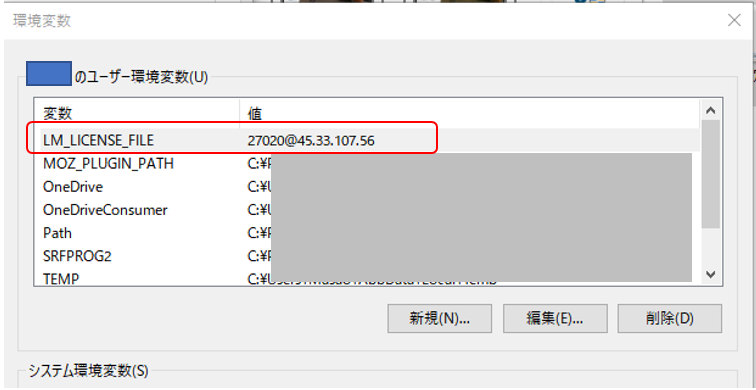

次にWindowsの環境変数にライセンスサーバーのアドレスを追加します。

Windowsのコマンドプロンプトで、以下のコマンドを実行します。

setx LM_LICENSE_FILE 27020@45.33.107.56

念のためにWindowsの環境変数に追加されているか確認しておきます。

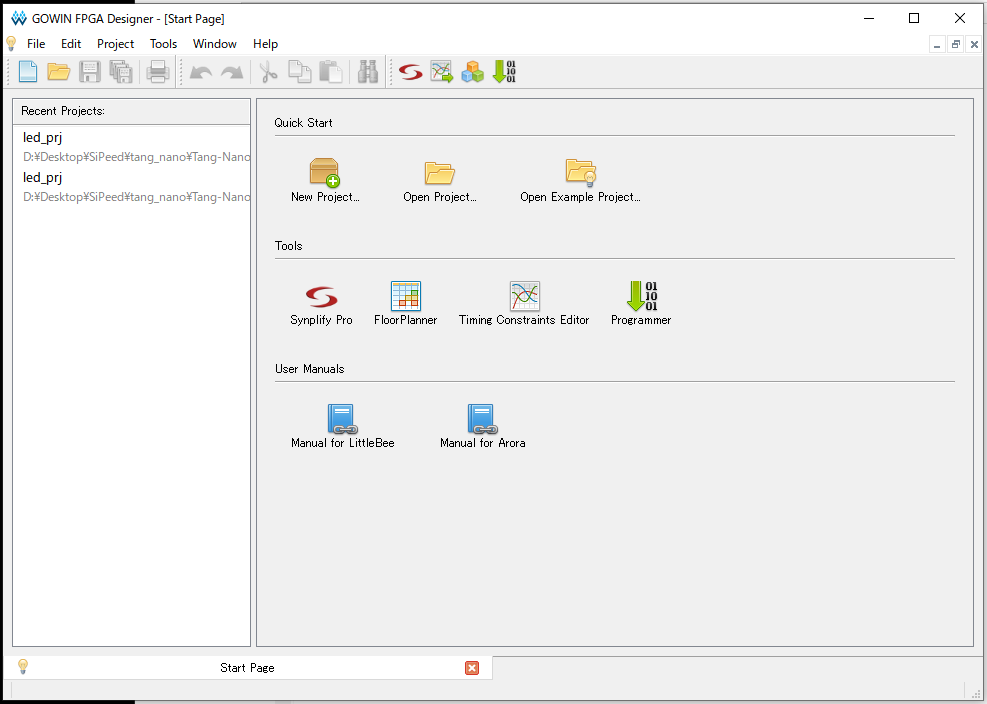

IDEの起動

ライセンス設定をしたら、念のためにPCを再起動します。

インストールした「GOWIN FPGA Designer」を必ず管理者モードで起動します。

管理者モードで起動しないと、イメージファイルの書込みができないので注意してください。

【追記】

管理者モードでも書込みがうまく出来なかったという話も聞きましたので、その場合はLinux環境で試してみて下さい。

ライセンス認証が完了すると以下のStart Pageが表示されます。論理合成ツールはSynopsys の「Synplify Pro]です。

サンプルプロジェクトの実行

サンプルプロジェクトはSiPeedのGitHubより入手できます。

Tang-Nano-examples

環境の動作確認として「led_prj」を実行してみます。

プロジェクトの読み込み

[File]->[Open]より \example_led\led_prj にある "led_prj.gprj" を開きます。

正常に読み込めると以下のDesign Summaryが表示されます。

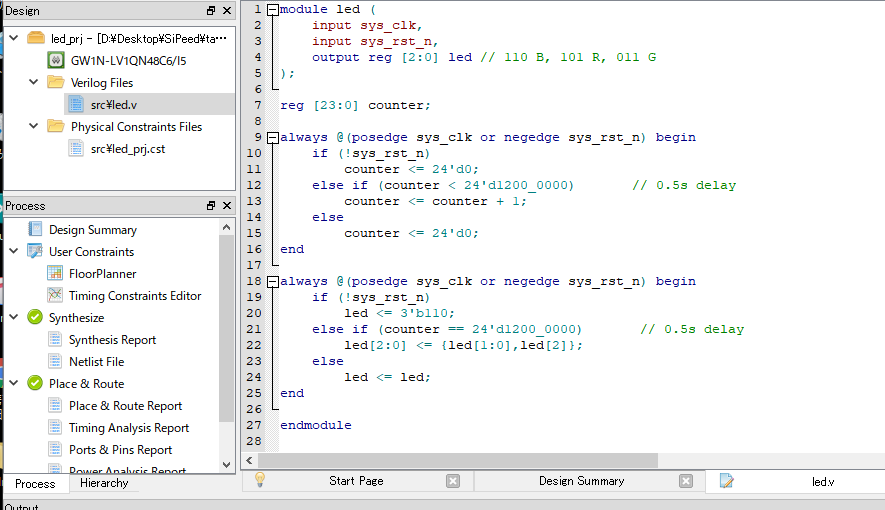

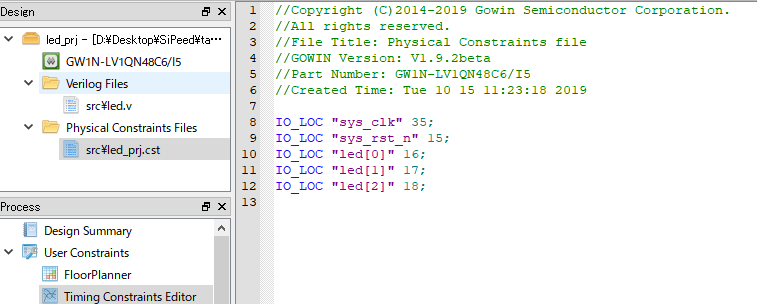

サンプルプロジェクトには "デザイン(Verilog)ファイル" と "制約(Constraint)ファイル"が含まれています。

左ペインのファイルをダブルクリックするとファイルの内容が表示されます。

"制約(Constraint)ファイル"にはピン配置が記述されています。

タイミング制約等FPGA設計そのものについてはここでは触れません

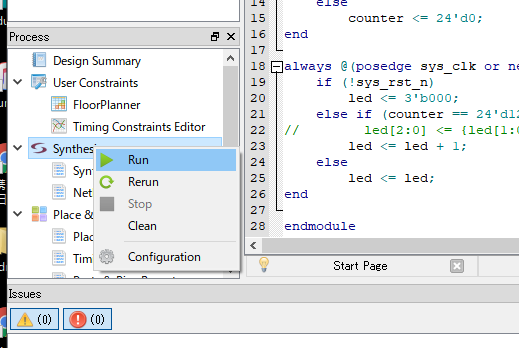

論理合成

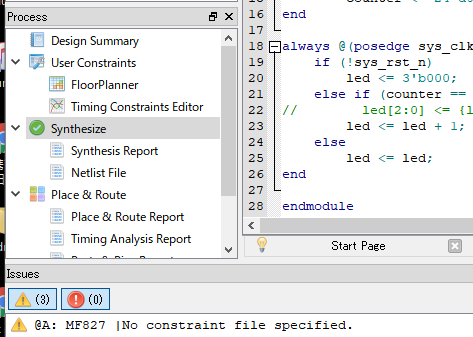

左下のペインのSynthesizeを右クリック->Runを選んで論理合成を実行します。

正常に終了するとアイコンが緑のチェックマークになります。エラーがある場合は下ペインの"Issues"に表示されます。

配置配線

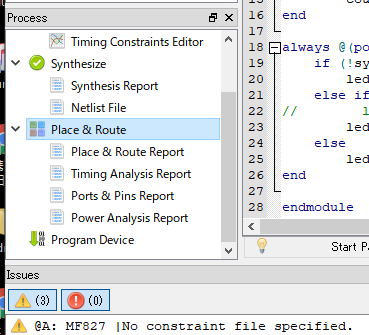

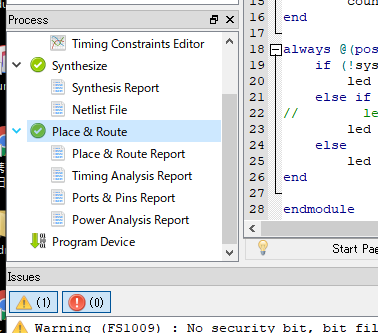

論理合成が終わったら左下のペインのPlace & Routeを右クリック->Runを選んで配置配線を実行します。

論理合成と同様、正常に終了するとアイコンが緑のチェックマークになります。エラーがある場合は下ペインの"Issues"に表示されます。

デザインの書き込み

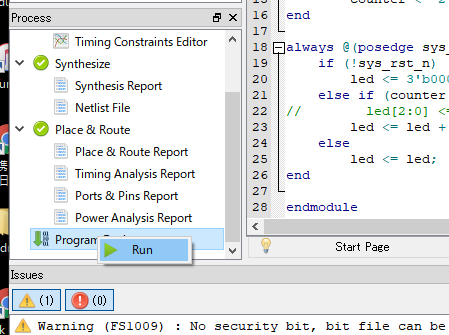

配置配線が終わったら作成したデザインをFPGAへ書き込みます。左下のペインのProgram Deviceを右クリック->Runを選んで"Programmer"を立ち上げます。

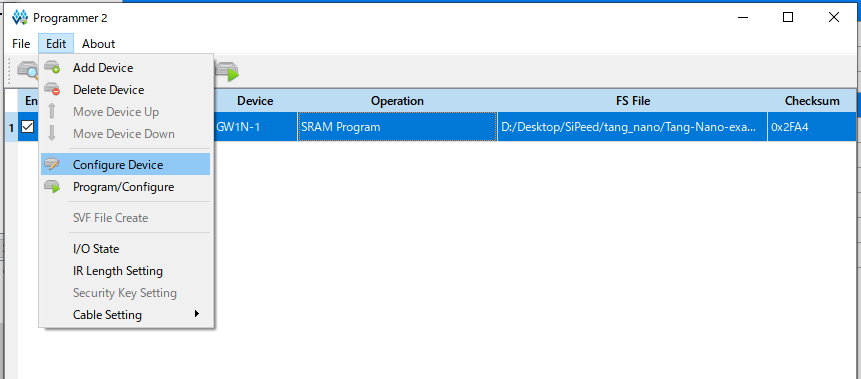

デフォルトの書き込み先はSRAMになっていますので、デバイスを選択して[Edit]->[Configure Device]でデバイス設定を開きます。

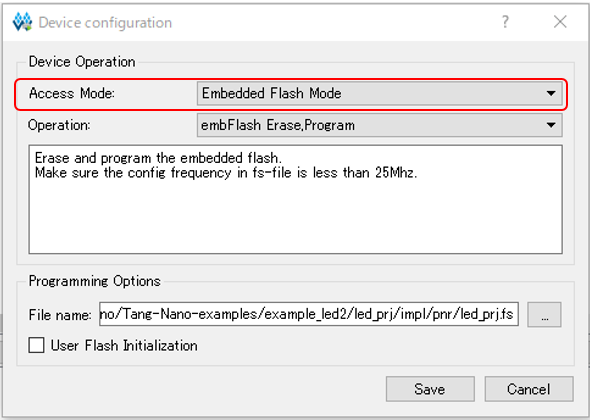

Access Modeで"Embedded Flash Mode"を選択して書き込み先を内蔵のフラッシュメモリに変更します。(SRAMのままでも、電源を切ったら消えますが、回路の書き込みと動作はできるようです。)

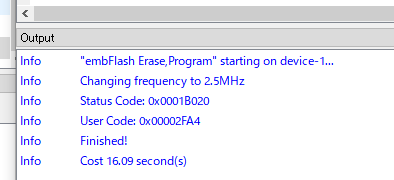

※v1.9.2/1.9.3だと、書き込み機のクロック周波数の設定がデフォルトで未設定のため書き込みが正常に終わっても動作しない、という減少があるようです。Edit→Cable→CableSettingから書き込み機のクロック周波数を「2.5MHz」に設定してから書き込みをすると動作します。

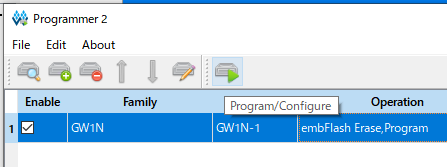

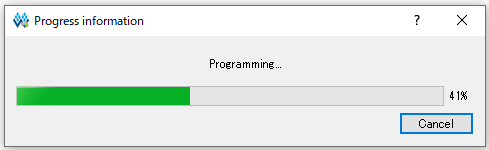

Saveボタンで保存してProgram/Configureボタンを押すと"フラッシュの消去"->"書き込み"が開始されます。

正常に終了すると下ペインのOutputに"Finished!"と表示されます。

動作確認

書込みが終わるとデバイスが自動で再起動しLチカが実行されます。以下はわかりやすいようにLチカのパターンをちょっと変えてみました。

@ciniml さんと投稿をみて、こちらでもLチカパターンを変えてみた。 pic.twitter.com/QMGJxvsqGg

— tomorrow56@11/9-10 MF深圳行くよ(今年こそ) (@tomorrow56) November 3, 2019

最後に

とりあえず開発環境は出来たので、このサイズのFPGAで何ができるのか色々と触ってみるつもりです。

LCDのサンプルもあったので、次は専用のパネルを入手して遊んでみたいです。