概要

GOWINのLittleBeeシリーズFPGAが載っているFPGAボードTang NanoがSipeedから出たので、Linux上に開発環境を整えてからLチカするまで試した内容を記載します。

Windows版は @tomorrow56 さんが既に書いている のでこちらを参考にしてください。

開発環境のインストール

基本的にインストール手順はSipeedのTang NanoのGet Startedページに書いてありますが、現時点でLinux版はTODOとあります。とりあえずLinux版の開発環境バイナリがDLできるので、適当に入れてみました。

Tang Nanoの資料はhttp://dl.sipeed.com/TANG/Nano からDLできます。

-

http://dl.sipeed.com/TANG/Nano/IDE にある

download_link.txtに記載されているとおり、 http://www.gowinsemi.com.cn/faq.aspx

のページを開く -

云源软件 for Linux(V1.9.2.01Beta)を選んでLinux版のIDEをダウンロードする。 -

ダウンロードしたtar.gz形式のアーカイブを展開する。このとき、アーカイブにはトップディレクトリが含まれていないので、適宜ディレクトリを作ってその中に展開すること。

mkdir gowin tar xf Gowin_V1.9.2.01Beta_linux.tar.gz -C gowin -

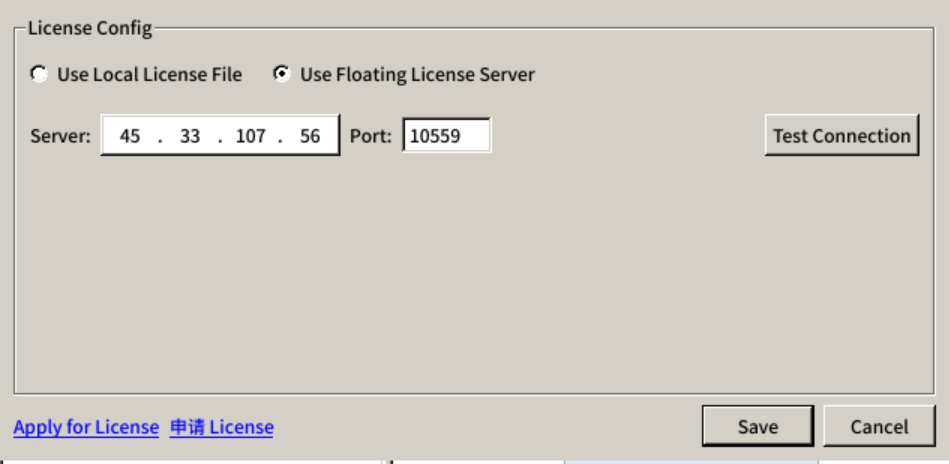

ライセンスサーバーの設定のため、以下の環境変数を設定する。他のflexlm系ライセンスを使っている場合は、既存の

LM_LICENSE_FILEに:で区切って追加する。再起動時に自動的に設定されるように.bashrcあたりに追加しておくとよいexport LM_LICENSE_FILE=27020@45.33.107.56 -

IDE/bin/gw_ideを実行する。ライセンスエラーとか言われるので、Use Floating License Serverを選んで、Serverに45.33.107.56,Portに10559を入力してSaveを押し、再度gw_ideを実行する。 -

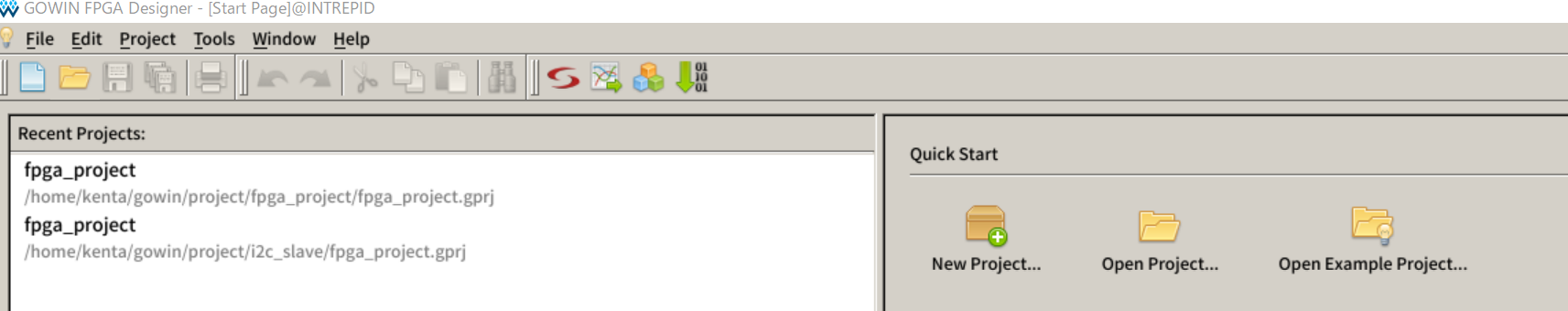

GOWIN FPGA Designerの画面が表示されたら成功

これでLinuxでの開発環境のインストールは終わりです。

Lチカする

買ってきてUSBポートに繋ぐとボード上のカラーLEDが点灯します。

動作確認用に点灯パターンを変更してみます。

プロジェクト作成

サンプル・プロジェクトが用意されていますが、適当に回路図読みながらプロジェクトを作ってみます。

回路図は http://dl.sipeed.com/TANG/Nano/HDK の下にあります。

GOWIN FPGA Designer のトップ画面のQuick StartからNew Project を選びます。

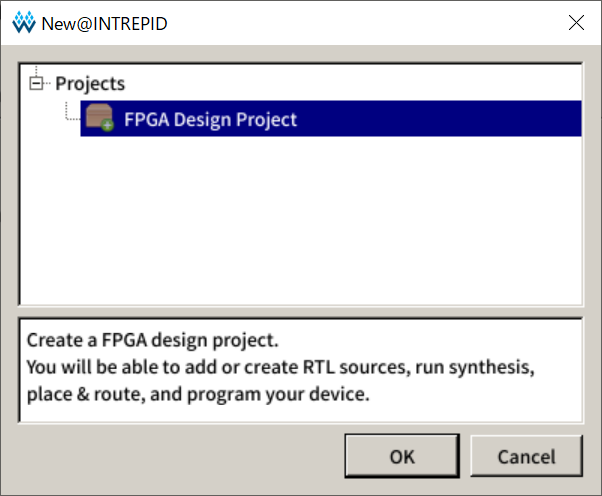

表示されたダイアログでFPGA Design Projectを選んでOKを押します。

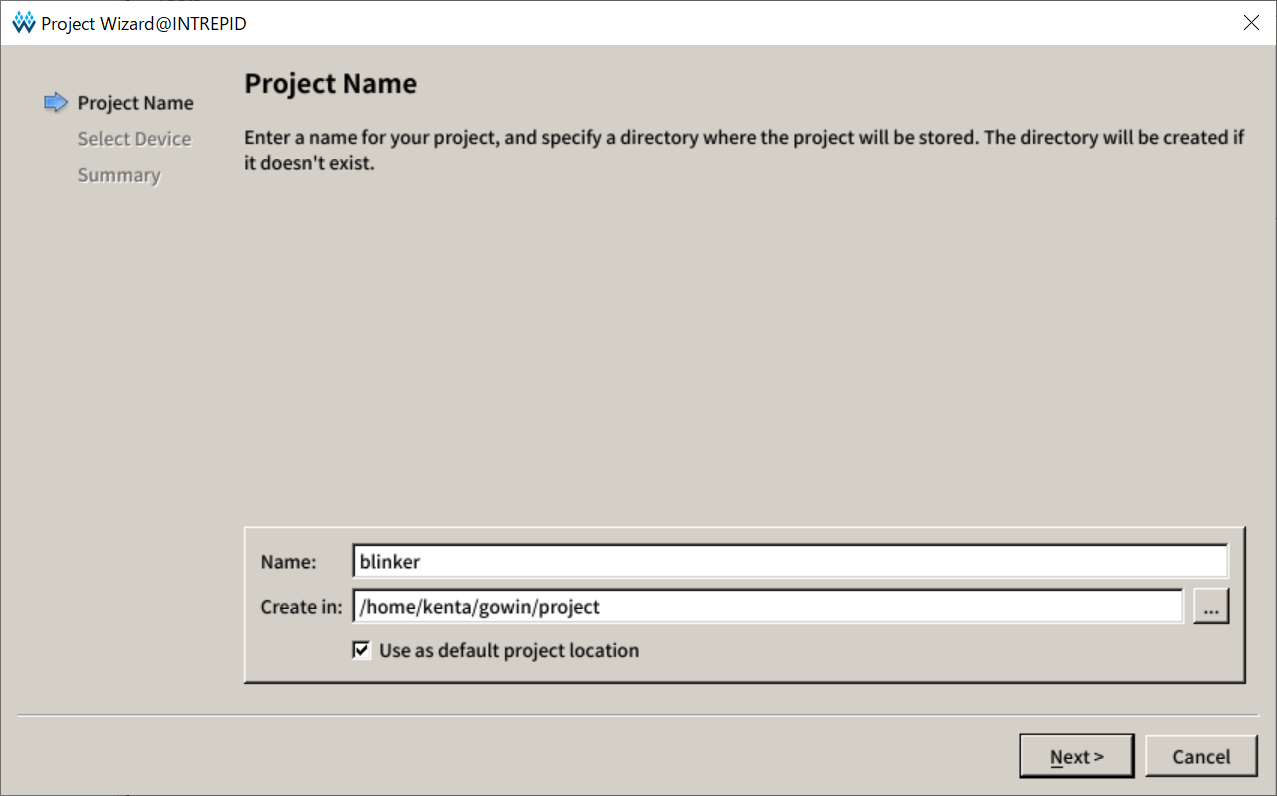

Project Wizardが表示されるので、プロジェクトの保存先のパスとして Create in: に適当なディレクトリのパスを入力します。

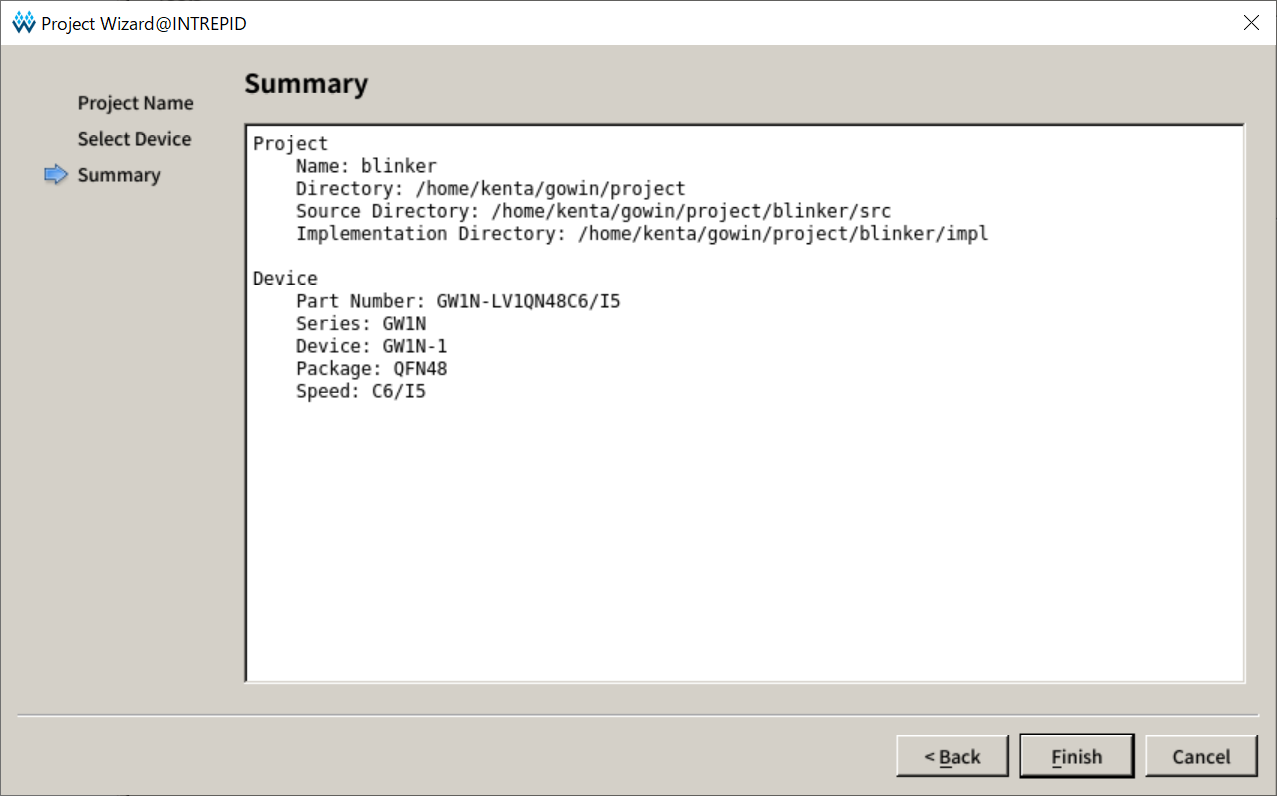

Name: には、プロジェクト名を入力します。ここでは適当にblinkerとでもしておきます。

入力したら Next を押します。

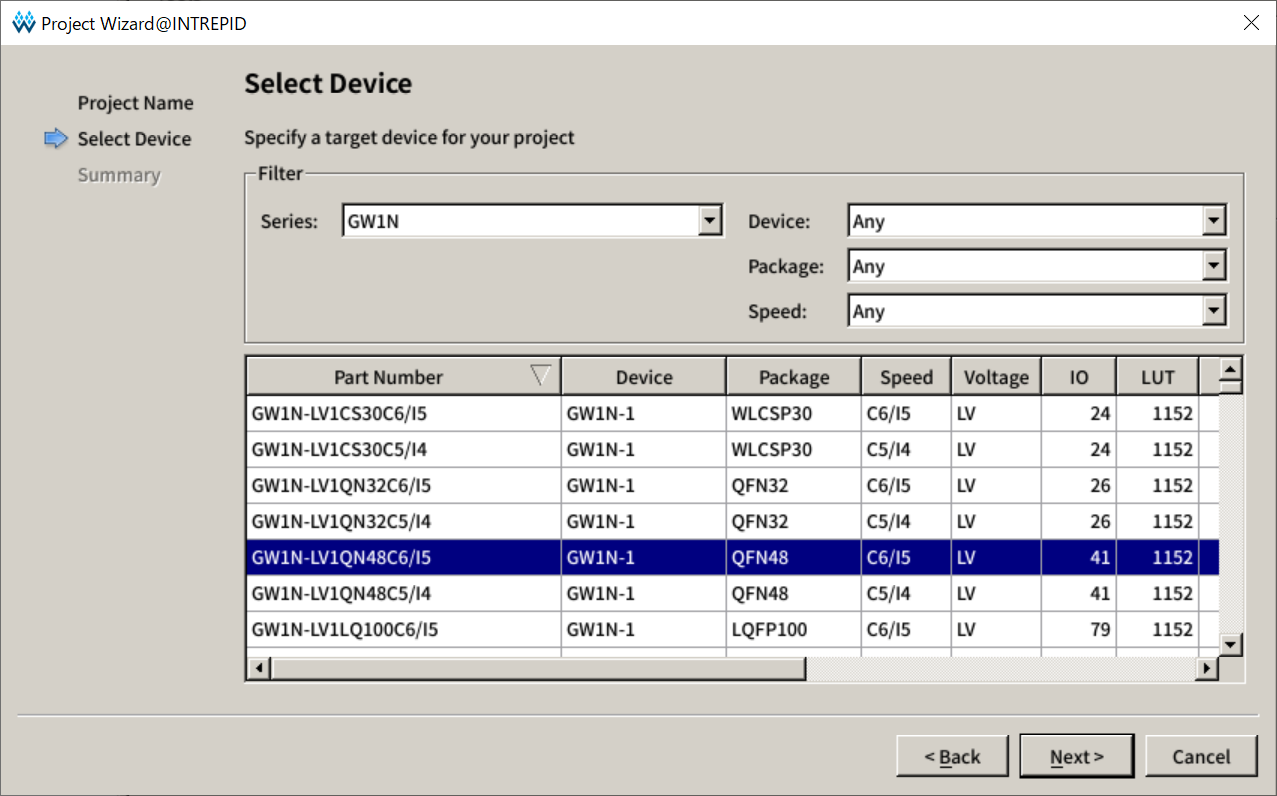

Select Device 画面が表示されるので、SeriesでGW1Nを選んで、下の表からGW1N-LV1QN48C6を選びます。

Summary 画面が表示されるので、 Finish を押します。

ソースファイルの追加

プロジェクトができたので、必要なファイルを追加します。

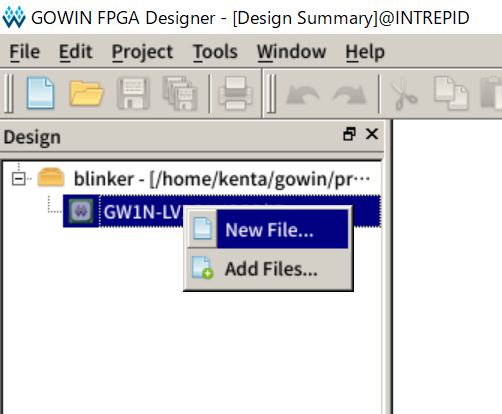

Designペインで右クリックしてNew Fileを選びます。

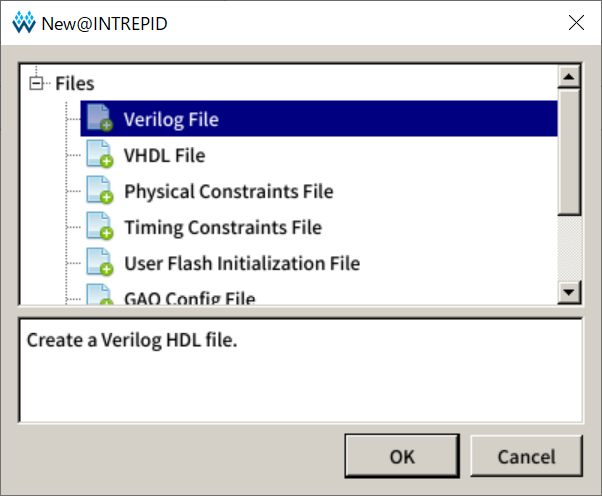

表示されたNewダイアログでVerilog Fileを選択しOKを押します。

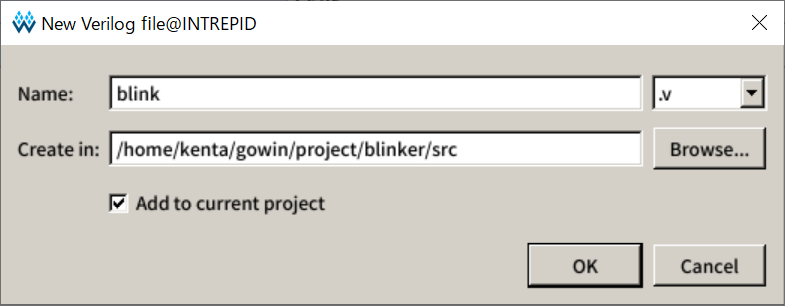

New Verilogダイアログが表示されるので、Nameにblinkと入力してOKを押します。

blink.v がエディタで開かれた状態になるので、下のコードをコピペして保存します。

clockと負論理のresetn入力を受け取り、カラーLEDのR, G, Bに対応する信号を出力する回路です。

Tang Nanoのデータシートによると24[MHz]の発信回路がボード上に搭載されているので、その発信回路をclockの入力とします。

また、ボード上にはアクティブローのプッシュボタンが2つ搭載されているので、そのうちの一つをresetnの入力にします。

内部ではdividerという名前の24bit幅のカウンタ、つまり2^24-1 = 16,777,215までカウントできるカウンタを持っており、このカウンタでクロックをDIVIDER_UPPER = 1200000 - 1 までカウントします。よってdividerは 1200000/24[MHz] = 1200000/2400000 = 0.5[s]ごとに0に戻ります。

dividerが0に戻る前のサイクルでled_outの値を1ずつ加算して、0.5[s]ごとにLEDの点灯パターンを変化させます。

計8パターンのLEDの点灯パターンを順に繰り返すようにします。

module blink (

input wire clock,

input wire resetn,

output wire led_r,

output wire led_g,

output wire led_b

);

reg [23:0] divider;

reg [2:0] led_out;

localparam [23:0] DIVIDER_UPPER = 24'd12_000_000 - 24'd1;

assign led_r = !led_out[0];

assign led_g = !led_out[1];

assign led_b = !led_out[2];

always @(posedge clock) begin

if( !resetn ) begin

divider <= 0;

led_out <= 0;

end

else begin

divider <= divider == DIVIDER_UPPER ? 0 : divider + 1;

led_out <= divider == DIVIDER_UPPER ? led_out + 1 : led_out;

end

end

endmodule

合成とIO制約の追加

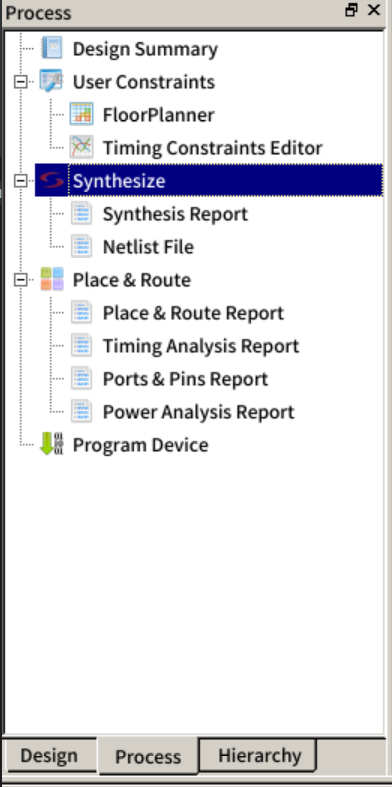

ここでIO制約を追加するため、一旦合成を行います。

右側のペインでProcessタブを開き、Synthesize をダブルクリックします。

ダブルクリックすると、Synthesize の左側のアイコンがぐるぐる回転する矢印に代わります。合成完了すると、以下のような画面画面になります。

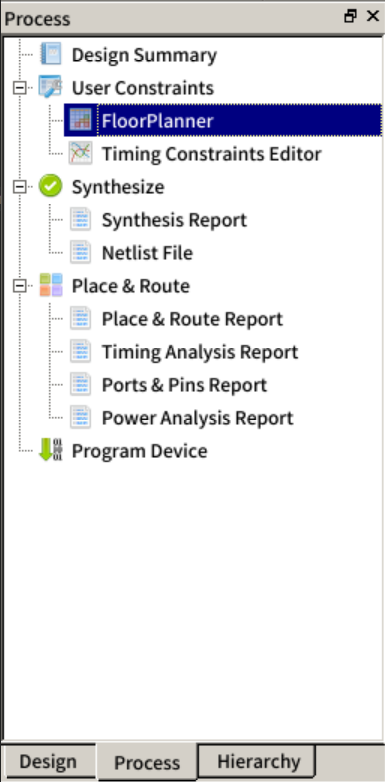

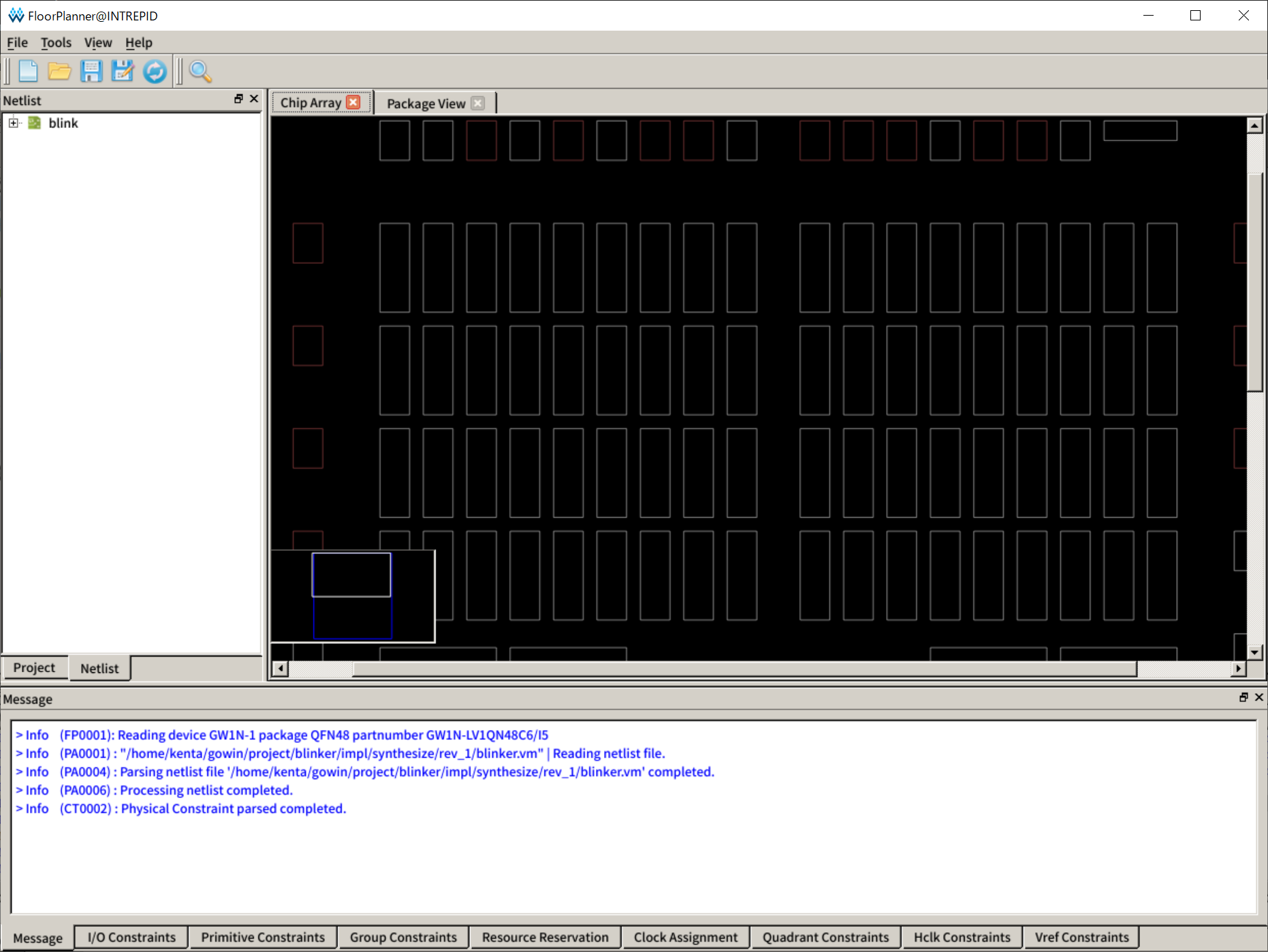

合成完了後、ProcessタブでFloorPlannerをダブルクリックします。

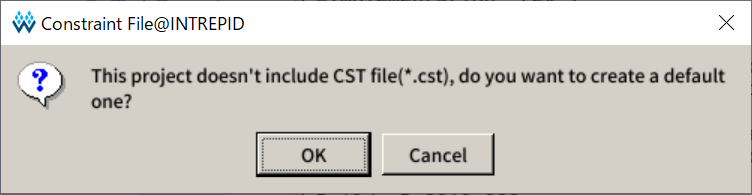

FloorPlannerの初回実行時はIO制約ファイル(*.cst)がないため、新しく作成するかどうかを確認するダイアログが表示されますので、OKを押します。

FloorPlannerは起動直後は以下のような画面になっています。

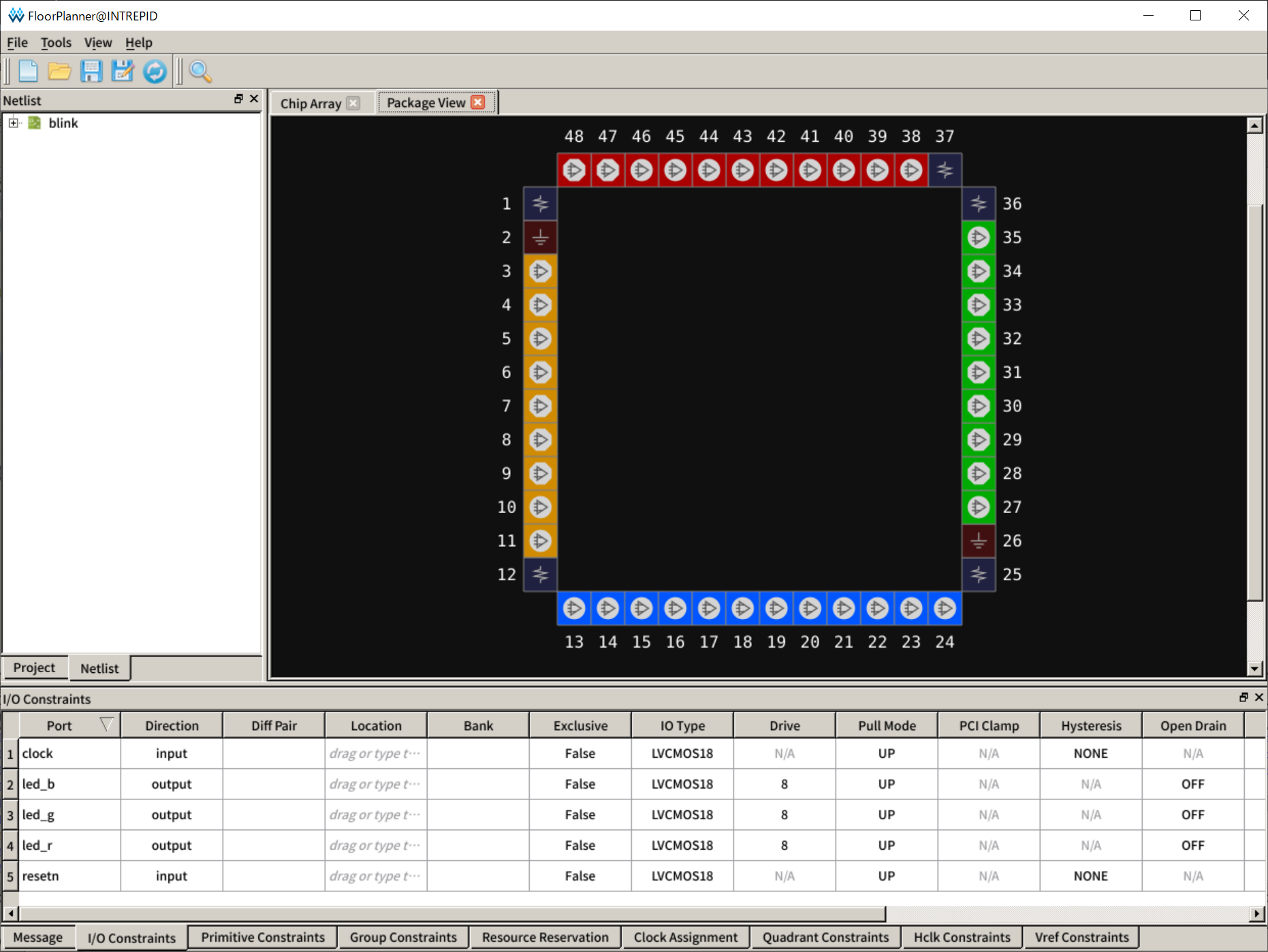

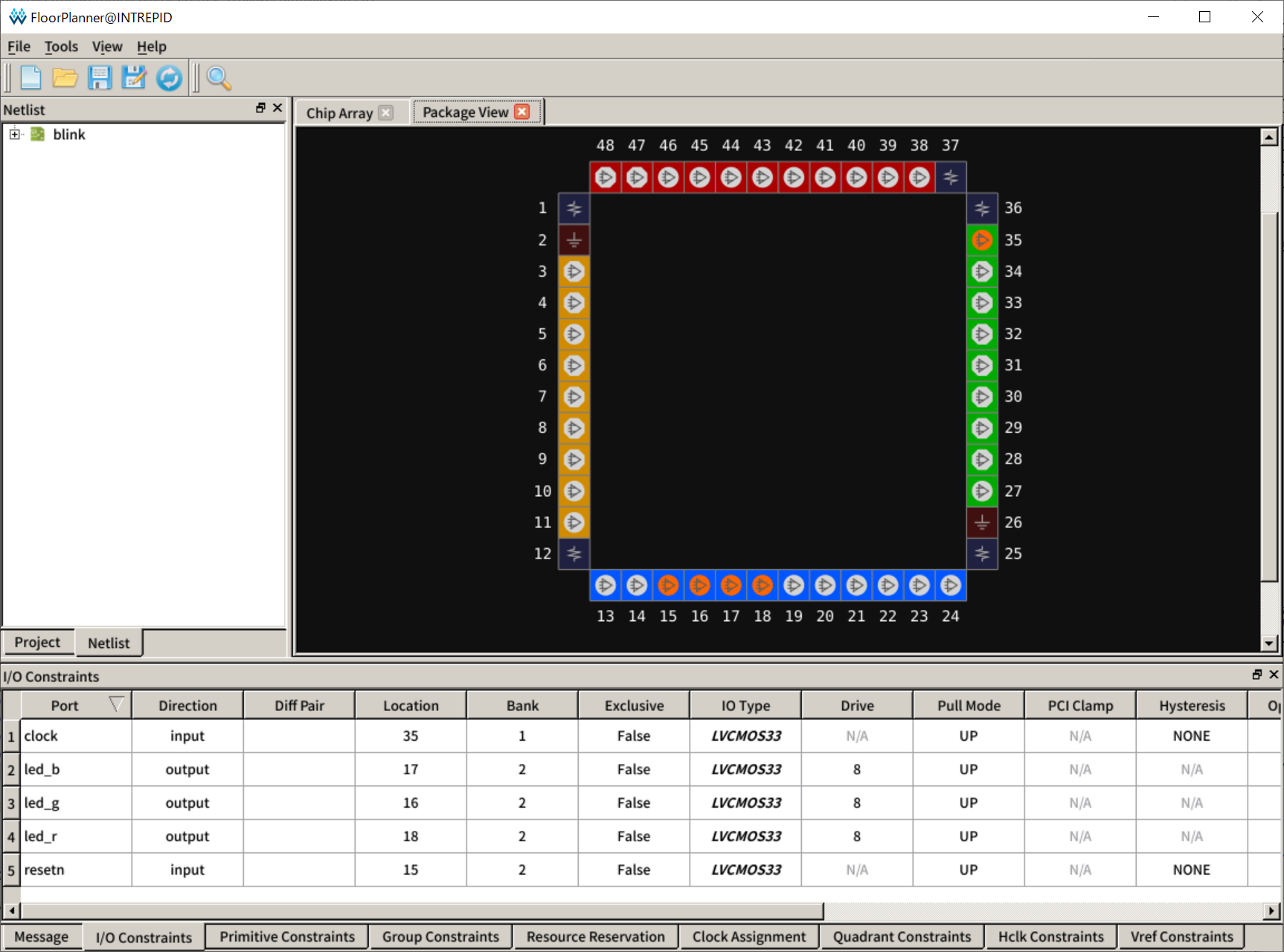

今回はIO制約を追加したいので、右上のペインでPackage Viewタブを開き、下のペインでI/O Constraintsタブを開きます。

現在のところ、合成した論理回路の各入出力ポートがFPGAのピンに割り当てられていませんので、Tang Nanoの回路図を見ながらピンを割り当てます。

ピンを割り当てるには、I/O Constraintsタブで割り当てを行いたいポートを選択し、Location列のセルをPackage Viewに表示されている割り当てたいピンにドラッグ&ドロップします。

各ポートのピン割り当ては以下の通りです。

| Port | Location | 備考 |

|---|---|---|

| clock | 35 | CH552と共用の24MHz水晶発振子の信号 |

| resetn | 15 | ボタンA (アクティブ・ロー) |

| led_r | 18 | カラーLEDの赤 (アクティブ・ロー) |

| led_g | 16 | カラーLEDの緑 (アクティブ・ロー) |

| led_b | 17 | カラーLEDの青 (アクティブ・ロー) |

回路図より、各ピンの属するIOバンクの電源電圧は3.3Vになっているので、IO Type列をLVCMOS33に変更します。

設定が完了したら保存してFloorPlannerを閉じます。

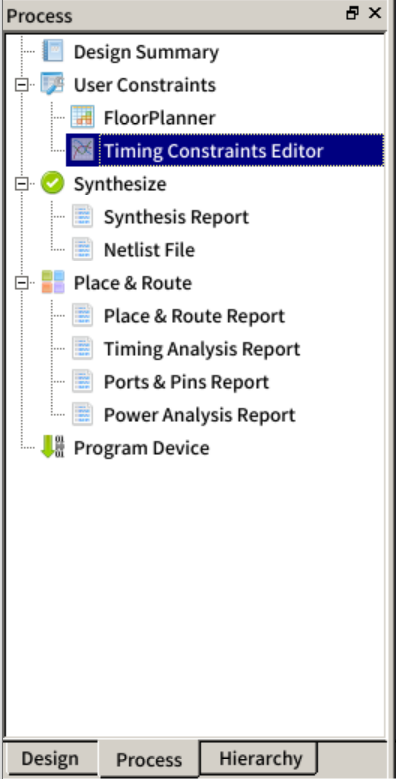

タイミング制約の追加

必須ではありませんが、一応タイミング解析を行えるようにタイミング制約を追加します。

ProcessタブからTiming Constraints Editorをダブルクリックします。

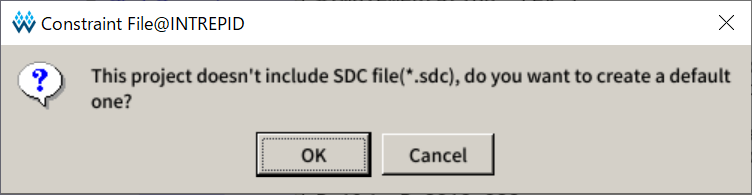

IO制約の時と同様に制約ファイル(*.sdc)が無いため新規作成するか確認されるので、OKを選びます。

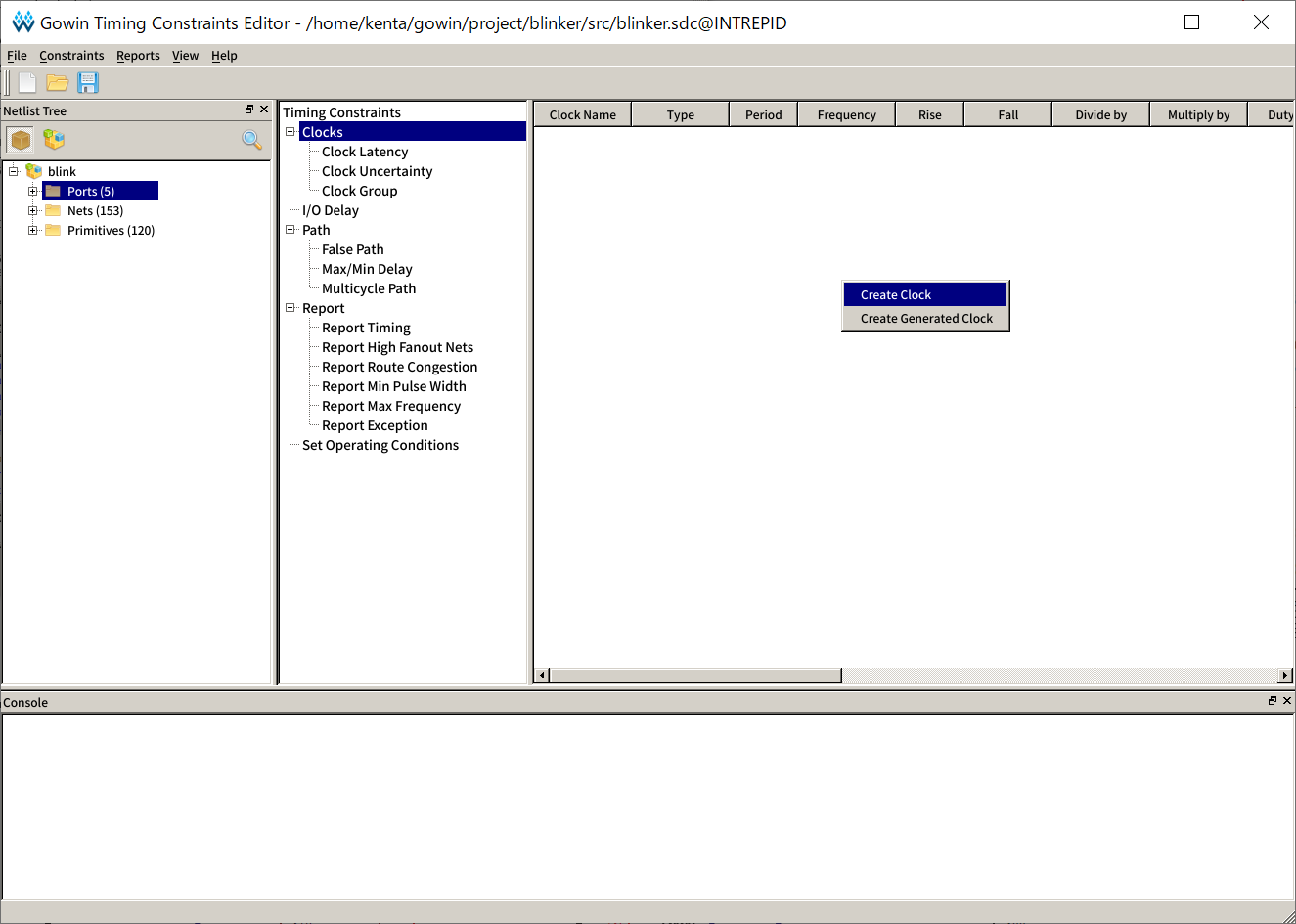

Gowin Timing Constraints Editor が表示されるので、右側の画面で右クリックし、Create Clockを選びます。

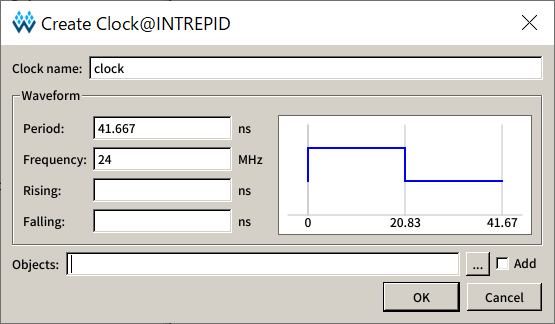

Create Clockダイアログが表示されるので、Clock nameにclock、Frequencyに24[MHz]を入力します。

Objects横の...を押してSelect Objectsダイアログを表示します。

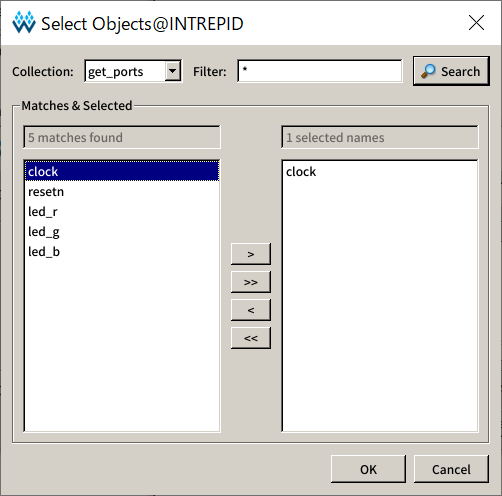

Collectionでget_ports、Filterに*を入力した状態でSearchボタンを押します。Matches&Selectedリストにポート一覧が表示されるので、clockを選んで>を押します。その後、OKを押してSelect Objectsダイアログを閉じます。

Create Clockダイアログに戻ると、Objectsに[get_ports {clock}]が入力されるので、OKを押します。

保存して Timing Constraints Editor を閉じます。

配置配線とビットストリームの生成

ProcessペインでPlace & Routeをダブルクリックします。しばらくすると配置配線が終わります。

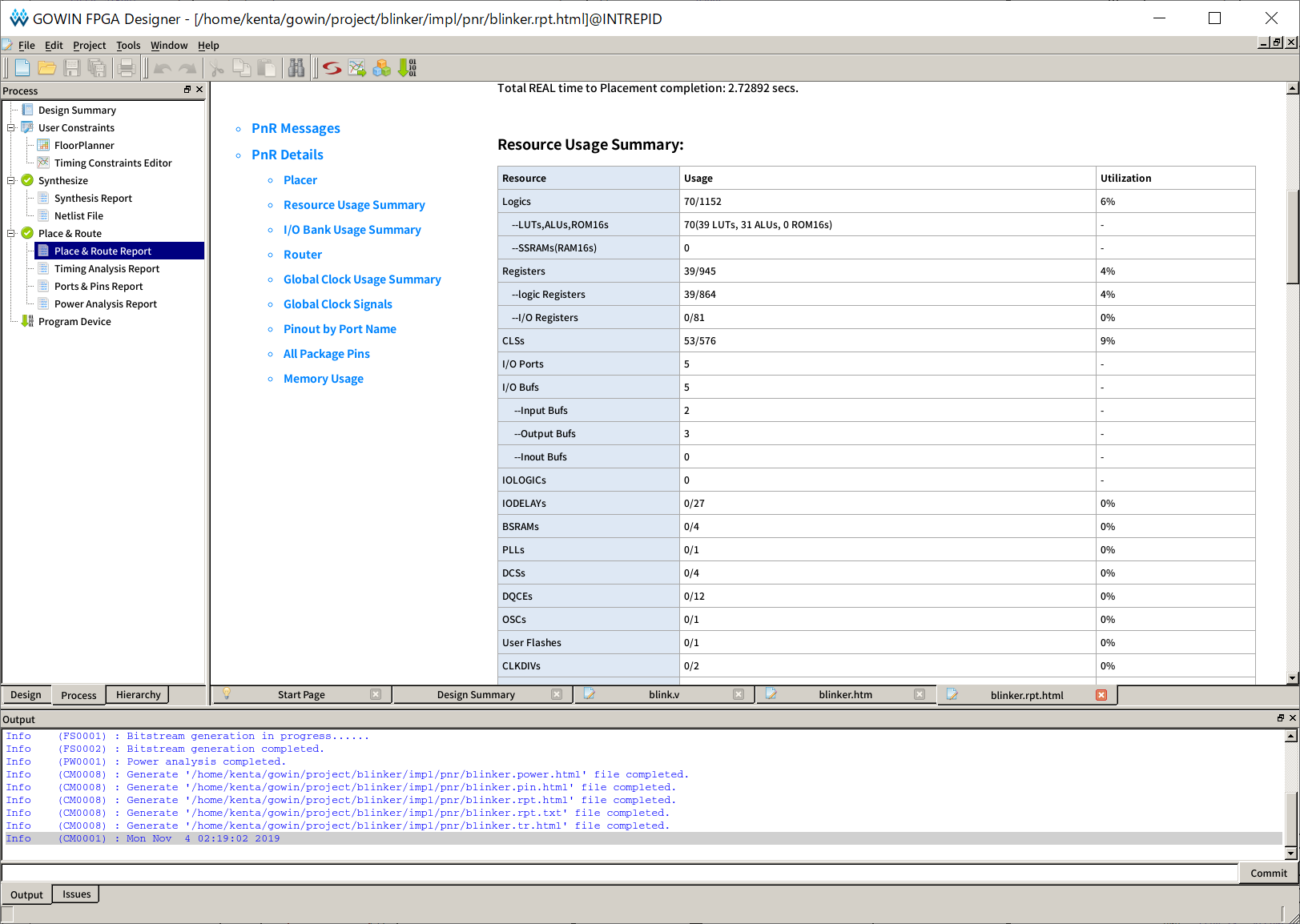

Place & Route Reportをダブルクリックすると、配置配線結果のレポートが表示されます。

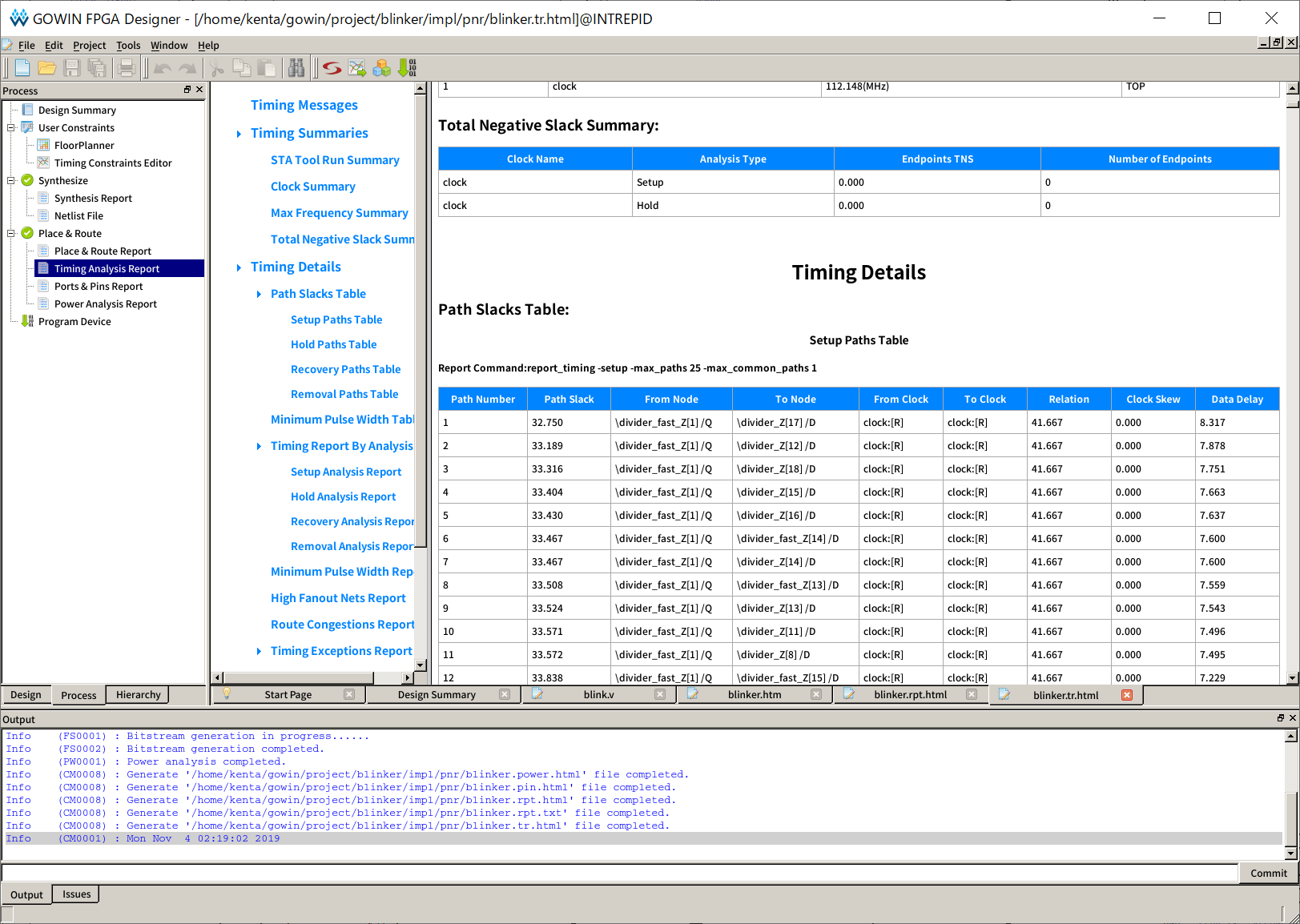

Timing Analysis Reportをダブルクリックすると、タイミング解析結果が表示されます。とりあえずタイミング制約違反は無いようです。

ビットストリームの書き込み

ボードに書き込むためのビットストリームを作り終わったので、実際にボードに書き込んで動かしてみます。チュートリアルではFlashへの永続的なコンフィグレーション手順が記載されていますが、とりあえず実験用にSRAMにコンフィグします。(電源を落とすともとに戻ります)

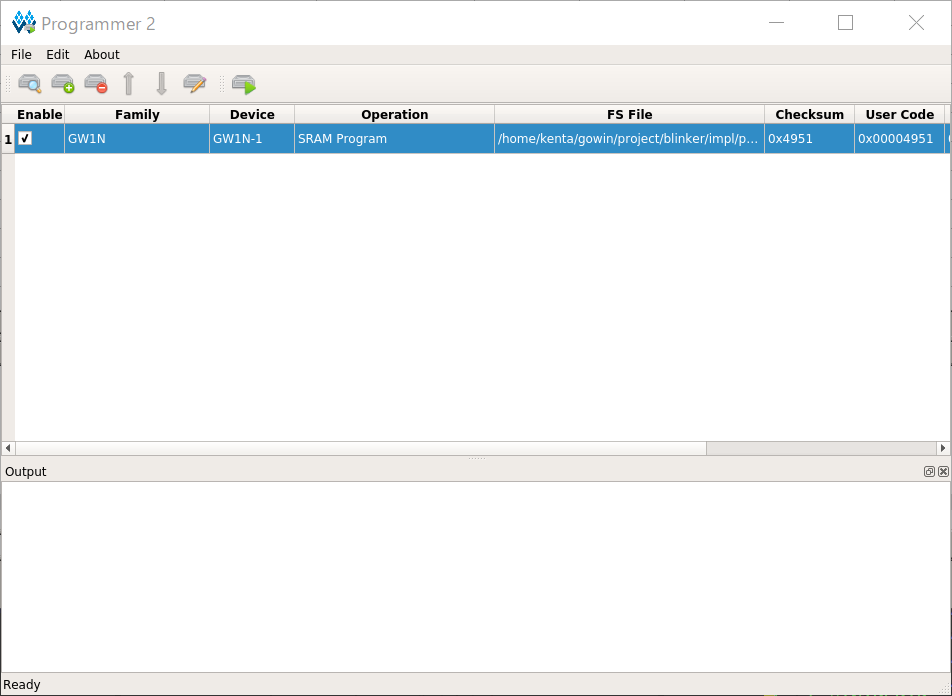

ここで注意しないといけないのは、書き込みに管理者権限が必要なため、Programmerを手動で起動することです。

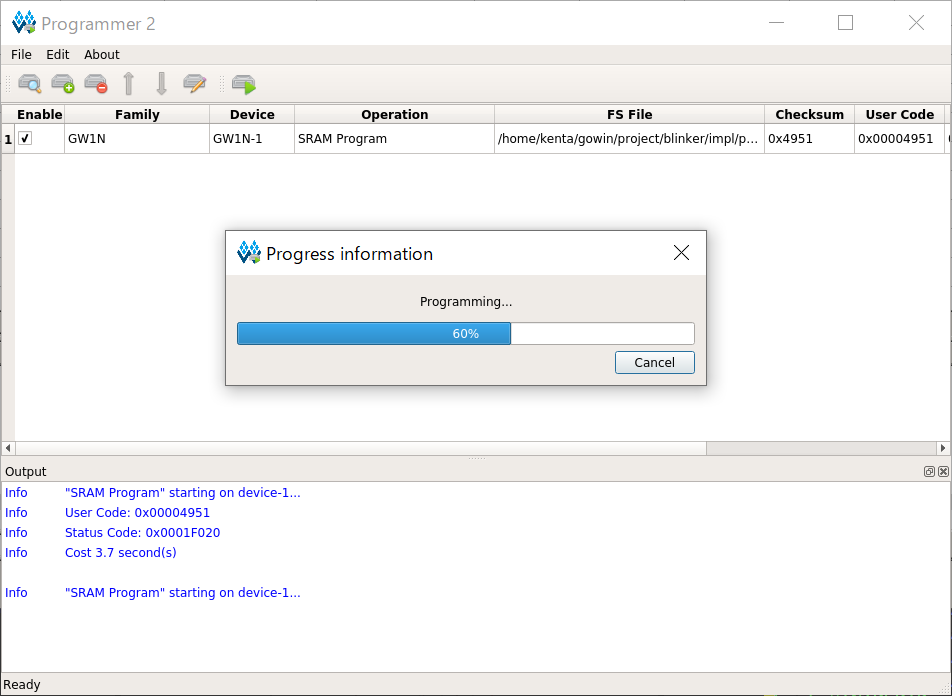

Programmer/bin/programmerを管理者で起動します。

sudo Programmer/bin/programmer

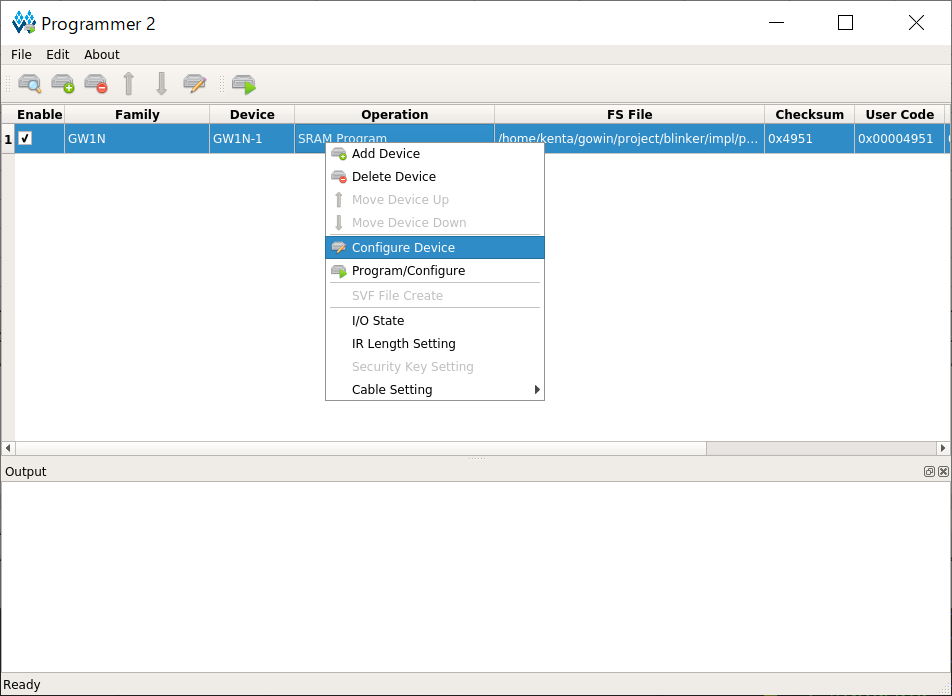

起動したら右クリックしてConfigure Deviceを選びます。

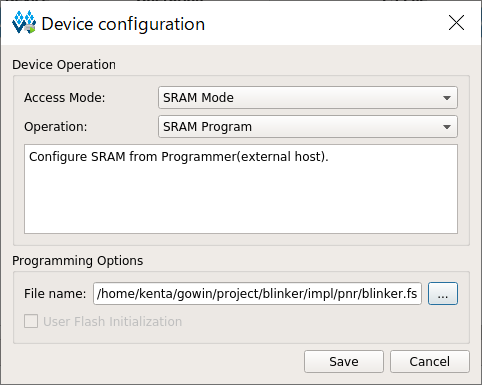

Device configurationダイアログが表示されるので、Access ModeでSRAM Mode、OperationでSRAM Programを選びます。

また、Programming OptionsのFile name右にある...を押して、

(プロジェクトのディレクトリ)/impl/pnr/blinker.fs を選びます。

Saveを押してDevice configurationダイアログを閉じ、さらに右クリックメニューからProgram/Configureを選ぶと、ビットストリームの書き込みが始まります。

Programmerを一般ユーザーでも使えるようにする

いちいち管理者で起動するのは面倒なので、udevの設定をして管理者で起動しなくても良いようにします。

以下のファイルを作成します。

SUBSYSTEMS=="usb", ATTRS{idVendor}=="0403", ATTRS{idProduct}=="6010", ATTRS{product}=="Sipeed-Debug", GROUP="users", MODE="0666"

udevの設定を再読込します。

sudo udevadm control --reload

Tang NanoをUSBポートから抜いて挿し直します。

その後、ftdi_sioドライバをアンロードします。

sudo modprobe -r ftdi_sio

これで一般ユーザーでもTang Nanoにアクセスできるようになります。

試しにコマンドライン版Programmerを実行してみます。

$ Programmer/bin/programmer_cli --channel 0 --device GW1N-1 --operation_index 0

"Read Device Codes" starting on device-1...

ID code is: 0x0900281B

User code is: 0x00004951

Status code is: 0x0001F020

Cost 1.04 second(s)