はじめに

Vivado 2021から「Intelligent Design Run」というタイミングクロージャが導入されました。

スクリプトを含め、適用してタイミングを収束させた結果等を紹介します。

なお、この機能は別途ライセンス追加等はありませんのですぐに試すことが可能です。

Intelligent Design Runとは

機械学習ベースアルゴリズムでタイミング収束させる機能のようです。

Strategyに適したデザインを認識し、コンパイルの試行でモデルを構築・学習し、タイミングを収束します。

ユーザーの作業はIntelligent Design Runを実行させるだけとなります。

タイミングを収束させるために、配置配線Strategyを変える方法がありますが、Vivadoにプリセットで入っているStrategyは30セット近くに及ぶため、これらを全て同時実行できるほどホストのスペックが非常に高い場合はさておき、特性を理解しチョイスして配置配線を実行し、タイミングが収束しなかったらStrategyを変えて再実行...と大変な作業となります。

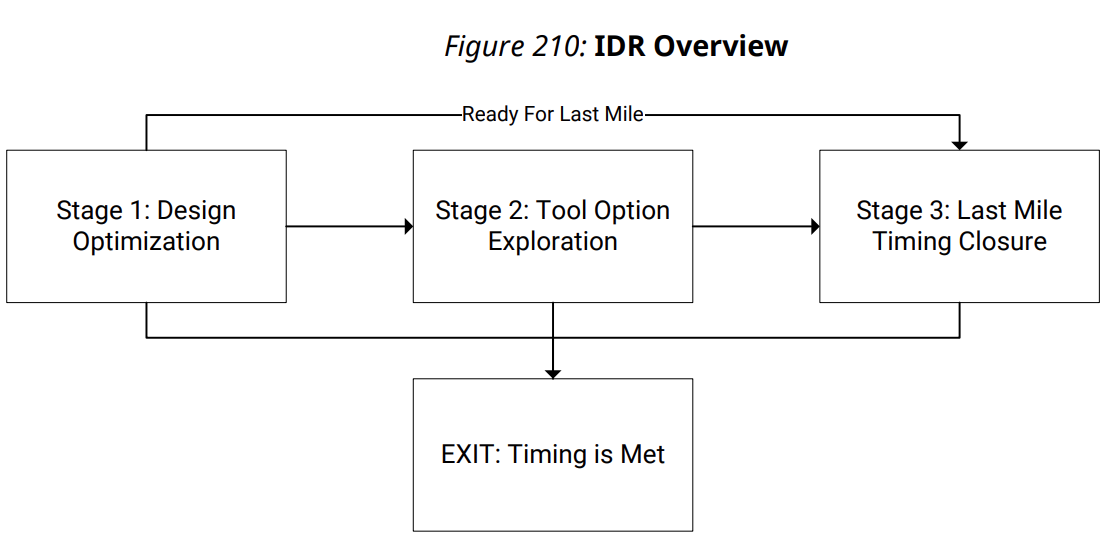

Intelligent Design Runの詳しいステップはこちらに記載されていますが、中身は知らなくても1回実行するだけでタイミング収束のイタレーションをツールがやってくれるので有力な手段となります。

Intelligent Design Runの実行方法

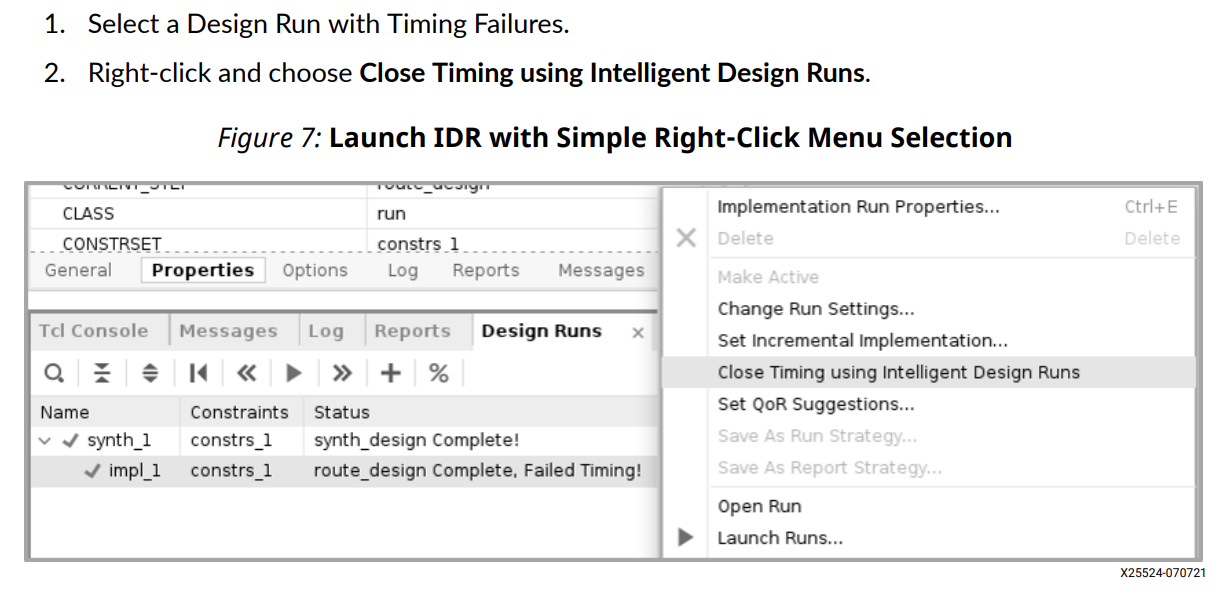

具体的な実行方法としては、通常の配置配線を実行後に、メニューから「Close Timing using Intelligent Design Runs.」を選択し、Runさせるだけです。

https://japan.xilinx.com/support/documentation/white_papers/wp535-intelligent-design-runs.pdf

実行スクリプト

GUIでは面倒なので、論理合成・配置配線からIntelligent Design Runを実行するスクリプトを以下に作成しました。

create_run -flow {Vivado IDR Flow 2021} -parent_run synth_1 i_impl_1コマンドでIntelligent Design Run用のRunセットi_impl_1を生成し、その前の配置配線結果をリファレンスとしてIntelligent Design Runを実行します。

Intelligent Design Runが終了すると、reate_single_pass_run -reference_run [get_runs i_impl_1] impl_2でタイミングクロージャの結果を通常の配置配線Runにimpl_2としてRunを作成し、再び配置配線を実行します。

# Implementation

launch_runs impl_1 -jobs 32

wait_on_run impl_1

# Intelligent Design Run

create_run -flow {Vivado IDR Flow 2021} -parent_run synth_1 i_impl_1

set_property REFERENCE_RUN impl_1 [get_runs i_impl_1]

launch_runs i_impl_1 -jobs 32

wait_on_run i_impl_1

# Export the results of Intelligent Design Run to Normal run

create_single_pass_run -reference_run [get_runs i_impl_1] impl_2

# Implementation

launch_runs impl_2 -to_step write_bitstream -jobs 32

wait_on_run impl_2

Ultra96 V2を対象とした実行結果

Intelligent Design RunをUltra96 V2をターゲットに配置配線を実行しました。

実行対象の回路のクロックは300MHzで、使用率は以下の通りです。

| Resource | Utilization % |

|---|---|

| LUT | 80.00 |

| LUTRAM | 20.00 |

| FF | 49.68 |

| BRAM | 53.01 |

実行結果を以下に示します。

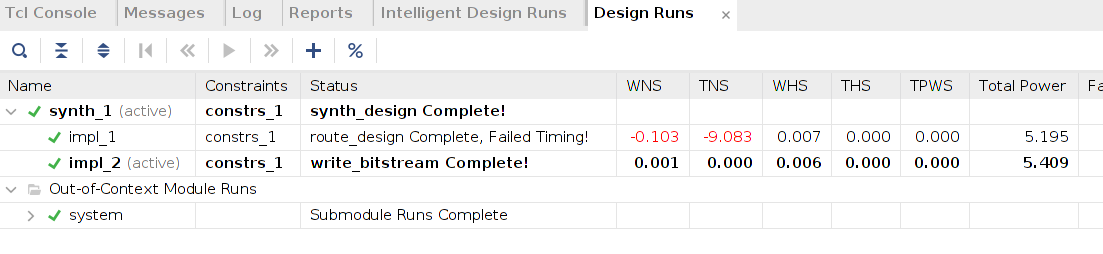

「impl_1」がデフォルトの配置配線、「impl_2」がIntelligent Design Runを適用した配置配線結果です。デフォルトの配置配線ではタイミング違反となりますが、Intelligent Design Runを実行した結果、WNSがMetし、300MHzで動作できるように配置配線を実施することができました。

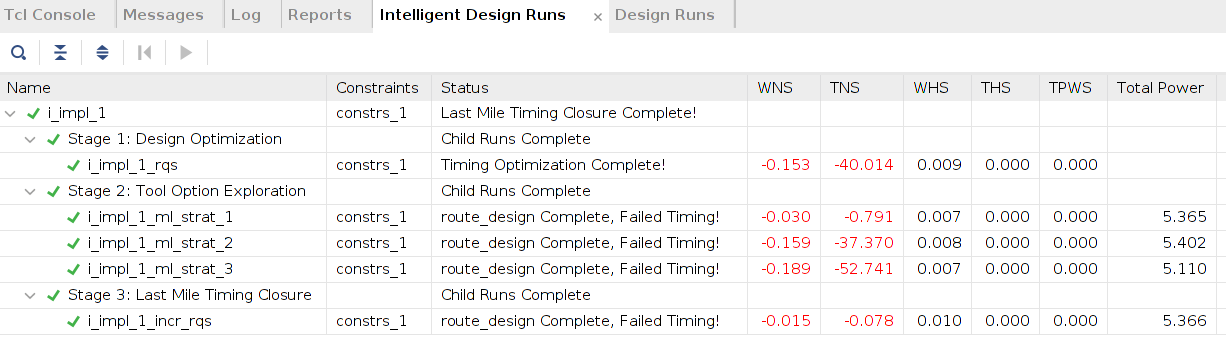

Intelligent Design Runを実施した時の、各課程の結果は以下の通りです。

Intelligent Design Runの実行は大きく3ステージに分かれ、ステージ1でデザインの最適化、ステージ2で3通りのML Strategyによる最適化の探索を行い、ステージ3で最もQoRの良いStrategyを利用してタイミング収束を試みているようです。

おわりに

Vivado 2021から追加されたIntelligent Design Runによるタイミング収束例について紹介しました。

複雑なスクリプトを記述することなく実行できるので、とりあえずはチャレンジしてみようかという気にさせられます。

ご参考まで。