DE0-Nanoでダブルパルスを出すVerilog HDLのリスト。

初学者ゆえ、よくわかっていないで書いている部分が多々あります。

「こういう書き方のほうがよい」等のアドバイスをいただけると助かります。

module double_pulse(CLOCK, GPIO);

input CLOCK; // 50MHz. 1clock = 20nsec.

output [33:0] GPIO;

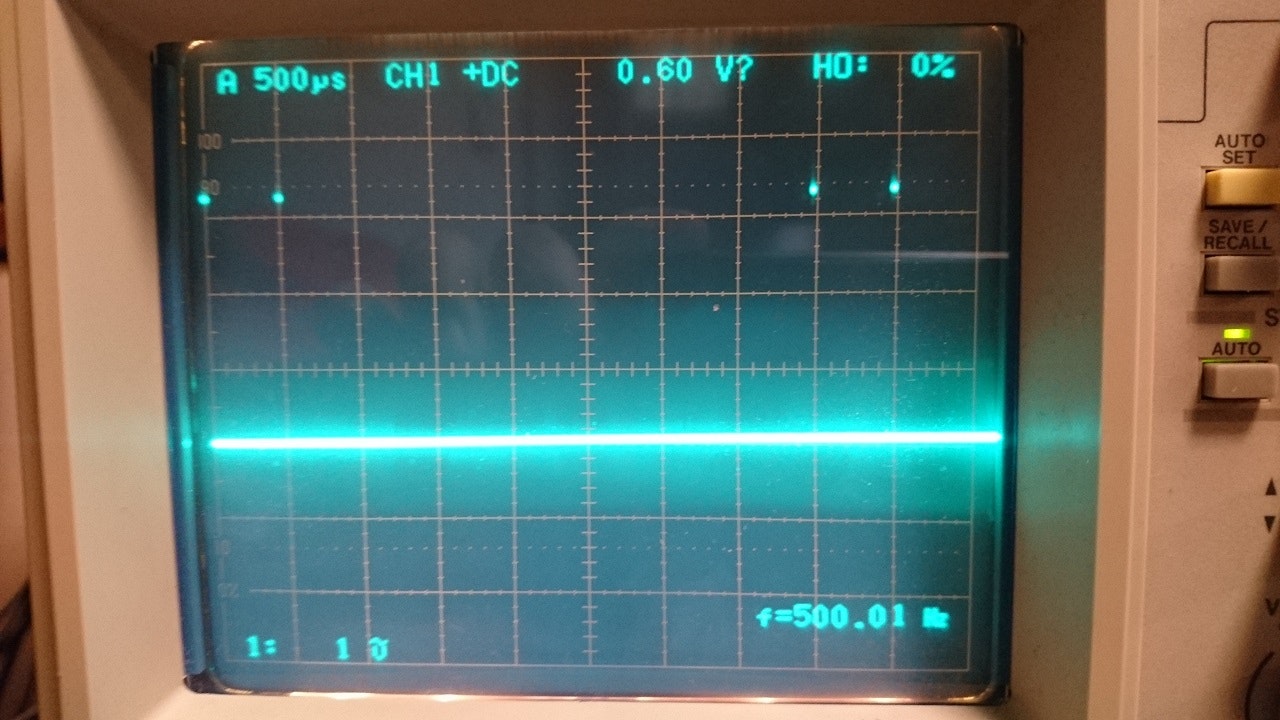

parameter [17:0] pulse_cycle = 199999; // 200000*20nsec = 4000usec

parameter [17:0] pulse1_start = 0;

parameter [17:0] pulse1_width = 200; // 200*20nsec = 4usec

parameter [17:0] pulse_interval = 25000; // 25000*20nsec = 500usec

parameter [17:0] pulse2_start = pulse1_width + pulse_interval;

parameter [17:0] pulse2_width = pulse1_width;

reg [17:0] pulse_cycle_count = 0;

reg pulse;

always @(posedge CLOCK) begin

if(pulse_cycle_count == pulse_cycle) begin

pulse_cycle_count = 0;

end

else begin

pulse_cycle_count = pulse_cycle_count + 1;

end

end

always @(posedge CLOCK) begin

if(pulse_cycle_count == pulse1_start) begin

pulse = 1;

end

else if(pulse_cycle_count == pulse1_start + pulse1_width) begin

pulse = 0;

end

if(pulse_cycle_count == pulse2_start) begin

pulse = 1;

end

else if(pulse_cycle_count == pulse2_start + pulse2_width) begin

pulse = 0;

end

end

assign GPIO[0] = CLOCK;

assign GPIO[1] = pulse;

endmodule

やっていることは単純にクロックでカウンターを回して周期をつくり、何クロック目でパルスをオン/オフするか条件分岐しているだけです。

だから分解能は20nsec。

どうにか工夫して10nsecまであげられないものでしょうか。