※本記事は、Nios® V processor インストール、Hello World実行編のアップデート記事です。

はじめに

この記事では、はじめてFPGAに触れる方を対象としてNios® V/m embedded processorの概要、インストール、ハードウエア構築、Hello Worldの実行までを行います。既にFPGAの経験がある方は、インストールなど一部は読み流して頂ければよいかと思います。

動作検証に使用したOSは下記となります。

Windows 11 Enterprise Version:22H2, Build:22621.2715

Ubuntu 22.04.3 LTS (Jammy Jellyfish), Kernel version:6.2.0-36-generic

基本的にはLinux上で作業を進め、実際のログを含めて説明します。しかし、Windowsでは明らかにコマンドが異なる場合はその都度説明します。

以下はNios® V/m embedded processor参考資料です。

- Nios® V Embedded Processor Design Handbook

- Nios® V Processor Reference Manual

- NiosV tool setup for Eclipse CDT and OpenOCD

1. Nios® V/m embedded processor概要

1.1 命令セット

Nios® V/m embedded processorはRV32IA命令セットをサポートしています。RV32Iが32ビット整数命令セットを意味し、その後に続く記号が拡張機能を示します。主な拡張機能を下記に示します。

| Extension | Description |

|---|---|

| M | Integer Multiplication and Division |

| A | Atomic Instructions |

| F | Single-Precision Floating-Point |

| D | Double-Precision Floating-Point |

| Q | Quad-Precision Floating-Point |

| C | Compressed Instructions |

従って、R32IAは32ビット整数命令と排他制御命令をサポートしているプロセッサーとなります。整数レジスタは32ビット幅が32本実装され、M20Kなどのブロックメモリーで実装されています。また、拡張記号から解る通り、浮動小数点レジスタ(f0-f31,fcsr)は実装されていません。詳しくはRISC-V Unprivileged Spec v.20191213を参照してください。

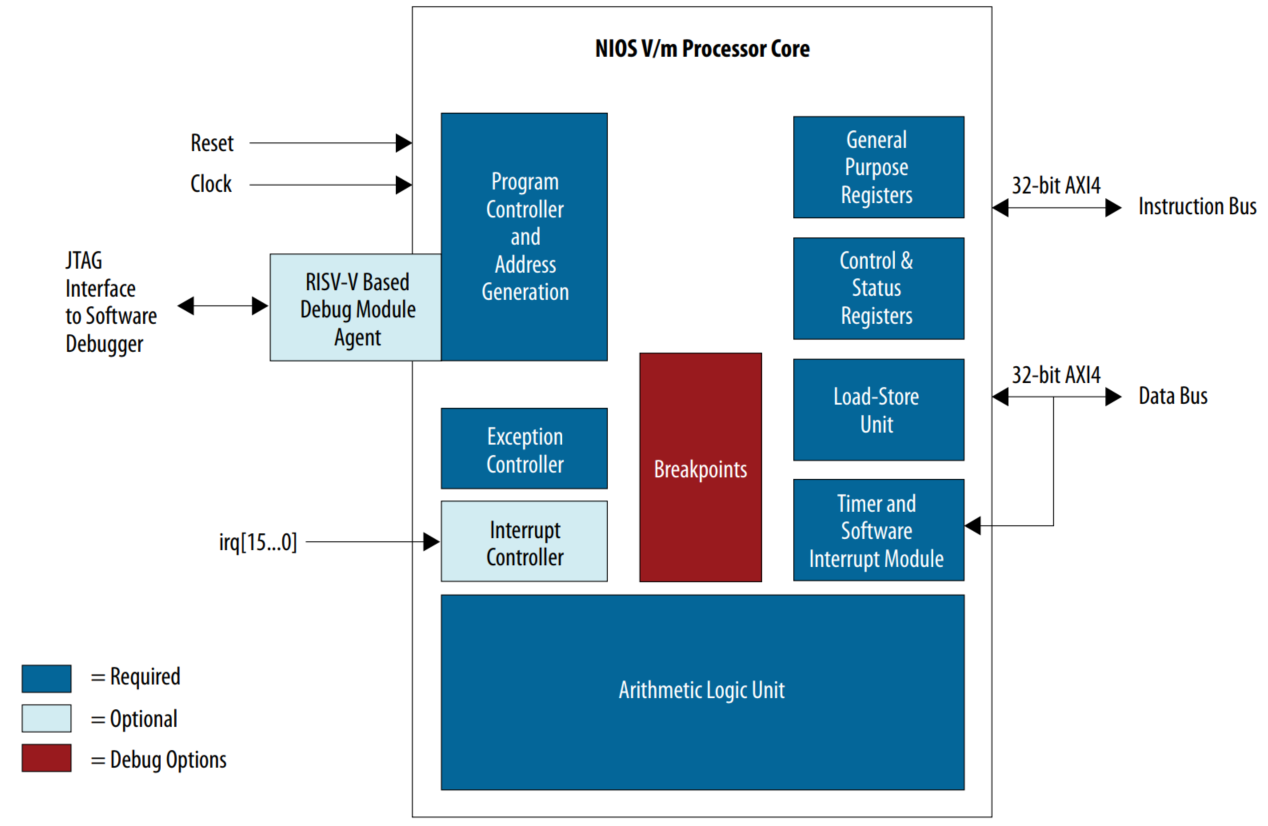

1.2 構成

| Item | 詳細 |

|---|---|

| General Purpose Register file | 32ビット幅x32本の整数汎用レジスタファイル |

| Arithmetic Logic Unit (ALU) | 算術、比較、論理、シフト演算を実行。ロード、ストアのアドレス生成にも使用 |

| Control and Status Registers (CSR) | 制御レジスタ |

| Exception Controller | 例外処理コントローラー |

| Interrupt Controller | 割り込みコントローラー、レベルトリガー |

| Instruction Bus | 命令バス |

| Data Bus | データバス |

| RISC-V based Debug Module | デバッグモジュール |

ここでNios® IIと主な違いを示します。

| 項目 | Nios® V/m embedded processor | Nios® II |

|---|---|---|

| バス | Arm* ABMA* AXI | Avalon-MM |

| 割り込み端子数 | 16 | 32 |

| デバッグ | Open OCD(On-Chip Debugger)準拠 | 独自仕様 |

1.3 命令、データバス

Nios® IIではバスはAvalon-MMを使用していましたが、Nios® V/m ProcessorからはArm* ABMA* AXIに変更されました。この変更により、AXIからのレスポンスがOKでない場合、Nios® V/m Processorに例外を発生させることができるようになりました。AXIの応答種類を下記に示します。

| RESP[1:0] | Response | Description |

|---|---|---|

| 2'b00 | OKAY | 通常アクセスOK |

| 2'b01 | EXOKAY | 排他アクセスOK |

| 2'b10 | SLVERR | スレーブがエラーを返した場合 |

| 2'b11 | DECERR | 指定したアドレスにスレーブが存在しない場合 |

詳しくはRead and write response structureをご参照ください。

1.4 パイプライン

Nios® V/m embedded processorは5ステージパイプラインCPUです。各ステージの概要を下記に示します。

| Stage | Denotation | Function |

|---|---|---|

| Instruction Fetch | F | • PC+4 calculation • Next instruction fetch • Pre-decode for register file read |

| Instruction Decode | D | • Decode the instruction • Register file read data available • Hazard resolution and data forwarding |

| Instruction Execute | E | • ALU operations • Memory address calculation • Branch resolution • CSR read/write |

| Memory | M | • Memory and multicycle operations • Register file write • Branch redirection |

| Write Back | W | • Facilitates data dependency resolution by providing General Purpose Register value. |

1.5 例外

現在定義されている例外を下記に示します。

| Exception | Description |

|---|---|

| Instruction Address Misaligned | 命令フェッチステージにて、プログラムカウンター(PC)が32ビット境界に整列していない(PCの下位2ビットが0でない)場合に例外発行 |

| Instruction Access Fault | 命令リード時のAXIの応答がOKAYでない場合に例外発行 |

| Illegal Instruction | 命令デコード時において、未実装、未定義の命令を検出した場合又は、実行ステージにおいて、未実装、未定義のCSRアクセスを検出した場合に例外発行 |

| Breakpoint | ブレイク命令を実行した場合にデコードステージにて例外発行 |

| Load Address Misaligned Store/AMO address misaligned |

メモリーアクセスステージにおいて、ロードストア命令のアクセスサイズにアドレスが整列していない場合に例外発行 |

| Load Access Fault Store/AMO access fault |

メモリアクセスにおいてAXIバスがOKAYでない応答を返した場合例外発行 |

| Environment call from U-mode | ECALL命令をU-modeで実行した場合例外発行 |

| Environment call from S-mode | ECALL命令をS-modeで実行した場合例外発行 |

| Environment call from M-mode | ECALL命令をM-modeで実行した場合例外発行 |

| Instruction page fault Load page fault Store/AMO page fault |

物理アドレスに対応しない仮想アドレスにアクセスするか、アクセス権が不十分である場合に例外発行 |

1.6 CSRレジスタ

下記にCSR領域にマップされているレジスタを示します。レジスタの詳細に関してはRISC-V Privileged Spec v.20190608を参照してください。

| Register Name | Description |

|---|---|

| mvendorid | Machine Vendor ID Register |

| marchid | Machine Architecture ID Register |

| mimpid | Machine Implementation ID Register |

| mhartid | Hart ID Register |

| mstatus | Machine Status Register |

| mtvec | Machine Trap-Vector Base-Address Register |

| mip | Machine interrupt-pending register |

| mie | Machine interrupt-enable register |

| mcounteren | Machine Counter-enable register |

| mepc | Machine Exception Program Counter |

| mcause | Machine Cause Register |

下記にメモリマップ領域にマップされているレジスタを示します。

| Register Name | Description | Offset |

|---|---|---|

| mtimecmp | Machine time register | 0x00 |

| mtime | Machine time register | 0x08 |

1.7 サポートデバイス

現在サポートしているFPGAデバイスは下記の通りです。

| Intel® Quartus® Prime Edition | Device Family |

|---|---|

| Pro | Intel® Cyclone® 10 device |

| Pro | Intel® Arria® 10 device |

| Pro | Intel® Stratix® 10 device |

| Pro | Intel Agilex® 7 device |

| Standard | Intel® MAX® 10 |

| Standard | Intel® Cyclone® IV E |

| Standard | Intel® Cyclone® IV GX |

| Standard | Intel® Cyclone® V |

| Standard | Intel® Cyclone® 10 LP |

| Standard | Intel® Arria® 10 |

| Standard | Intel® Arria® II GX |

| Standard | Intel® Arria® II GZ |

| Standard | Intel® Arria® V |

| Standard | Intel® Arria® V GZ |

| Standard | Intel® Stratix® IV |

| Standard | Intel® Stratix® V |

2. ライセンス取得

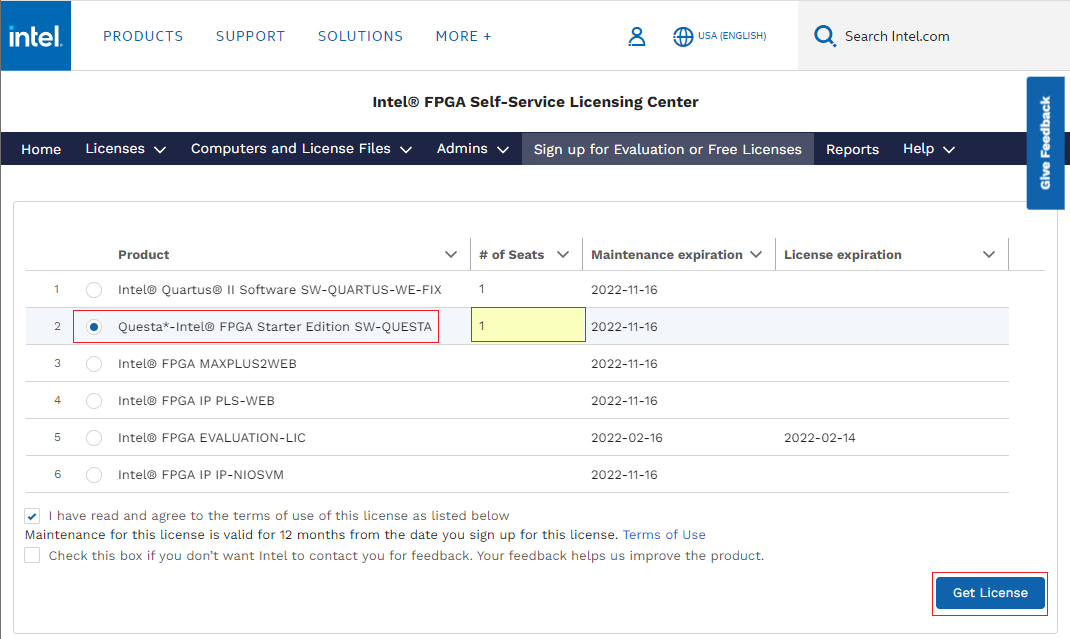

Nios® V/m embedded processorを使用するには無償ライセンスを取得する必要があります。ここではライセンス取得手順について説明します。また、シミュレータとしてQuesta*-Intel® FPGA Edition Softwareのライセンスも併せて取得します。

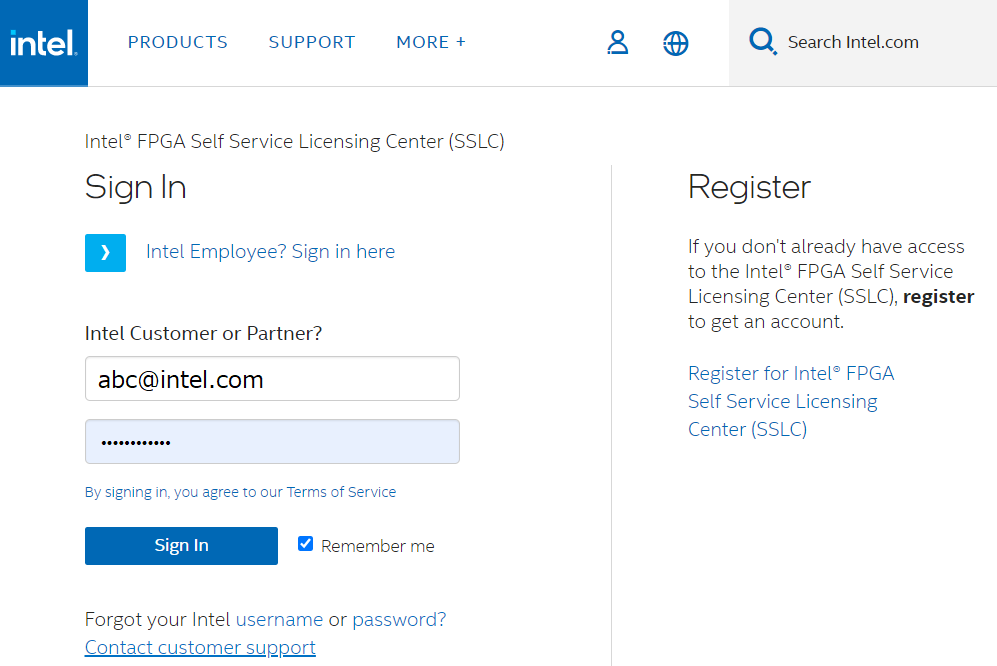

2.1 Sign In

Self Service Licensing Centerをクリックします。

下記にようなSign In画面が表示されますので、自分のIntelアカウントでSign Inしてください。

Intelのアカウントをお持ちでない場合は、アカウントを作成してください。

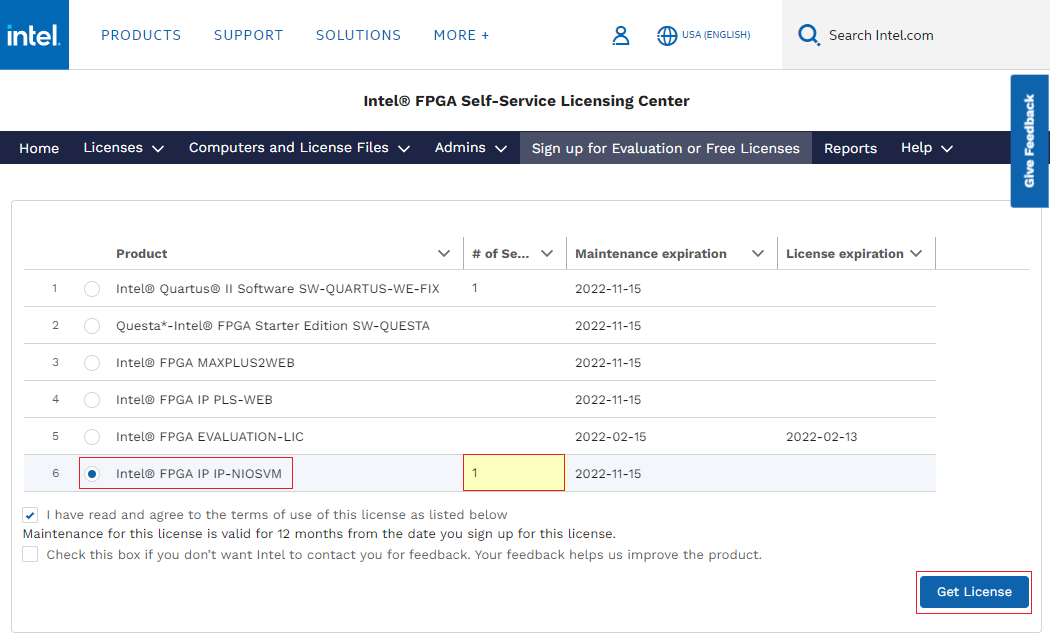

2.2 Nios® V/m embedded processorライセンス取得

Sign Inが完了後、次のような画面が表示されますので、

Intel® FPGA IP IP-NIOSVMを選択し、"# of Seats"に1を入力して、右下の"Get License"をクリックしてください。

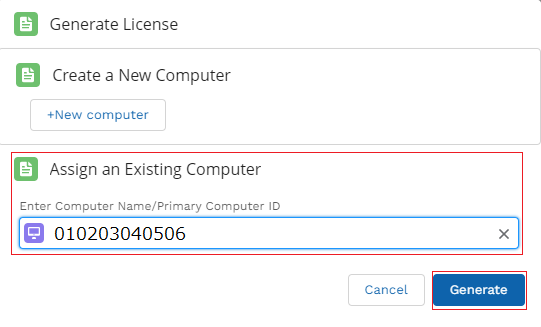

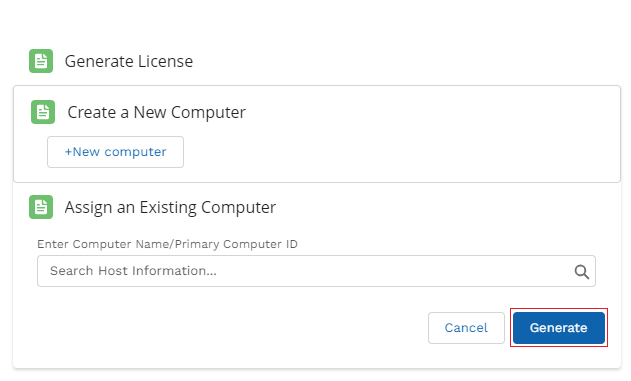

2.3 新規コンピュータ登録

次の画面が表示されますので、

初めてライセンスを取得する方は”Create a New Computer"のを選択し、既に登録済の方は"Assign an Exisiting Computer"を選択し、右下の"Generate"ボタンをクックします。今回は新規でコンピューターを登録し、イーサネットのMACIDをIDとして作成します。

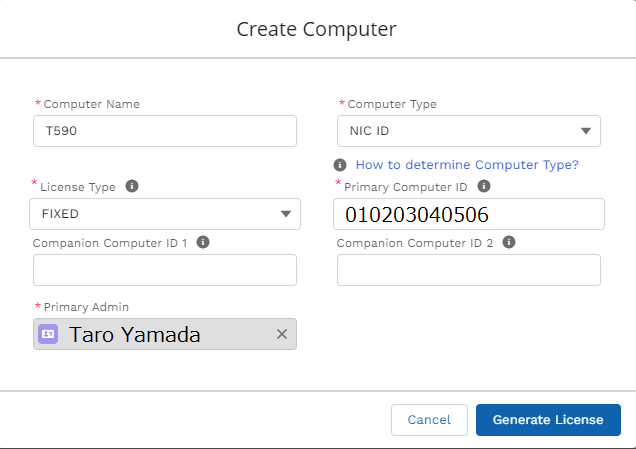

2.4 新規コンピュータ情報入力

次の画面が表示されますので、使用するコンピューターを設定します。

下記の必要な項目を入力して、"Generate License"をクリックしてください。

| Item | Description |

|---|---|

| Computer Name | 任意の名前入力 |

| License Type | FIXEDを選択 |

| Computer Name | NIC IDを選択 |

| Primary Computer ID | PCのイーサネットMACIDを入力 |

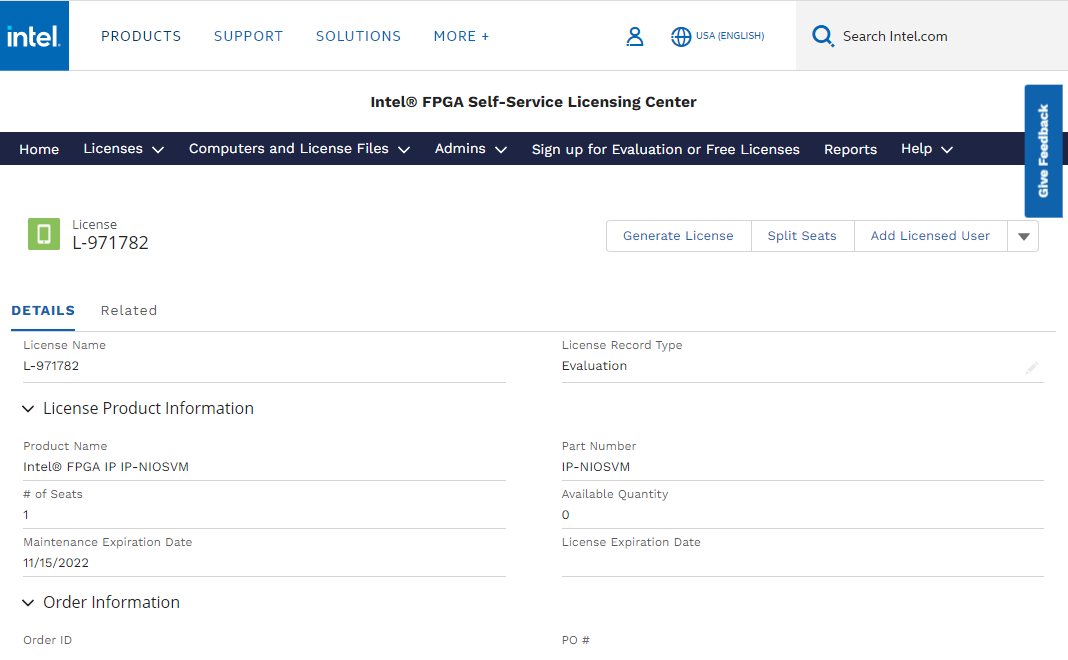

2.5 Nios® V/m embedded processorライセンスファイル確認

生成が成功すると下記の画面が表示され、登録したメールアドレスにライセンスファイルが送付されますの、ファイルを確認してください。

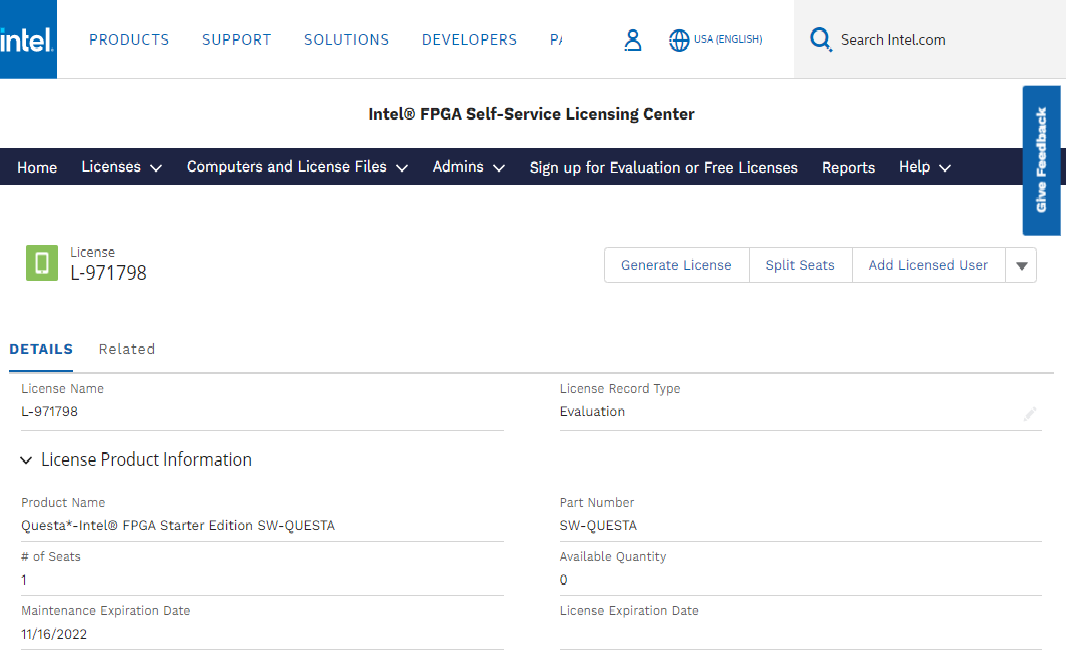

2.6 Questa*-Intel® FPGA Edition Softwareライセンス取得

同じ手順でQuesta*-Intel® FPGA Edition Softwareのラインセスを取得します。既にライセンスをお持ちの方は必要ありませんので次章に進んでください。前回と同じく、Self Service Licensing Centerをクリックします。

Questa*-Intel® FPGA Starter software Edition SW-QUESTAを選択し、"# of Seats"に1を入力して、右下の"Get License"をクリックしてください。

2.7 既存コンピュータへ追加

下記画面が表示されたら、先ほど登録したPCを指定しますので、"Assign an Existing Compture"を選び、MAXIDを入力して、右下の"Generate"ボタンを押します。

2.8 Questa*-Intel® FPGA Edition Softwareライセンスファイルの確認

生成が成功すると次の画面が表示され、登録したメールアドレスにライセンスファイルが送付されます。

これで、ライセンス取得は完了です。

3. インストール

本章では、Intel® Quartus® Prime Softwareのダウンロード、インストール方法、また環境変数の設定について説明します。

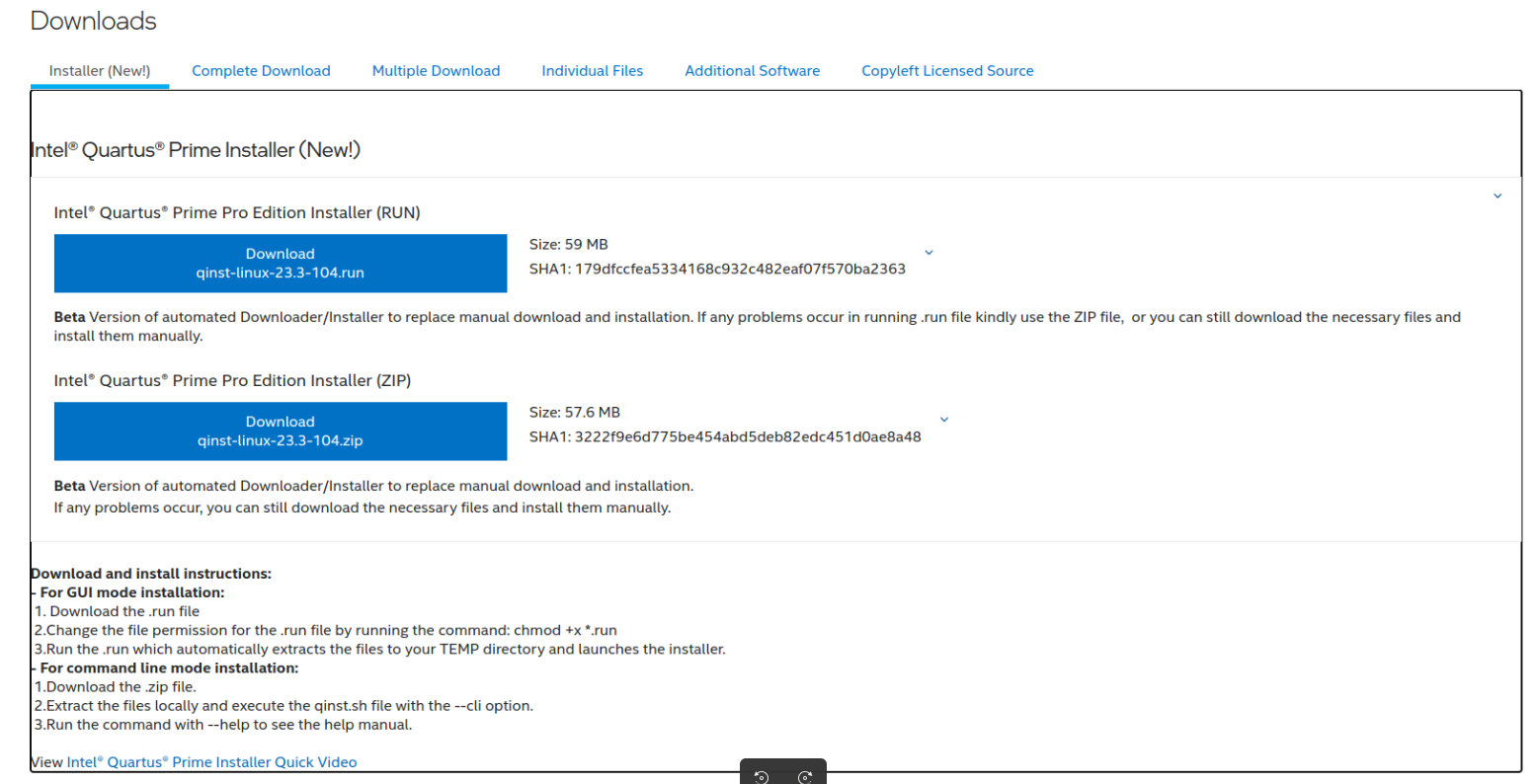

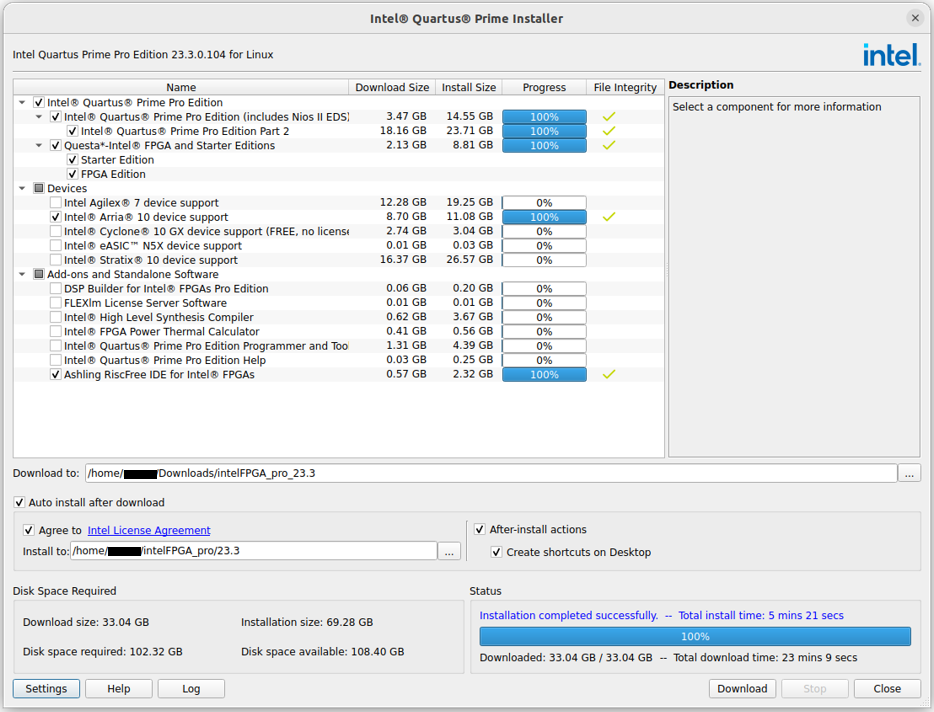

3.1 Intel® Quartus® Prime Pro Edition 23.3インストール

3.1.1 ダウンロード

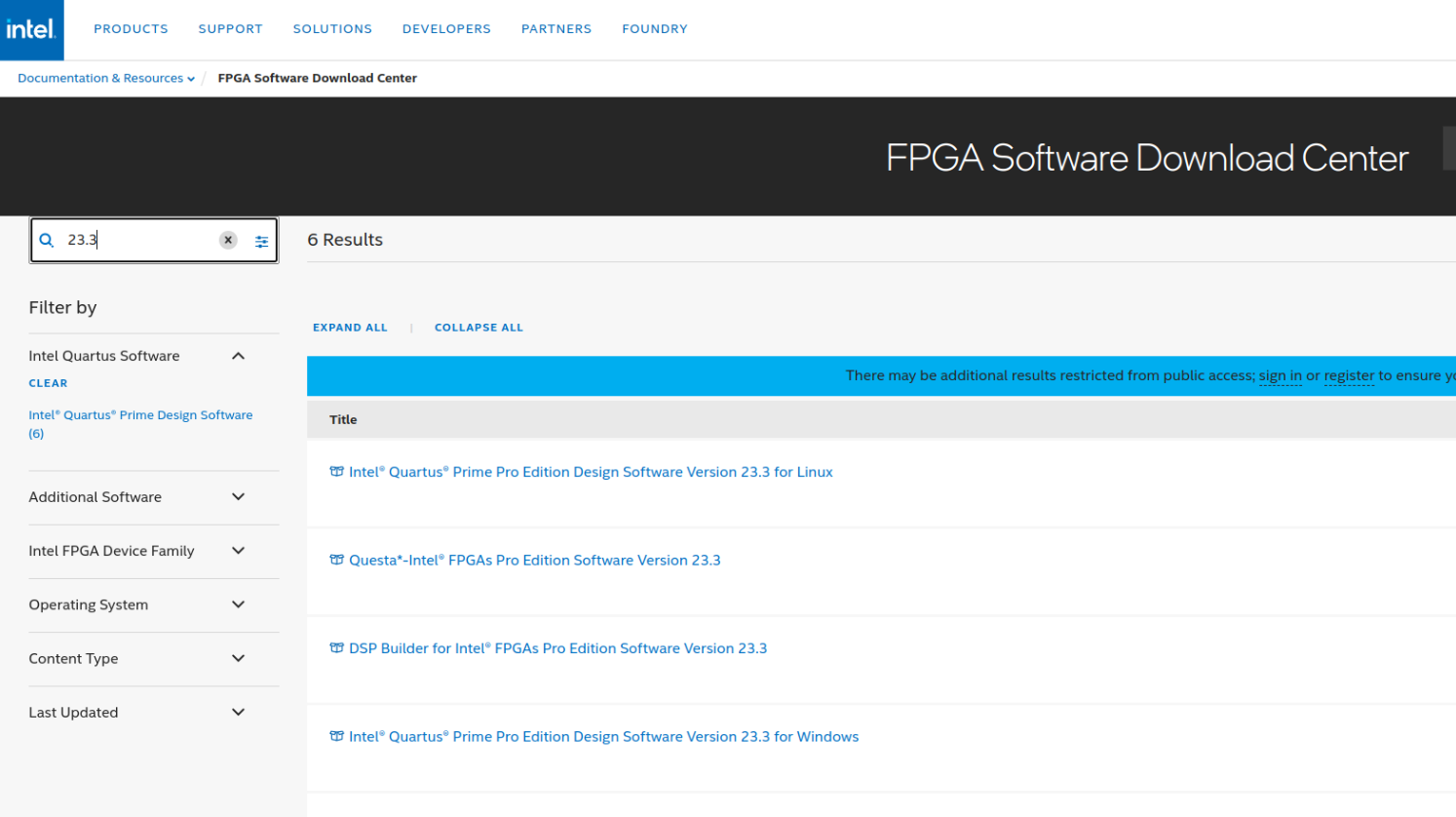

まず、FPGA Software Download Centerをクリックして下記ページに行き、OSの種類に従って、対応するIntel® Quartus® Prime Softwareのバージョンをクリックしてください。今回はLinux版でインストールの説明をします。

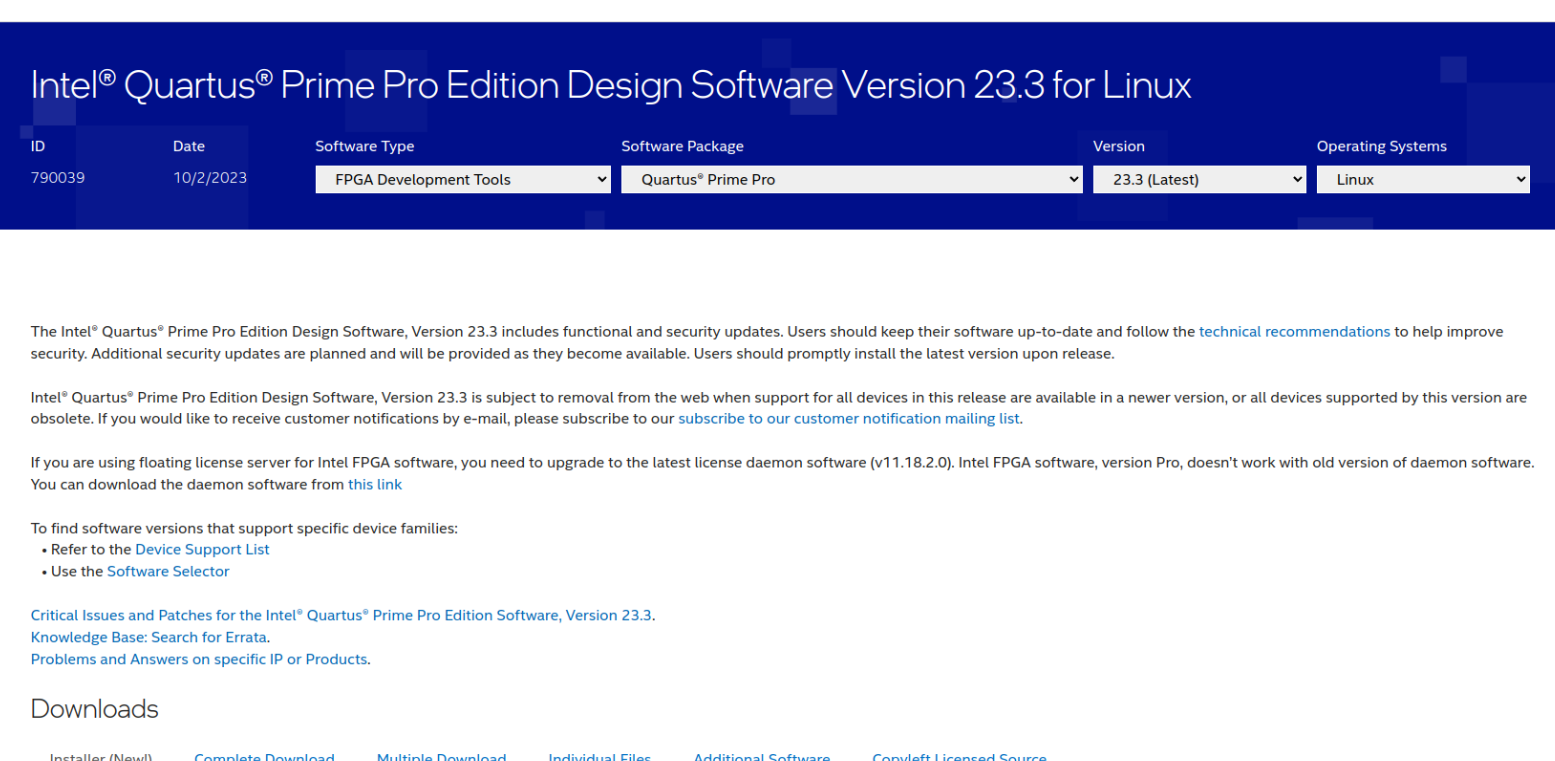

クリックすると下記ページが表示されますので、Versionが23.3になっていることを確認して、下にスクロールしてください。

下記ページよりIntel® Quartus® Prime Pro Edition Installer (RUN)をダウンロードしてください。Windowsの場合はIntel® Quartus® Prime Pro Edition Installer (EXE)をダウンロードしてください。

ダウンロードが完了しましたら、ダウンロード先のディレクトリーで下記コマンドを入力するとインストーラーが起動します。

$ chmod +x *.run

$ ./qinst-linux-23.3-104.run

Windowsの場合はダウンロードしたqint-windows-23.3-104.exeをダブルクリックしてください。

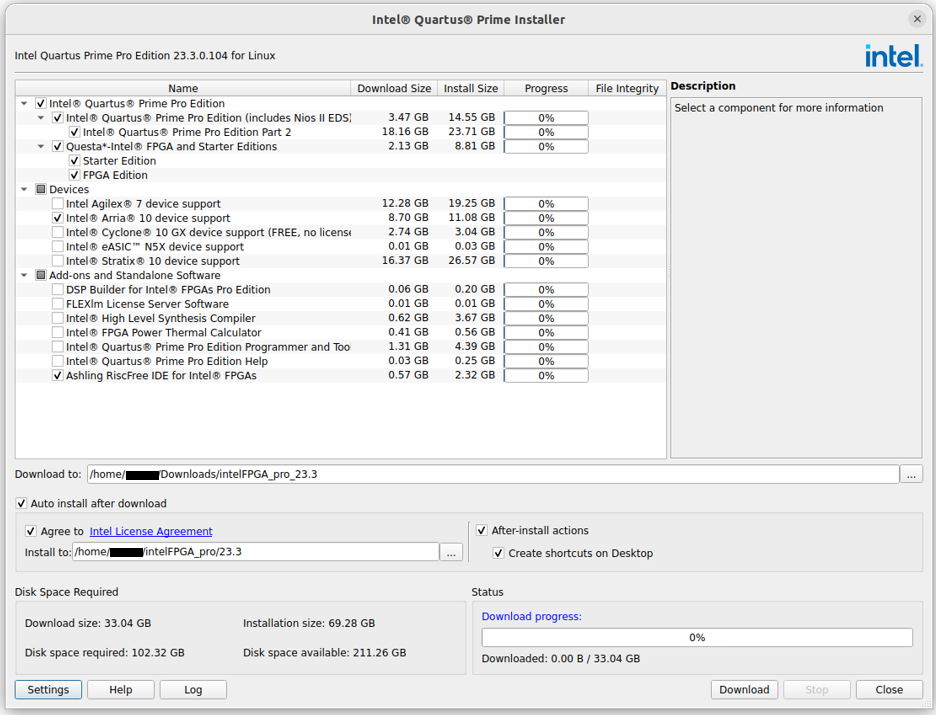

インストーラーが起動したら、

- Intel® Quartus® Prime Pro Edition Part 1 (includes Nios II EDS)

- Intel® Quartus® Prime Pro Edition Part 2

- Questa*-Intel® FPGA and Starter Editions

- Intel® Arria® 10 device support

- Ashling RiscFree IDE for Intel® FPGAs

を選択し、Agree to Intel License Agreementにチェックを入れ、Downloadをクリックします。

ダウンロード先とインストール先を変更したい場合は、この画面で変更してください。

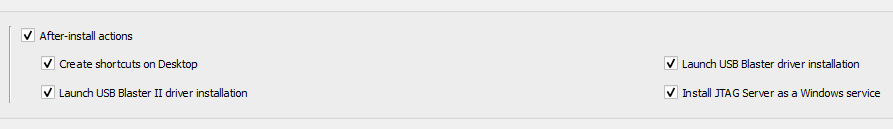

Windowsの場合はAfter-install actionsで

- Launch USB Blaster driver installation

- Launch USB blaster II driver installation

- Install JTAG Server as a Windows service

にチェックが付いていることを確認してください。

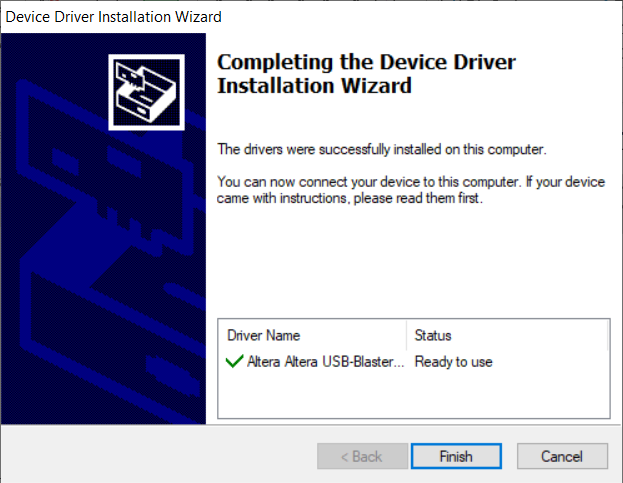

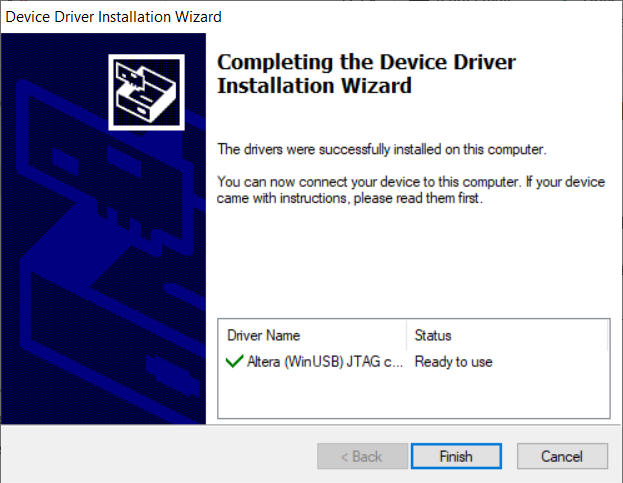

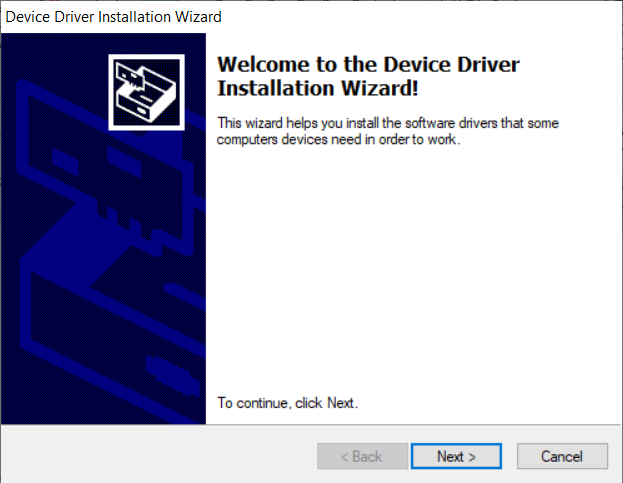

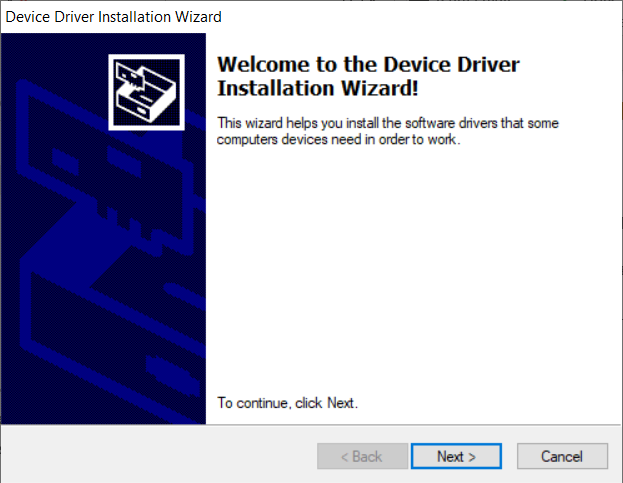

ダウンロード&インストールが進行するとWindowsのみ、Intel® FPGA Download Cable II(旧USB Blaster II)やIntel® FPGA Download Cable(旧USB Blaster)をインストールするためのDevice Driver Installation Wizardが開きます。

FPGAのコンフィグレーションや、Nios® V/m embedded processorのデバッグに必要ですのでインストールしてください。

Linuxの方はIntel® FPGA Download Cable II User Guideの

"1.6. Installing the Intel FPGA Download Cable II Driver on Linux Systems"に従ってください。

Intel® FPGA Download Cable(旧USB Blaster)ドライバーをインストールします。Nextをクリックしてください。

Intel® FPGA Download Cable II(旧USB Blaster II)ドライバーをインストールします。Nextをクリックしてください。

Quartusのインストール完了後の画面です。

以上でIntel® Quartus® Prime Pro Editionのインストールは完了です。

3.2 環境変数の設定

3.2.1 Linux

下記を実行し、ツール類へのパスとライセンスファイルの指定を行ってください。

#!/bin/bash

export QUARTUS_ROOTDIR="$HOME/intelFPGA_pro/23.3/quartus"

export QSYS_ROOTDIR="$QUARTUS_ROOTDIR/../qsys/bin"

export SOPC_KIT_NIOS2="${QUARTUS_ROOTDIR}/../nios2eds"

# Tools

QUARTUS="$QUARTUS_ROOTDIR/bin64"

QSYS="$QSYS_ROOTDIR"

NIOSV="$QUARTUS_ROOTDIR/../niosv/bin"

NIOS2EDS="$QUARTUS_ROOTDIR/../nios2eds/bin"

MAKE="$QUARTUS_ROOTDIR/../riscfree/build_tools/bin"

CMAKE="$QUARTUS_ROOTDIR/../riscfree/build_tools/cmake/bin"

GCC="$QUARTUS_ROOTDIR/../riscfree/toolchain/riscv32-unknown-elf/bin"

if [ -d "$QUARTUS_ROOTDIR/../questa_fe" ]; then

QSIM="$QUARTUS_ROOTDIR/../questa_fe/bin"

elif [ -d "$QUARTUS_ROOTDIR/../questa_fse" ]; then

QSIM="$QUARTUS_ROOTDIR/../questa_fse/bin"

else

echo "Questa not found"

fi

export PATH="$QUARTUS:$QSYS:$NIOSV:$NIOS2EDS:$MAKE:$CMAKE:$GCC:$QSIM:$PATH"

# License files

export LM_LICENSE_FILE="$HOME/license/1-V4ICFB_License.dat"

export MGLS_LICENSE_FILE="$HOME/license/1-V4ICFB_License.dat"

ライセンスに関しては、$HOME/licenseに保存してある1-V4ICFB_License.datを指定してます。

複数のライセンスファイルを指定する場合は、以下の2行で

export LM_LICENSE_FILE="$HOME/license/1-V4ICFB_License.dat"

export MGLS_LICENSE_FILE="$HOME/license/1-V4ICFB_License.dat"

":"で区切ってライセンスファイルを繋げてください。

# Example

export LM_LICENSE_FILE="$HOME/license/1-V4ICFB_License.dat:$HOME/license/XXX_License.dat"

export MGLS_LICENSE_FILE="$HOME/license/1-V4ICFB_License.dat:$HOME/license/XXX_License.dat"

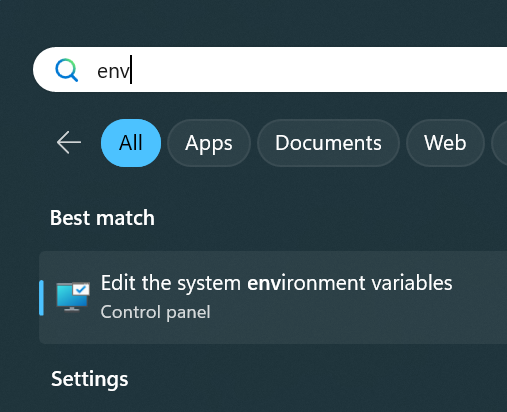

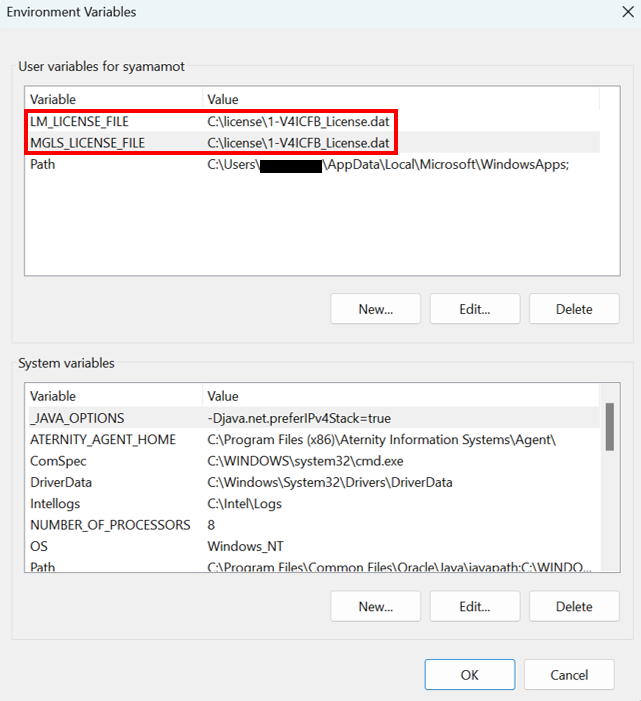

3.2.2 Windows

Windowsの場合はNios V Command Shellを使用するので、ツール類のパスの設定は不要です。

ライセンスの指定のみ行います。

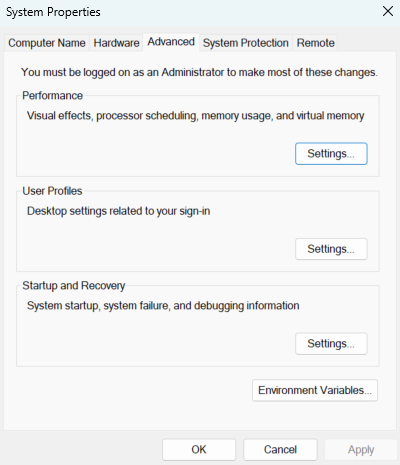

キーボードのWindowsキーを押し、envと入力してください。

そして表示される"Edit the system environment variables"を選択してください。

日本語では"システム環境変数の編集"です。

下記ダイアログが開きますので、"Environment Variables"をクリックしてください。

日本語では"環境変数(N)..."です。

赤枠のユーザー環境変数設定で、LM_LICENSE_FILE, MGLS_LICENSE_FILEへライセンスファイルを指定します。ファイルが複数ある場合は";"で区切って指定してください。

再起動をしたら設定完了です。

4. ハードウエア構築

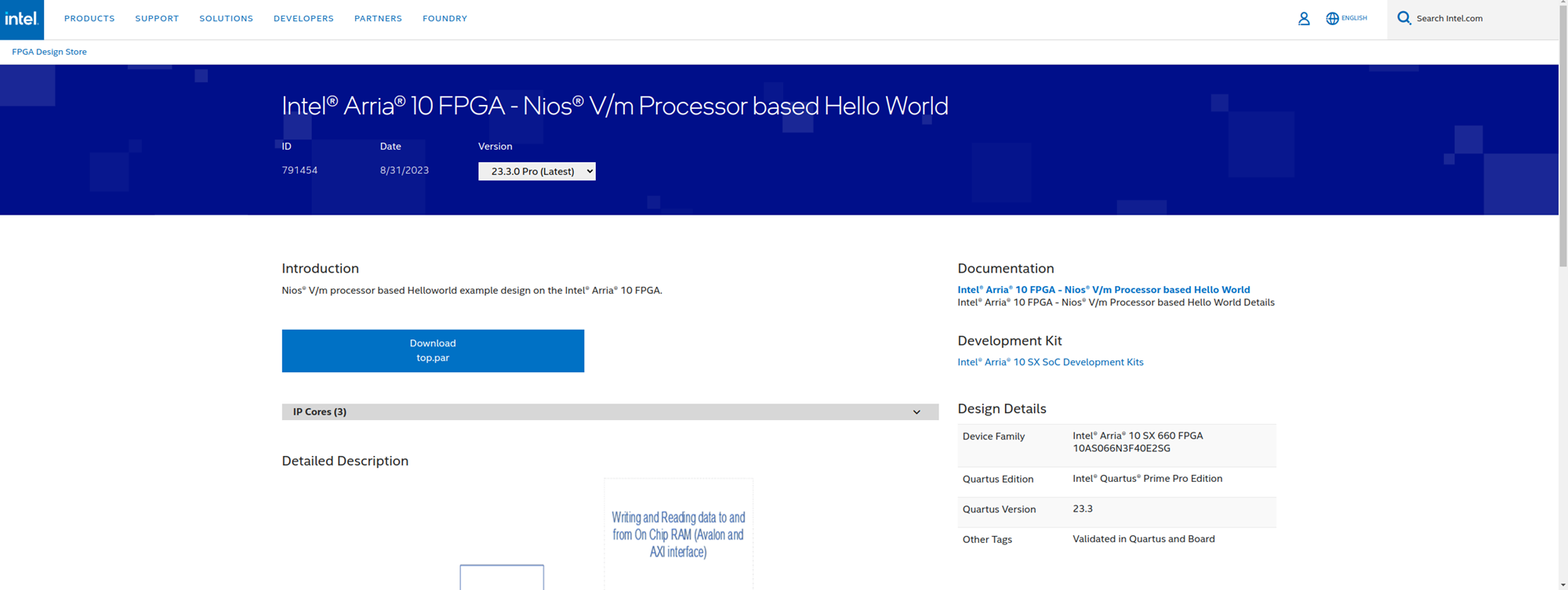

4.1 デザインサンプル&下準備

ここでは、Nios® V/m embedded processorを用いたデザインを構築します。FPGA Design StoreからIntel® Arria® 10 FPGA - Nios® V/m Processor based Hello Worldのversion 23.3をダウンロードしてください。ファイル名はtop.parです。

ダウンロードが完了したら、ワークディレクトリにtop.parをコピーします。

ワークディレクトリが$HOME/wsだとすれば

cp $HOME/Downloads/top.par $HOME/ws

とします。

Windowsの場合はワークディレクトリがC:\wsだとすれば

こちらにドラッグ&ドロップでコピーしてください。

次に、LinuxではTerminalで環境変数のセットを完了させた状態にし、WindowsではスタートメニューのQuartus Prime Pro Edition 23.3.0.104->Nios V Command Shell (Quartus Prime Pro 23.3)を起動します。

$HOME/wsに移動したら以下を実行します。

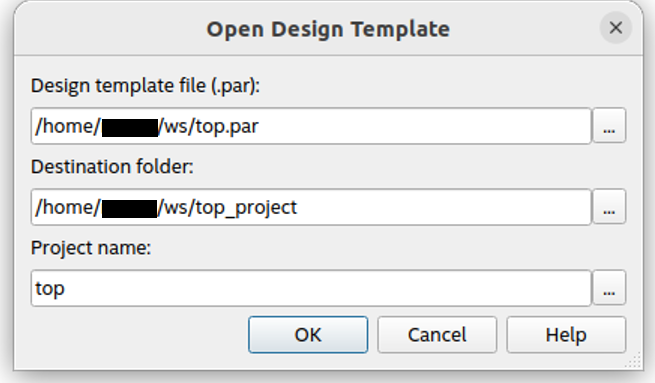

quartus top.par &

Quartusが起動し、Example Designの展開場所を聞かれるので、お好きなワークディレクトリを指定しOKをクリックしてください。

以降、Example Designの展開先としてLinuxでは$HOME/ws/top_project, WindowsではC:/ws/top_projectを指定したとして話を進めます。また、ターミナルのコマンドは全て$HOME/ws/top_projectまたはC:/ws/top_projectから実行することとします。

$HOME/ws/top_project/hw/top.vを見てもらえればわかる通り、本デザインは50MHzのクロック入力1本のみ使用しています。そのため、他のFPGAへの移植も容易です。詳細は4.5 他のFPGAへの移植を参照してください。リセットに関しては、ISSP(In-System Source & Probe)と呼ばれるJTAGより信号を制御するIPを使用して、toggle_issp.tclにより、リセットを行います。詳しくは5.1.6 ISSP (In-System Source & Probe)によりCPUをリセットで説明します。

| File | Description |

|---|---|

| readme.txt | READMEファイル |

| hw/top.qpf | Quartus Project file |

| hw/top.qsf | Quartus Settings file |

| hw/top.sdc | Synopsys Design Constraints file |

| hw/top.v | Design TOP RTL file |

| scripts/create_qsys.tcl | Platform Designer作成スクリプト |

| scripts/toggle_issp.tcl | Reset実行スクリプト |

| sw/app_hal/hello.c | HAL用Hello Worldメインファイル |

| sw/app_ucosii/hello_ucosii.c | uC/OS-II用Hello Worldメインファイル |

| sw/app_freertos/hello_freertos.c | FreeRTOS™用Hello Worldメインファイル |

大前提として、今ダウンロード&展開してきたExample Designはready to testの状態、すなわちNios® V/m embedded processorの実行に必要なファイルやバイナリーは最初から全て揃っています。FPGAコンフィグレーション用ファイルは

$HOME/ws/top_project/ready_to_test/top.sof,

Nios® V/m embedded processor用アプリケーションのELFファイルは

$HOME/ws/top_project/ready_to_test/app_hal.elf, $HOME/ws/top_project/ready_to_test/app_ucosii.elf, $HOME/ws/top_project/ready_to_test/app_freertos.elf

として用意されています。実機での動作確認のみ行いたい場合はこれらを使用してください。

以下では、自分でハードウェアデザインのコンパイルおよびNios® V/m embedded processor用のアプリケーションのビルドを行う際の手順を説明します。

4.2 Platform Designerデザイン確認

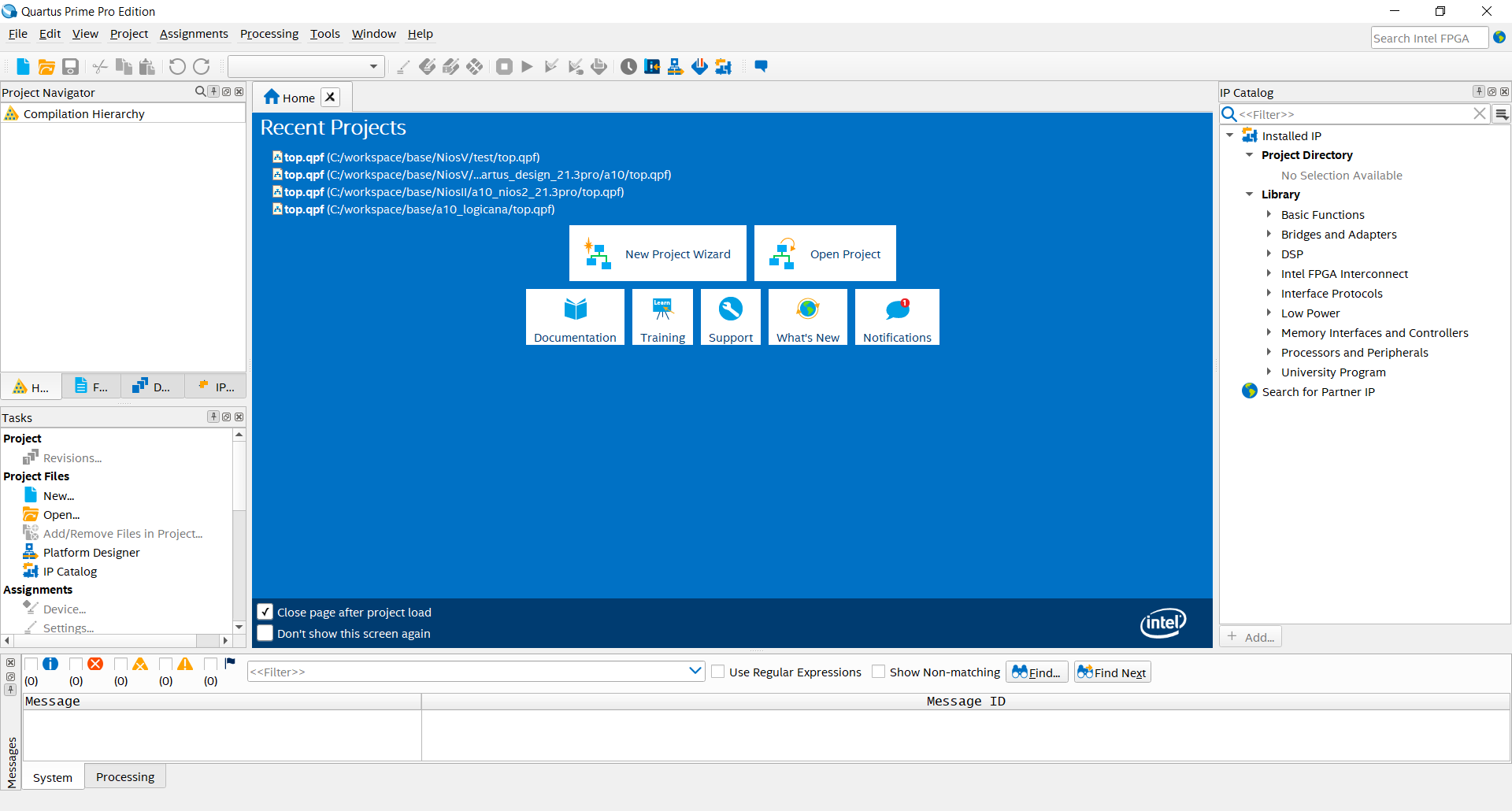

実際にPlatform DesignerのデザインをGUIで確認してみましょう。Platform Deisgnerの起動方法は2つあり、一つ目は、Intel® Quartus® Primeソフトウェアを起動し、Platfrom Designerを起動する方法です。もう一つはTerminalよりコマンドで起動する方法です。

4.2.1 Intel® Quartus® PrimeソフトウェアよりPlatform Designer起動

1)Terminal上で以下を実行するとQuartusが起動します。

quartus &

Windowsの場合はスタートメニューからQuartus Prime Pro Edition 23.3.0.104->Quartus (Quartus Prime Pro 23.3)を選択してQuartusを起動してもOKです。

2)Fileメニューより"Open Project..."を選択し、$HOME/ws/top_project/hw/top.qpfを指定し、"Open"をクリックします。

3)Toolsメニューより"Platform Designer"を選択します。

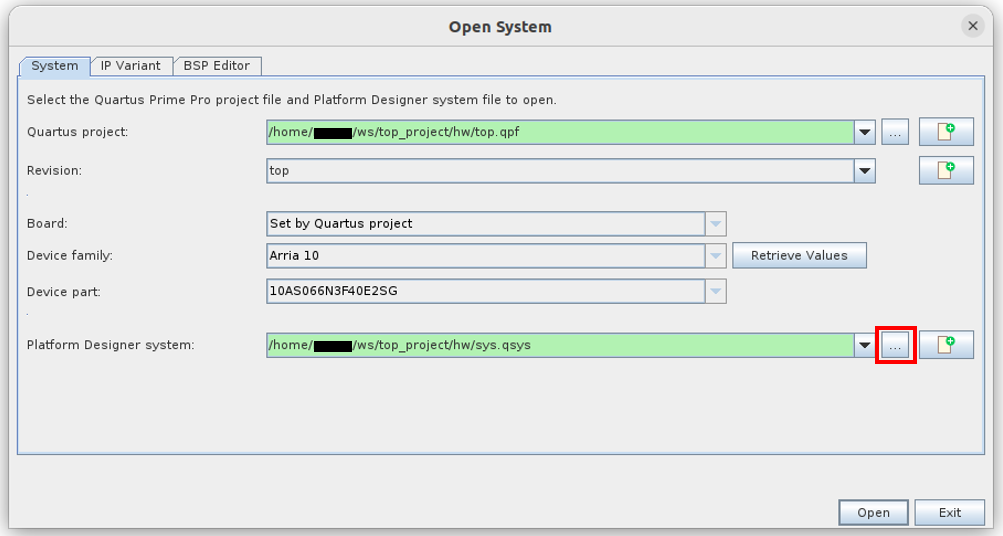

4)下記の"Open System"ダイアログが開いたら、赤枠をクリックして、$HOME/ws/top_project/hw/sys.qsysファイルを指定してください。

5)Openをクリックします。

4.2.2 TerminalよりPlatform Designer起動

$HOME/ws/top_projectに移動し下記コマンドを入力します。

qsys-edit --quartus-project=hw/top.qpf hw/sys.qsys

4.2.3 Platform Designerデザイン

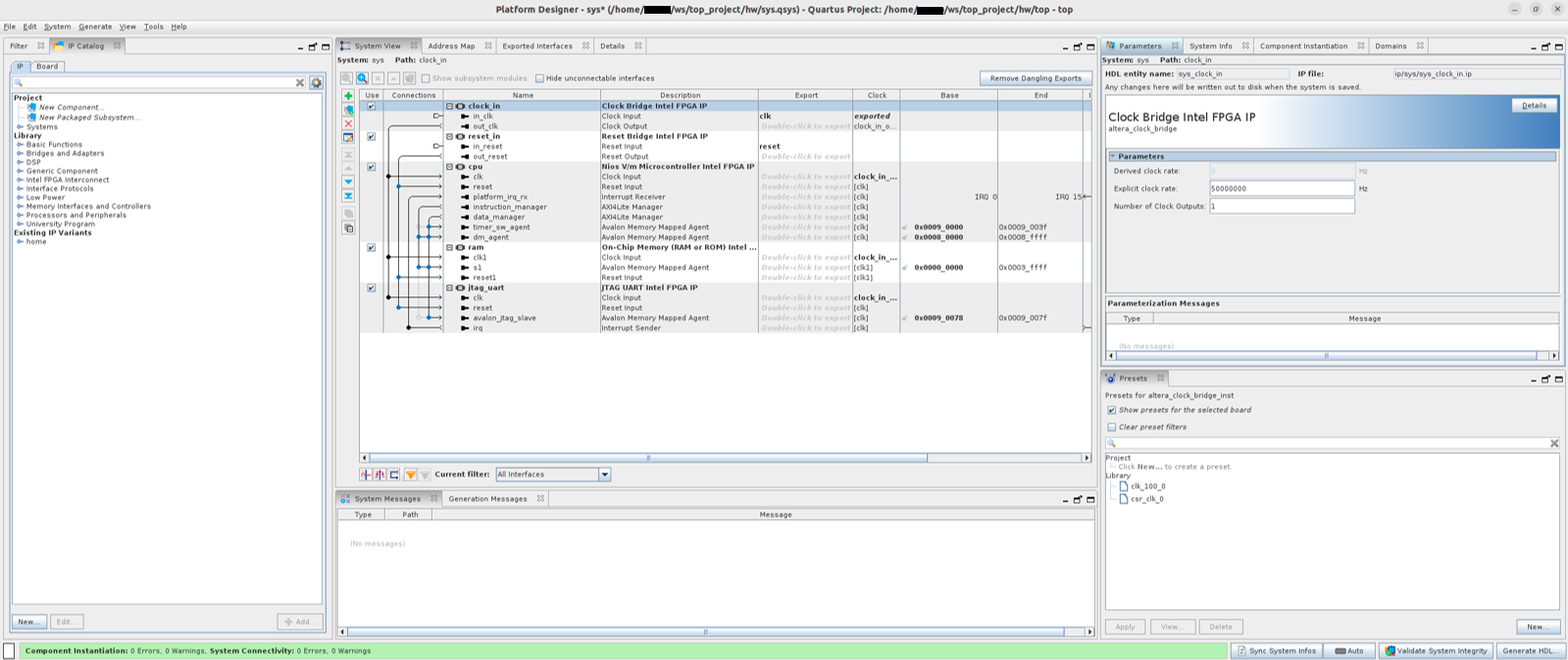

ここでは、デザイン構成と各IPの設定を確認します。下記がデザインの全体構成です。

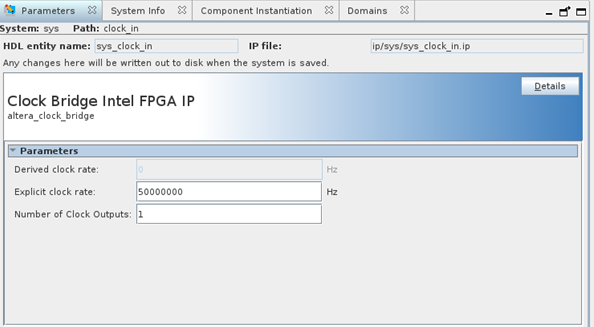

4.2.3.1 クロック

クロック入力IPの設定画面です。入力クロックが異なるはこの値を変更します。変更した場合はtop.sdcのクロック周期(周期はnsで指定)も併せて変更します。

IPの詳細は7.1.1. Clock Bridge Intel® FPGA IPを参照してください。

4.2.3.2 リセット

リセット入力IPの設定画面です。

IPの詳細は6.6.3. Reset Bridgeを参照してください。

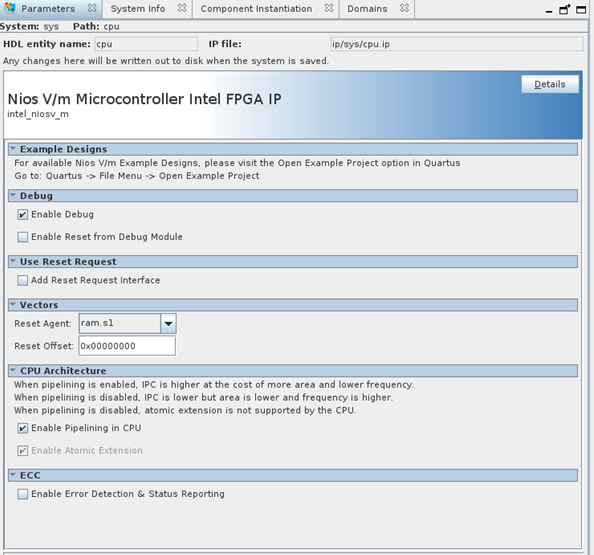

4.2.3.3 Nios® V/m embedded processor

Nios® V/m embedded processor IPの設定画面です。

各パラメーターに関しては以下を参照してください。

2.1.1.2.1. Debug Tab

2.1.1.2.2. Use Reset Request Tab

2.1.1.2.3. Vectors Tab

2.1.1.2.4. CPU Architecture

2.1.1.2.5. ECC Tab

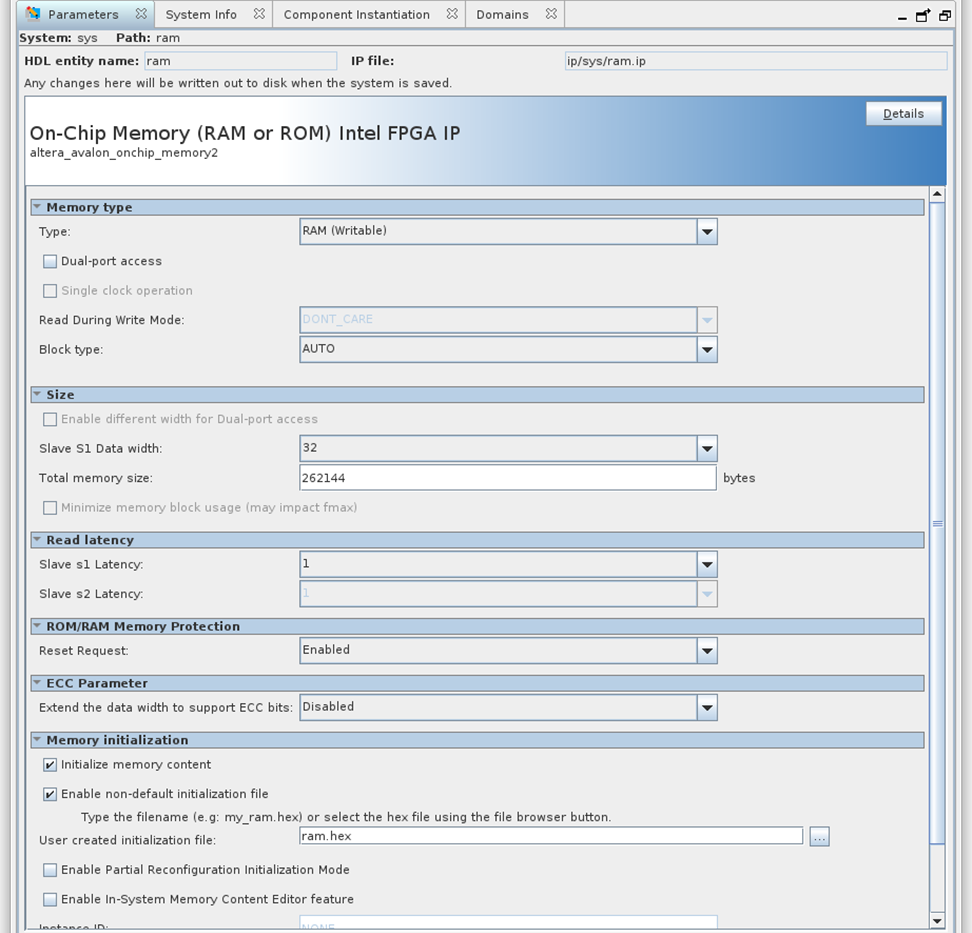

4.2.3.4 内蔵RAM

各パラメーターに関しては以下を参照してください。

25.2.1. Memory Type

25.2.2. Size

25.2.3. Read Latency

25.2.4. ROM/RAM Memory Protection

25.2.5. ECC Parameter

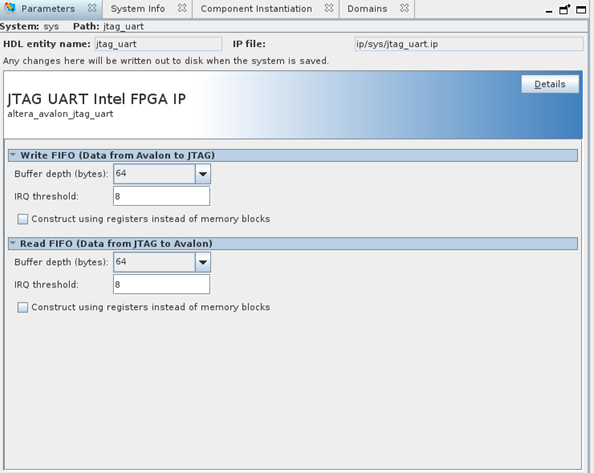

4.2.3.5 JTAG UART

各パラメーターに関しては以下を参照してください。

12.3.1.1. Write FIFO Settings

12.3.1.2. Read FIFO Settings

確認しましたら、Platform Designerは閉じてください。

4.3 デザインコンパイル

次にTerminalで下記コマンドを実行するとデザインのコンパイルが始まります。

quartus_sh --flow compile hw/top

出力

Info: *******************************************************************

Info: Running Quartus Prime Shell

Info: Version 23.3.0 Build 104 09/20/2023 SC Pro Edition

Info: Copyright (C) 2023 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and any partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel FPGA IP License Agreement, or other applicable license

Info: agreement, including, without limitation, that your use is for

Info: the sole purpose of programming logic devices manufactured by

Info: Intel and sold by Intel or its authorized distributors. Please

Info: refer to the Intel FPGA Software License Subscription Agreements

Info: on the Quartus Prime software download page.

Info: Processing started: Mon Nov 27 17:16:26 2023

Info: System process ID: 64166

Info: Command: quartus_sh --flow compile hw/top

Info: Quartus(args): compile hw/top

Info: The application is running in 'DNI' mode.

Info: Project Name = /home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/hw/top

Info: Revision Name = top

Info: Run task: IP Generation

Info: *******************************************************************

Info: Running Quartus Prime IP Generation Tool

Info: Version 23.3.0 Build 104 09/20/2023 SC Pro Edition

Info: Processing started: Mon Nov 27 17:16:27 2023

Info: System process ID: 64187

Info: Command: quartus_ipgenerate --dni top -c top --run_default_mode_op

Info: The application is running in 'DNI' mode.

.....

.....

.....

Info: Command: quartus_asm --read_settings_files=on --write_settings_files=off top -c top

Info: The application is running in 'DNI' mode.

Info (16677): Loading final database.

Info (16734): Loading "final" snapshot for partition "root_partition".

Info (16734): Loading "final" snapshot for partition "auto_fab_0".

Info (16678): Successfully loaded final database: elapsed time is 00:00:02.

Info (22889): This design was generated using the DNI flow.

Info: Quartus Prime Assembler was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 5103 megabytes

Info: Processing ended: Mon Nov 27 17:18:49 2023

Info: Elapsed time: 00:00:16

Info: System process ID: 66849

Info (21793): Quartus Prime Full Compilation was successful. 0 errors, 35 warnings

Info (23030): Evaluation of Tcl script /home/ubuntu_usr/intelFPGA_pro/23.3/quartus/common/tcl/internal/qsh_flowengine.tcl was successful

Info: Quartus Prime Shell was successful. 0 errors, 35 warnings

Info: Peak virtual memory: 1034 megabytes

Info: Processing ended: Mon Nov 27 17:18:51 2023

Info: Elapsed time: 00:02:25

Info: System process ID: 64166

$HOME/ws/top_project/hw/top.qsfの10行目を見てみると

set_global_assignment -name PROJECT_OUTPUT_DIRECTORY output_files

このように書いてあります。これはデザインコンパイルの生成物をどこに出力するかを指定しており、

$HOME/ws/top_project/hw/output_filesに.sofが生成されます。

4.4 FPGAのコンフィグレーション

次のコマンドを実行して、FPGAをコンフィグレーションします。LinuxとWindowsとではコマンドが微妙に異なるので注意してください。

Linux

quartus_pgm -c 1 -m JTAG -o p\;hw/output_files/top.sof@1

出力

Info: *******************************************************************

Info: Running Quartus Prime Programmer

Info: Version 23.3.0 Build 104 09/20/2023 SC Pro Edition

Info: Copyright (C) 2023 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and any partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel FPGA IP License Agreement, or other applicable license

Info: agreement, including, without limitation, that your use is for

Info: the sole purpose of programming logic devices manufactured by

Info: Intel and sold by Intel or its authorized distributors. Please

Info: refer to the Intel FPGA Software License Subscription Agreements

Info: on the Quartus Prime software download page.

Info: Processing started: Mon Nov 27 17:20:19 2023

Info: System process ID: 67118

Info: Command: quartus_pgm -c 1 -m JTAG -o p;hw/output_files/top.sof@1

Info: The application is running in 'DNI' mode.

Info (213045): Using programming cable "USB-BlasterII [1-6.1]"

Info (213011): Using programming file hw/output_files/top.sof with checksum 0x1D2C05B0 for device 10AS066N3F40@1

Info (209060): Started Programmer operation at Mon Nov 27 17:20:21 2023

Info (209016): Configuring device index 1

Info (209017): Device 1 contains JTAG ID code 0x02E050DD

Info (209007): Configuration succeeded -- 1 device(s) configured

Info (209011): Successfully performed operation(s)

Info (209061): Ended Programmer operation at Mon Nov 27 17:20:32 2023

Info: Quartus Prime Programmer was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 1917 megabytes

Info: Processing ended: Mon Nov 27 17:20:32 2023

Info: Elapsed time: 00:00:13

Info: System process ID: 67118

Windows

quartus_pgm -c 1 -m JTAG -o p;hw/output_files/top.sof@1

出力

Info: *******************************************************************

Info: Running Quartus Prime Programmer

Info: Version 23.3.0 Build 104 09/20/2023 SC Pro Edition

Info: Copyright (C) 2023 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and any partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel FPGA IP License Agreement, or other applicable license

Info: agreement, including, without limitation, that your use is for

Info: the sole purpose of programming logic devices manufactured by

Info: Intel and sold by Intel or its authorized distributors. Please

Info: refer to the Intel FPGA Software License Subscription Agreements

Info: on the Quartus Prime software download page.

Info: Processing started: Tue Nov 28 23:34:47 2023

Info: System process ID: 26872

Info: Command: quartus_pgm -c 1 -m JTAG -o p;hw/output_files/top.sof@1

Info: The application is running in 'DNI' mode.

Info (213045): Using programming cable "USB-BlasterII [USB-1]"

Info (213011): Using programming file hw/output_files/top.sof with checksum 0x1D2C388C for device 10AS066N3F40@1

Info (209060): Started Programmer operation at Tue Nov 28 23:34:53 2023

Info (209016): Configuring device index 1

Info (209017): Device 1 contains JTAG ID code 0x02E050DD

Info (209007): Configuration succeeded -- 1 device(s) configured

Info (209011): Successfully performed operation(s)

Info (209061): Ended Programmer operation at Tue Nov 28 23:35:04 2023

Info: Quartus Prime Programmer was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 1296 megabytes

Info: Processing ended: Tue Nov 28 23:35:04 2023

Info: Elapsed time: 00:00:17

Info: System process ID: 26872

4.5 他のFPGAへの移植

本デザインを他のFPGAボードへ移植する場合は、デバイスと、クロックピンが主な変更点です。

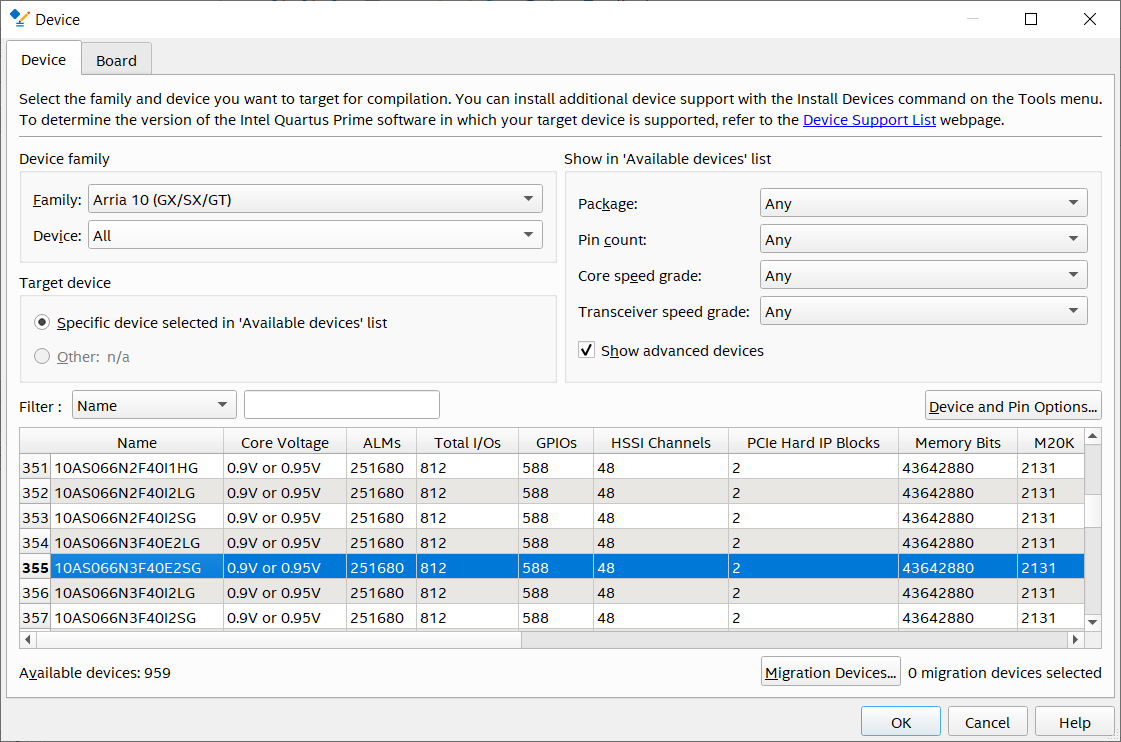

1)Assigmentsメニューより"Device..."を選択すると、下記ダイアログが表示されますので、使用するデバイスを指定してください。

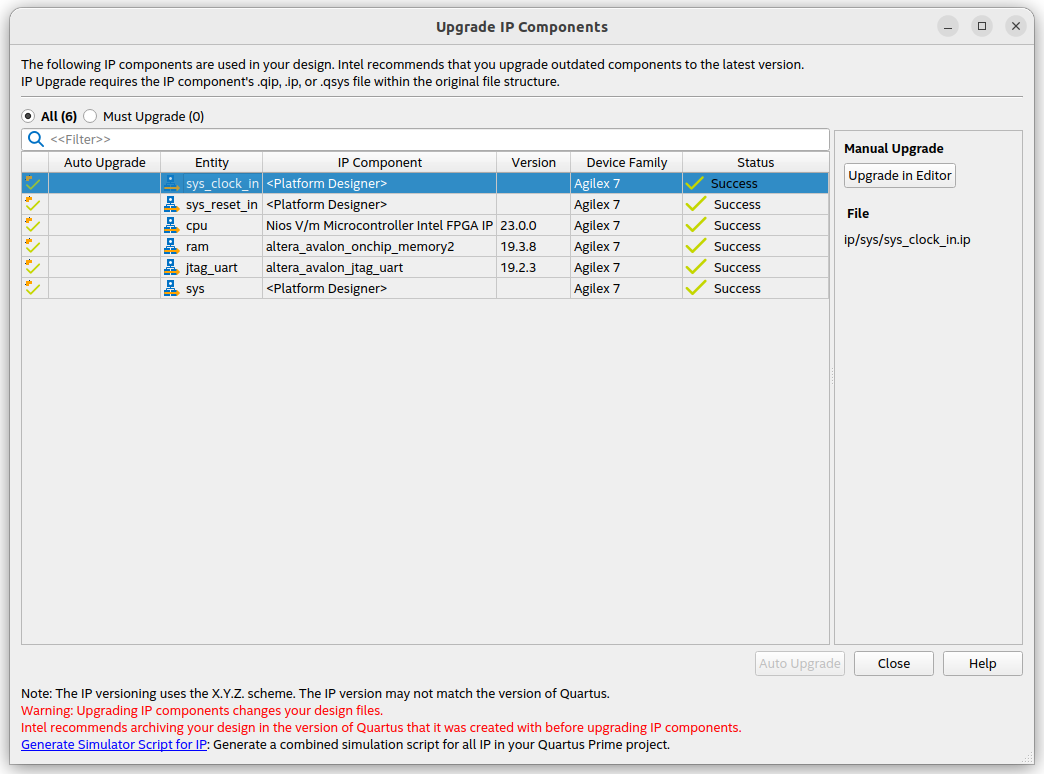

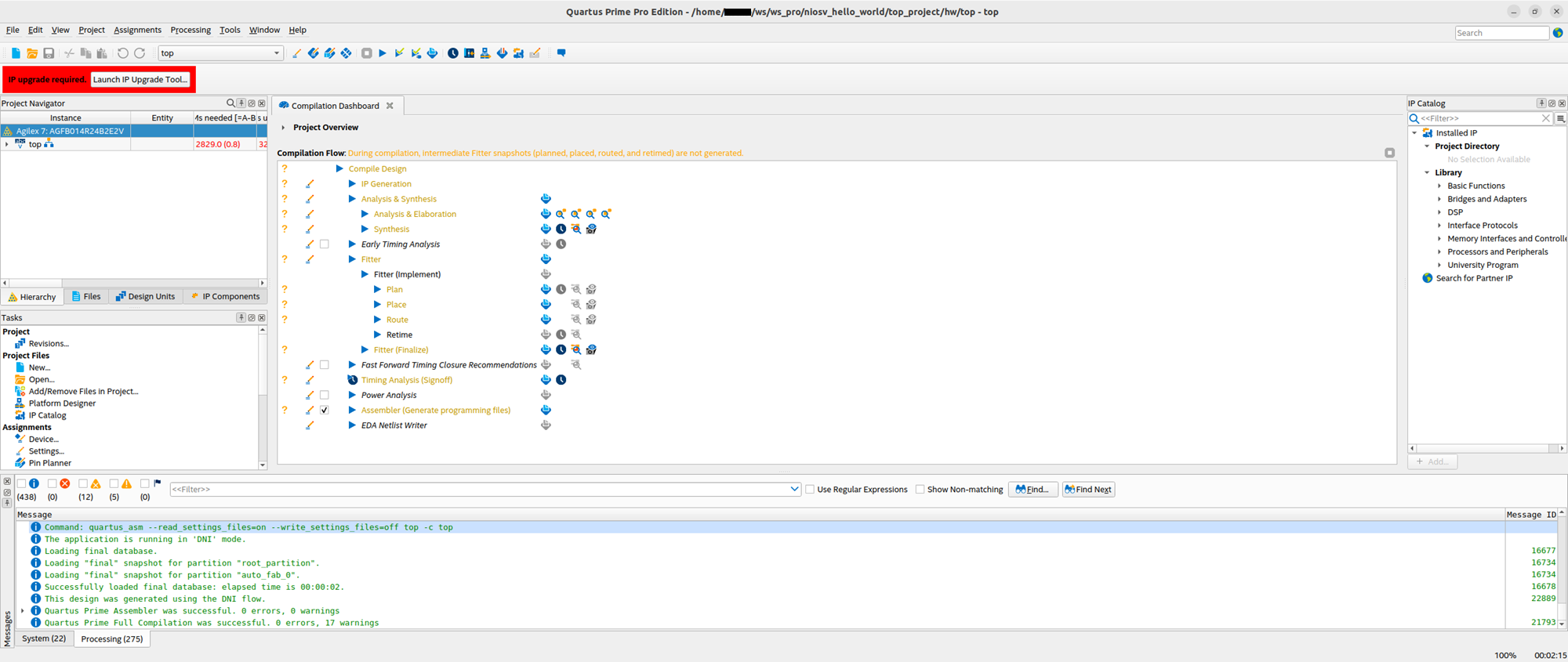

2)デバイスを変更したら、Quartusの左上に"IP update required"と赤く表示されるので、"Launch IP Upgrade Tool..."をクリックしてください。

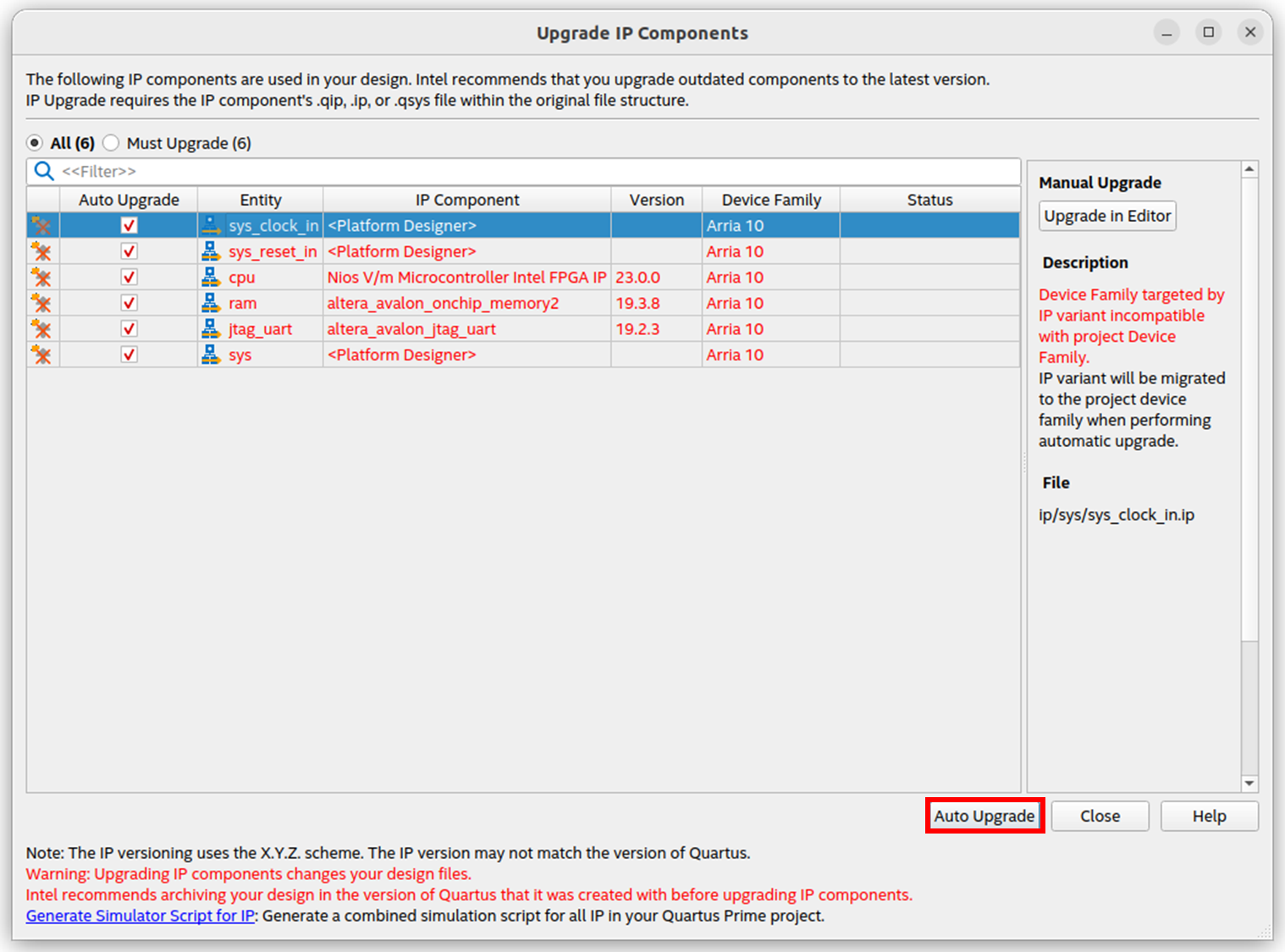

3)下記ダイアログが表示されますので、"Auto Upgrade"をクリックしてIPを更新してください。

4)IPの更新が完了し、Statusの列にSuccessと表示されたら閉じてください。

5)Processingメニューより、”Start Compilation..."を選択し、コンパイルを実行します。クロックピンの設定を行っていないので、Fitterステージでエラーがでるかもしれませんが無視してください。

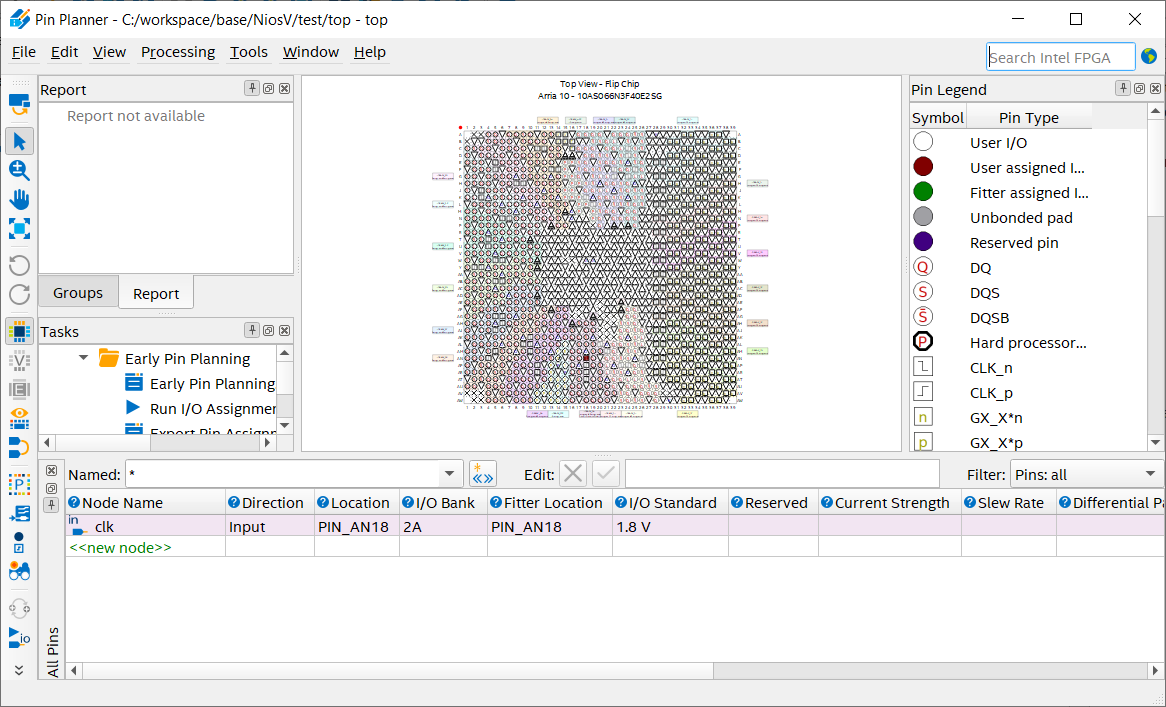

6)Assigmentsメニューより"Pin Planner..."を選択すると、下記ダイアログは表示されますので、クロックピンのLocationを更新します。併せてI/O Standardも更新してください。

4)Processingメニューより、”Start Compilation..."を選択し、コンパイルを再実行します。今回はエラーが無いことを確認してください。

5. ソフトウエア構築&実行

BSPの種類は現在hal, ucosii, freertosの3つが指定可能です。各々BSPの生成からビルド、実行までの手順をご紹介します。

5.1 HAL編

5.1.1 Board Support Package(BSP)生成

BSP生成コマンドの--typeというオプションでhalを指定します。下記コマンドを入力してください。

niosv-bsp -c --quartus-project=hw/top.qpf --qsys=hw/sys.qsys --type=hal sw/bsp_hal/settings.bsp

2023.11.27.17:21:26 Info: Searching for BSP components with category: os_software_element

2023.11.27.17:21:27 Info: Creating BSP settings.

2023.11.27.17:21:27 Info: Searching for BSP components with category: driver_element

2023.11.27.17:21:27 Info: Searching for BSP components with category: software_package_element

2023.11.27.17:21:27 Info: Loading drivers from ensemble report.

2023.11.27.17:21:27 Info: Finished loading drivers from ensemble report.

2023.11.27.17:21:27 Info: Evaluating default script "/home/ubuntu_usr/intelFPGA_pro/23.3/quartus/../niosv/scripts/bsp-defaults/bsp-set-defaults.tcl".

2023.11.27.17:21:27 Info: Tcl message: "STDIO character device is jtag_uart"

2023.11.27.17:21:27 Info: Tcl message: "System timer device is cpu"

2023.11.27.17:21:27 Info: Tcl message: "Default linker sections mapped to ram"

2023.11.27.17:21:27 Info: Tcl message: "No bootloader located at the reset address."

2023.11.27.17:21:27 Info: Tcl message: "Application ELF allowed to contain code at the reset address."

2023.11.27.17:21:27 Info: Tcl message: "The alt_load() facility is enabled."

2023.11.27.17:21:27 Info: Tcl message: "The .rwdata section is copied into RAM by alt_load()."

2023.11.27.17:21:28 Info: Saving BSP settings file.

2023.11.27.17:21:28 Info: Default memory regions will not be persisted in BSP Settings File.

2023.11.27.17:21:28 Info: Generated file "/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/bsp_hal/settings.bsp"

2023.11.27.17:21:28 Info: Generating BSP files in "/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/bsp_hal"

2023.11.27.17:21:28 Info: Default memory regions will not be persisted in BSP Settings File.

2023.11.27.17:21:28 Info: Generated file "/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/bsp_hal/settings.bsp"

2023.11.27.17:21:28 Info: Finished generating BSP files. Total time taken = 2 seconds

5.1.2 CMafileLists.txt生成

下記コマンドを実行して、アプリケーションのコンパイルに必要なCMafileLists.txtを生成させます。このコマンドを実行するにあたり、--srcsで指定したパスにソースファイルが無い場合エラーになります。

niosv-app --bsp-dir=sw/bsp_hal --app-dir=sw/app_hal --srcs=sw/app_hal --elf-name=hello.elf

出力

2023.11.27.17:23:52 Info: Elf name is set to "hello.elf".

2023.11.27.17:23:52 Info: Source file "hello.c" added from directory "sw/app_hal".

2023.11.27.17:23:52 Info: "sw/app_hal/CMakeLists.txt" was generated.

5.1.3 MakeFile生成

下記コマンドを実行して、CMakeLists.txtよりMakeFileを生成します。今回はビルドディレクトリとして既存のsw/app_hal/buildを指定するので、まずsw/app_hal/build/CMakeCache.txtを削除する必要があります。

rm sw/app_hal/build/CMakeCache.txt

次にMakeFileを生成します。

cmake -S sw/app_hal -G "Unix Makefiles" -B sw/app_hal/build

出力

-- Defaulting build type to Debug.

-- The ASM compiler identification is GNU

-- Found assembler: /home/ubuntu_usr/intelFPGA_pro/23.3/riscfree/toolchain/riscv32-unknown-elf/bin/riscv32-unknown-elf-gcc

-- The C compiler identification is GNU 12.1.0

-- Detecting C compiler ABI info

-- Detecting C compiler ABI info - done

-- Check for working C compiler: /home/ubuntu_usr/intelFPGA_pro/23.3/riscfree/toolchain/riscv32-unknown-elf/bin/riscv32-unknown-elf-gcc - skipped

-- Detecting C compile features

-- Detecting C compile features - done

-- The CXX compiler identification is GNU 12.1.0

-- Detecting CXX compiler ABI info

-- Detecting CXX compiler ABI info - done

-- Check for working CXX compiler: /home/ubuntu_usr/intelFPGA_pro/23.3/riscfree/toolchain/riscv32-unknown-elf/bin/riscv32-unknown-elf-g++ - skipped

-- Detecting CXX compile features

-- Detecting CXX compile features - done

-- Configuring done (0.4s)

-- Generating done (0.0s)

-- Build files have been written to: /home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/app_hal/build

5.1.4 hello.elf生成

下記コマンドを実行して、hello.elfを生成します。

make -C sw/app_hal/build

出力

make: Entering directory '/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/app_hal/build'

[ 1%] Building ASM object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_log_macro.S.obj

[ 2%] Building ASM object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_mcount.S.obj

[ 3%] Building ASM object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/crt0.S.obj

[ 4%] Building ASM object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/machine_trap.S.obj

[ 5%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_alarm_start.c.obj

[ 6%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_busy_sleep.c.obj

[ 7%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_close.c.obj

[ 8%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_dcache_flush.c.obj

[ 9%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_dcache_flush_all.c.obj

[ 10%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_dcache_flush_no_writeback.c.obj

[ 12%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_dev.c.obj

[ 13%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_dev_llist_insert.c.obj

[ 14%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_dma_rxchan_open.c.obj

[ 15%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_dma_txchan_open.c.obj

[ 16%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_do_ctors.c.obj

[ 17%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_do_dtors.c.obj

[ 18%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_env_lock.c.obj

[ 19%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_environ.c.obj

[ 20%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_errno.c.obj

[ 21%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_execve.c.obj

[ 23%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_exit.c.obj

[ 24%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_fcntl.c.obj

[ 25%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_fd_lock.c.obj

[ 26%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_fd_unlock.c.obj

[ 27%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_find_dev.c.obj

[ 28%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_find_file.c.obj

[ 29%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_flash_dev.c.obj

[ 30%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_fork.c.obj

[ 31%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_fs_reg.c.obj

[ 32%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_fstat.c.obj

[ 34%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_get_fd.c.obj

[ 35%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_getchar.c.obj

[ 36%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_getpid.c.obj

[ 37%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_gettod.c.obj

[ 38%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_gmon.c.obj

[ 39%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_icache_flush.c.obj

[ 40%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_icache_flush_all.c.obj

[ 41%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_iic.c.obj

[ 42%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_iic_isr_register.c.obj

[ 43%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_instruction_exception_register.c.obj

[ 45%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_io_redirect.c.obj

[ 46%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_ioctl.c.obj

[ 47%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_irq_handler.c.obj

[ 48%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_isatty.c.obj

[ 49%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_kill.c.obj

[ 50%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_link.c.obj

[ 51%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_load.c.obj

[ 52%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_log_printf.c.obj

[ 53%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_lseek.c.obj

[ 54%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_main.c.obj

[ 56%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_malloc_lock.c.obj

[ 57%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_open.c.obj

[ 58%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_printf.c.obj

[ 59%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_putchar.c.obj

[ 60%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_putcharbuf.c.obj

[ 61%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_putstr.c.obj

[ 62%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_read.c.obj

[ 63%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_release_fd.c.obj

[ 64%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_remap_cached.c.obj

[ 65%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_remap_uncached.c.obj

[ 67%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_rename.c.obj

[ 68%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_sbrk.c.obj

[ 69%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_settod.c.obj

[ 70%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_stat.c.obj

[ 71%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_tick.c.obj

[ 72%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_times.c.obj

[ 73%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_tls.c.obj

[ 74%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_uncached_free.c.obj

[ 75%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_uncached_malloc.c.obj

[ 76%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_unlink.c.obj

[ 78%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_usleep.c.obj

[ 79%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_wait.c.obj

[ 80%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/alt_write.c.obj

[ 81%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/intel_fpga_api_cmn_dfl.c.obj

[ 82%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/intel_fpga_api_cmn_inf.c.obj

[ 83%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/intel_fpga_api_cmn_msg.c.obj

[ 84%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/intel_fpga_api_niosv.c.obj

[ 85%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/intel_fpga_platform_api_niosv.c.obj

[ 86%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/intel_niosv_irq.c.obj

[ 87%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/HAL/src/mtimer.c.obj

[ 89%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/alt_sys_init.c.obj

[ 90%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/drivers/src/altera_avalon_jtag_uart_fd.c.obj

[ 91%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/drivers/src/altera_avalon_jtag_uart_init.c.obj

[ 92%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/drivers/src/altera_avalon_jtag_uart_ioctl.c.obj

[ 93%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/drivers/src/altera_avalon_jtag_uart_read.c.obj

[ 94%] Building C object bsp_hal/CMakeFiles/hal2_bsp.dir/drivers/src/altera_avalon_jtag_uart_write.c.obj

[ 95%] Linking C static library libhal2_bsp.a

[ 95%] Built target hal2_bsp

[ 96%] Building C object CMakeFiles/hello.elf.dir/hello.c.obj

[ 97%] Linking C executable hello.elf

[ 97%] Built target hello.elf

[ 98%] Creating hello.elf.objdump.

[ 98%] Built target create-objdump

[100%] Reporting memory available for stack + heap in hello.elf.

hello.elf

* 110.77 KB - Program size (code + initialized data).

* 138.26 KB - Free for stack + heap.

[100%] Built target niosv-stack-report

make: Leaving directory '/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/app_hal/build'

5.1.5 hello.elfファイルダウンロード

次に作成したELFファイルを下記のコマンドでターゲットのRAMにダウンロードします。

niosv-download sw/app_hal/build/hello.elf

出力

INFO: Generating OpenOCD config file. Running "openocd-cfg-gen /tmp/tmpr4uqn_43/niosv.cfg".

/bin/bash: /home/ubuntu_usr/intelFPGA_pro/23.3/niosv/bin/../../quartus/linux64/libtinfo.so.6: no version information available (required by /bin/bash)

INFO: Starting OpenOCD. Running "openocd -c tcl_port disabled -c gdb_port 0 -c telnet_port 0 -f /tmp/tmpr4uqn_43/niosv.cfg".

[OpenOCD output] Open On-Chip Debugger 0.11.0-R22.4

[OpenOCD output] Licensed under GNU GPL v2

[OpenOCD output] For bug reports, read

[OpenOCD output] http://openocd.org/doc/doxygen/bugs.html

[OpenOCD output] Info : only one transport option; autoselect 'jtag'

[OpenOCD output] Info : Application name is OpenOCD.20231127172750

[OpenOCD output] Info : Attempting to find 'USB-BlasterII [1-6.1]'

[OpenOCD output]

[OpenOCD output] Info : Cable 1: device_name=(null), hw_name=USB-BlasterII, server=(null), port=1-6.1, chain_id=0x55ca56909410, persistent_id=1, chain_type=1, features=2048, server_version_info=(null)

[OpenOCD output] Info : TAP position 0 (2E050DD) has 3 SLD nodes

[OpenOCD output] Info : node 0 idcode=00486E00 position_n=0

[OpenOCD output] Info : node 1 idcode=08986E00 position_n=0

[OpenOCD output] Info : node 2 idcode=0C006E00 position_n=0

[OpenOCD output] Info : TAP position 1 (4BA00477) has 0 SLD nodes

[OpenOCD output] Info : Discovered 2 TAP devices

[OpenOCD output] Info : Detected device (tap_position=0) device_id=02e050dd, instruction_length=10, features=4, device_name=10AS066H(1|2|3|3E2|4|4E2)/..

[OpenOCD output] Info : Found an Intel device at tap_position 0.Currently assuming it is SLD Hub

[OpenOCD output] Info : Detected device (tap_position=1) device_id=4ba00477, instruction_length=4, features=0, device_name=SOCVHPS

[OpenOCD output] Info : Found a ARM device at tap_position 1. Currently assume it is JTAG-DP capable

[OpenOCD output] Info : This adapter doesn't support configurable speed

[OpenOCD output] Info : JTAG tap: tap_02E050DD.0 tap/device found: 0x02e050dd (mfg: 0x06e (Altera), part: 0x2e05, ver: 0x0)

[OpenOCD output] Info : JTAG tap: tap_4BA00477.0 tap/device found: 0x4ba00477 (mfg: 0x23b (ARM Ltd), part: 0xba00, ver: 0x4)

[OpenOCD output] Info : JTAG tap: tap_02E050DD.0 Parent Tap found: 0x02e050dd (mfg: 0x06e (Altera), part: 0x2e05, ver: 0x0)

[OpenOCD output] Info : Virtual Tap/SLD node 0x08986E00 found at tap position 0 vtap position 1

[OpenOCD output] Info : datacount=2 progbufsize=8

[OpenOCD output] Info : Examined RISC-V core; found 1 harts

[OpenOCD output] Info : hart 0: XLEN=32, misa=0x40000101

[OpenOCD output] Info : starting gdb server for tap_02E050DD.0.niosv_0.cpu on 0

[OpenOCD output] Info : Listening on port 38223 for gdb connections

INFO: Found gdb port 38223

[OpenOCD output] Ready for Remote Connections

[OpenOCD output] Info : tcl server disabled

[OpenOCD output] Info : Listening on port 46631 for telnet connections

INFO: Found telnet port 46631

INFO: OpenOCD is ready.

INFO: Loading image via GDB. Running "riscv32-unknown-elf-gdb -batch -ex set arch riscv:rv32 -ex set remotetimeout 60 -ex target extended-remote localhost:38223 -ex load sw/app_hal/build/hello.elf -ex set $mstatus &= ~(0x00000088)".

The target architecture is set to "riscv:rv32".

warning: No executable has been specified and target does not support

determining executable automatically. Try using the "file" command.

0x00000008 in ?? ()

Loading section .entry, size 0x20 lma 0x0

Loading section .exceptions, size 0x29c lma 0x20

Loading section .text, size 0x18c0c lma 0x2bc

Loading section .rodata, size 0xf60 lma 0x18ed0

Loading section .rwdata, size 0x1bd8 lma 0x1ba08

Start address 0x0000036c, load size 113152

Transfer rate: 186 KB/sec, 10286 bytes/write.

[Inferior 1 (Remote target) detached]

5.1.6 ISSP (In-System Source & Probe)によりCPUをリセット

デザイン作成時に説明したとおり、本デザインのリセット信号はISSPに接続されています。ISSPによってリセット信号をトグルさせ、デザインをリセットします。

ISSPについては

2.3.1. In-System Sources and Probes

を参照してください。

下記のコマンドを実行することで、デザインがリセットされます。

quartus_stp -t scripts/toggle_issp.tcl

出力

Info: *******************************************************************

Info: Running Quartus Prime Signal Tap

Info: Version 23.3.0 Build 104 09/20/2023 SC Pro Edition

Info: Copyright (C) 2023 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and any partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel FPGA IP License Agreement, or other applicable license

Info: agreement, including, without limitation, that your use is for

Info: the sole purpose of programming logic devices manufactured by

Info: Intel and sold by Intel or its authorized distributors. Please

Info: refer to the Intel FPGA Software License Subscription Agreements

Info: on the Quartus Prime software download page.

Info: Processing started: Mon Nov 27 17:28:43 2023

Info: System process ID: 69244

Info: Command: quartus_stp -t scripts/toggle_issp.tcl

Info: The application is running in 'DNI' mode.

Info (23030): Evaluation of Tcl script scripts/toggle_issp.tcl was successful

Info: Quartus Prime Signal Tap was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 737 megabytes

Info: Processing ended: Mon Nov 27 17:28:44 2023

Info: Elapsed time: 00:00:01

Info: System process ID: 69244

5.1.7 ターミナル上にHello worldを表示

下記コマンドを実行して、デザインに実装したJTAG-UARTをホスト上にメッセージ表示させます。JTAG-UARTはホストと通信が確立するまで待機していますので、メッセージが先頭から始まっているので確認できます。終了するには"CTRL+C"を押してください。

juart-terminal

出力

juart-terminal: connected to hardware target using JTAG UART on cable

juart-terminal: "USB-BlasterII [1-6.1]", device 1, instance 0

juart-terminal: (Use the IDE stop button or Ctrl-C to terminate)

Hello world, this is the Nios V/m cpu checking in 0...

Hello world, this is the Nios V/m cpu checking in 1...

Hello world, this is the Nios V/m cpu checking in 2...

Hello world, this is the Nios V/m cpu checking in 3...

Hello world, this is the Nios V/m cpu checking in 4...

Hello world, this is the Nios V/m cpu checking in 5...

.....

.....

.....

Hello world, this is the Nios V/m cpu checking in 995...

Hello world, this is the Nios V/m cpu checking in 996...

Hello world, this is the Nios V/m cpu checking in 997...

Hello world, this is the Nios V/m cpu checking in 998...

Hello world, this is the Nios V/m cpu checking in 999...

Bye world!

juart-terminal: exiting due to ^C on host

5.2 uCOS-II編

次にuC/OS-IIのサンプルをコンパイルし、実行します。

5.2.1 Board Support Package(BSP)生成

下記コマンドを使用してuC/OSii用のBSPを生成します。bsp設定ファイルとしてsw/bsp_ucosii/settings.bspが用意されています。Typeにはucosiiを指定してください。

niosv-bsp -c --quartus-project=hw/top.qpf --qsys=hw/sys.qsys --type=ucosii sw/bsp_ucosii/settings.bsp

出力

2023.11.28.00:33:30 Info: Searching for BSP components with category: os_software_element

2023.11.28.00:33:31 Info: Creating BSP settings.

2023.11.28.00:33:31 Info: Searching for BSP components with category: driver_element

2023.11.28.00:33:31 Info: Searching for BSP components with category: software_package_element

2023.11.28.00:33:31 Info: Loading drivers from ensemble report.

2023.11.28.00:33:31 Info: Finished loading drivers from ensemble report.

2023.11.28.00:33:31 Info: Evaluating default script "/home/ubuntu_usr/intelFPGA_pro/23.3/quartus/../niosv/scripts/bsp-defaults/bsp-set-defaults.tcl".

2023.11.28.00:33:31 Info: Tcl message: "STDIO character device is jtag_uart"

2023.11.28.00:33:31 Info: Tcl message: "System timer device is cpu"

2023.11.28.00:33:31 Info: Tcl message: "Default linker sections mapped to ram"

2023.11.28.00:33:31 Info: Tcl message: "No bootloader located at the reset address."

2023.11.28.00:33:31 Info: Tcl message: "Application ELF allowed to contain code at the reset address."

2023.11.28.00:33:31 Info: Tcl message: "The alt_load() facility is enabled."

2023.11.28.00:33:31 Info: Tcl message: "The .rwdata section is copied into RAM by alt_load()."

2023.11.28.00:33:31 Info: Saving BSP settings file.

2023.11.28.00:33:31 Info: Default memory regions will not be persisted in BSP Settings File.

2023.11.28.00:33:31 Info: Generated file "/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/bsp_ucosii/settings.bsp"

2023.11.28.00:33:31 Info: Generating BSP files in "/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/bsp_ucosii"

2023.11.28.00:33:31 Info: Default memory regions will not be persisted in BSP Settings File.

2023.11.28.00:33:31 Info: Generated file "/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/bsp_ucosii/settings.bsp"

2023.11.28.00:33:31 Info: Finished generating BSP files. Total time taken = 2 seconds

5.2.2 CMafileLists.txt生成

CMakefileLists.txtを生成します。アプリケーションディレクトリやソースコードはuC/OSii用のものがsw/app_ucosiiの中に用意されていますのでそちらを使用します。

niosv-app --bsp-dir=sw/bsp_ucosii --app-dir=sw/app_ucosii --srcs=sw/app_ucosii --elf-name=hello_ucosii.elf

出力

2023.11.28.00:56:14 Info: Elf name is set to "hello_ucosii.elf".

2023.11.28.00:56:14 Info: Source file "hello_ucosii.c" added from directory "sw/app_ucosii".

2023.11.28.00:56:14 Info: "sw/app_ucosii/CMakeLists.txt" was generated.

5.2.3 Makefile生成

下記コマンドを実行して、CMakeLists.txtよりMakefileを生成します。

cmake -S sw/app_ucosii -G "Unix Makefiles" -B sw/app_ucosii/build

出力

-- Defaulting build type to Debug.

-- The ASM compiler identification is GNU

-- Found assembler: /home/ubuntu_usr/intelFPGA_pro/23.3/riscfree/toolchain/riscv32-unknown-elf/bin/riscv32-unknown-elf-gcc

-- The C compiler identification is GNU 12.1.0

-- Detecting C compiler ABI info

-- Detecting C compiler ABI info - done

-- Check for working C compiler: /home/ubuntu_usr/intelFPGA_pro/23.3/riscfree/toolchain/riscv32-unknown-elf/bin/riscv32-unknown-elf-gcc - skipped

-- Detecting C compile features

-- Detecting C compile features - done

-- The CXX compiler identification is GNU 12.1.0

-- Detecting CXX compiler ABI info

-- Detecting CXX compiler ABI info - done

-- Check for working CXX compiler: /home/ubuntu_usr/intelFPGA_pro/23.3/riscfree/toolchain/riscv32-unknown-elf/bin/riscv32-unknown-elf-g++ - skipped

-- Detecting CXX compile features

-- Detecting CXX compile features - done

-- Configuring done (0.2s)

-- Generating done (0.0s)

-- Build files have been written to: /home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/app_ucosii/build

5.2.4 hello_ucosii.elf生成

下記コマンドを実行して、hello_ucosii.elfを生成します。

make -C sw/app_ucosii/build

出力

make: Entering directory '/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/app_ucosii/build'

[ 1%] Building ASM object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_log_macro.S.obj

[ 2%] Building ASM object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_mcount.S.obj

[ 3%] Building ASM object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/crt0.S.obj

[ 4%] Building ASM object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/machine_trap.S.obj

[ 5%] Building ASM object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/os_cpu_a.S.obj

[ 6%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_alarm_start.c.obj

[ 7%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_busy_sleep.c.obj

[ 8%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_close.c.obj

[ 9%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_dcache_flush.c.obj

[ 10%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_dcache_flush_all.c.obj

[ 11%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_dcache_flush_no_writeback.c.obj

[ 12%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_dev.c.obj

[ 13%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_dev_llist_insert.c.obj

[ 14%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_dma_rxchan_open.c.obj

[ 15%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_dma_txchan_open.c.obj

[ 16%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_do_ctors.c.obj

[ 17%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_do_dtors.c.obj

[ 17%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_environ.c.obj

[ 18%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_errno.c.obj

[ 19%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_execve.c.obj

[ 20%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_exit.c.obj

[ 21%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_fcntl.c.obj

[ 22%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_fd_lock.c.obj

[ 23%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_fd_unlock.c.obj

[ 24%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_find_dev.c.obj

[ 25%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_find_file.c.obj

[ 26%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_flash_dev.c.obj

[ 27%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_fork.c.obj

[ 28%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_fs_reg.c.obj

[ 29%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_fstat.c.obj

[ 30%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_get_fd.c.obj

[ 31%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_getchar.c.obj

[ 32%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_getpid.c.obj

[ 33%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_gettod.c.obj

[ 34%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_gmon.c.obj

[ 35%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_icache_flush.c.obj

[ 36%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_icache_flush_all.c.obj

[ 37%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_iic.c.obj

[ 37%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_iic_isr_register.c.obj

[ 38%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_instruction_exception_register.c.obj

[ 39%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_io_redirect.c.obj

[ 40%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_ioctl.c.obj

[ 41%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_irq_handler.c.obj

[ 42%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_isatty.c.obj

[ 43%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_kill.c.obj

[ 44%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_link.c.obj

[ 45%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_load.c.obj

[ 46%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_log_printf.c.obj

[ 47%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_lseek.c.obj

[ 48%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_main.c.obj

[ 49%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_open.c.obj

[ 50%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_printf.c.obj

[ 51%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_putchar.c.obj

[ 52%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_putcharbuf.c.obj

[ 53%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_putstr.c.obj

[ 54%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_read.c.obj

[ 55%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_release_fd.c.obj

[ 56%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_remap_cached.c.obj

[ 57%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_remap_uncached.c.obj

[ 57%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_rename.c.obj

[ 58%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_sbrk.c.obj

[ 59%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_settod.c.obj

[ 60%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_stat.c.obj

[ 61%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_tick.c.obj

[ 62%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_times.c.obj

[ 63%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_tls.c.obj

[ 64%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_uncached_free.c.obj

[ 65%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_uncached_malloc.c.obj

[ 66%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_unlink.c.obj

[ 67%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_usleep.c.obj

[ 68%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_wait.c.obj

[ 69%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/alt_write.c.obj

[ 70%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/intel_fpga_api_cmn_dfl.c.obj

[ 71%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/intel_fpga_api_cmn_inf.c.obj

[ 72%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/intel_fpga_api_cmn_msg.c.obj

[ 73%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/intel_fpga_api_niosv.c.obj

[ 74%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/intel_fpga_platform_api_niosv.c.obj

[ 75%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/intel_niosv_irq.c.obj

[ 76%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/mtimer.c.obj

[ 77%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/HAL/src/os_cpu_c.c.obj

[ 77%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/alt_env_lock.c.obj

[ 78%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/alt_malloc_lock.c.obj

[ 79%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/os_core.c.obj

[ 80%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/os_dbg_r.c.obj

[ 81%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/os_flag.c.obj

[ 82%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/os_mbox.c.obj

[ 83%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/os_mem.c.obj

[ 84%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/os_mutex.c.obj

[ 85%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/os_q.c.obj

[ 86%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/os_sem.c.obj

[ 87%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/os_task.c.obj

[ 88%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/os_time.c.obj

[ 89%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/os_tmr.c.obj

[ 90%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/UCOSII/src/ucos_ii.c.obj

[ 91%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/alt_sys_init.c.obj

[ 92%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/drivers/src/altera_avalon_jtag_uart_fd.c.obj

[ 93%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/drivers/src/altera_avalon_jtag_uart_init.c.obj

[ 94%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/drivers/src/altera_avalon_jtag_uart_ioctl.c.obj

[ 95%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/drivers/src/altera_avalon_jtag_uart_read.c.obj

[ 96%] Building C object bsp_ucosii/CMakeFiles/ucosii_hal2_bsp.dir/drivers/src/altera_avalon_jtag_uart_write.c.obj

[ 97%] Linking C static library libucosii_hal2_bsp.a

[ 97%] Built target ucosii_hal2_bsp

[ 97%] Building C object CMakeFiles/app_ucosii.elf.dir/hello_ucosii.c.obj

[ 98%] Linking C executable app_ucosii.elf

[ 98%] Built target app_ucosii.elf

[ 99%] Creating app_ucosii.elf.objdump.

[ 99%] Built target create-objdump

[100%] Reporting memory available for stack + heap in app_ucosii.elf.

app_ucosii.elf

* 186.04 KB - Program size (code + initialized data).

* 62.98 KB - Free for stack + heap.

[100%] Built target niosv-stack-report

make: Leaving directory '/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/app_ucosii/build'

5.2.5 hello_ucosii.elfファイルダウンロード

次に、作成したELFファイルを下記のコマンドでターゲットのRAMにダウンロードします。

niosv-download sw/app_ucosii/build/hello_ucosii.elf

出力

INFO: Generating OpenOCD config file. Running "openocd-cfg-gen /tmp/tmp9eayfe_7/niosv.cfg".

INFO: Starting OpenOCD. Running "openocd -c tcl_port disabled -c gdb_port 0 -c telnet_port 0 -f /tmp/tmp9eayfe_7/niosv.cfg".

[OpenOCD output] Open On-Chip Debugger 0.11.0-R22.4

[OpenOCD output] Licensed under GNU GPL v2

[OpenOCD output] For bug reports, read

[OpenOCD output] http://openocd.org/doc/doxygen/bugs.html

[OpenOCD output] Info : only one transport option; autoselect 'jtag'

[OpenOCD output] Info : Application name is OpenOCD.20231128010450

[OpenOCD output] Info : Attempting to find 'USB-BlasterII [1-6.1]'

[OpenOCD output]

[OpenOCD output] Info : Cable 1: device_name=(null), hw_name=USB-BlasterII, server=(null), port=1-6.1, chain_id=0x555c3bd47420, persistent_id=1, chain_type=1, features=2048, server_version_info=(null)

[OpenOCD output] Info : TAP position 0 (2E050DD) has 3 SLD nodes

[OpenOCD output] Info : node 0 idcode=00486E00 position_n=0

[OpenOCD output] Info : node 1 idcode=08986E00 position_n=0

[OpenOCD output] Info : node 2 idcode=0C006E00 position_n=0

[OpenOCD output] Info : TAP position 1 (4BA00477) has 0 SLD nodes

[OpenOCD output] Info : Discovered 2 TAP devices

[OpenOCD output] Info : Detected device (tap_position=0) device_id=02e050dd, instruction_length=10, features=4, device_name=10AS066H(1|2|3|3E2|4|4E2)/..

[OpenOCD output] Info : Found an Intel device at tap_position 0.Currently assuming it is SLD Hub

[OpenOCD output] Info : Detected device (tap_position=1) device_id=4ba00477, instruction_length=4, features=0, device_name=SOCVHPS

[OpenOCD output] Info : Found a ARM device at tap_position 1. Currently assume it is JTAG-DP capable

[OpenOCD output] Info : This adapter doesn't support configurable speed

[OpenOCD output] Info : JTAG tap: tap_02E050DD.0 tap/device found: 0x02e050dd (mfg: 0x06e (Altera), part: 0x2e05, ver: 0x0)

[OpenOCD output] Info : JTAG tap: tap_4BA00477.0 tap/device found: 0x4ba00477 (mfg: 0x23b (ARM Ltd), part: 0xba00, ver: 0x4)

[OpenOCD output] Info : JTAG tap: tap_02E050DD.0 Parent Tap found: 0x02e050dd (mfg: 0x06e (Altera), part: 0x2e05, ver: 0x0)

[OpenOCD output] Info : Virtual Tap/SLD node 0x08986E00 found at tap position 0 vtap position 1

[OpenOCD output] Info : datacount=2 progbufsize=8

[OpenOCD output] Info : Examined RISC-V core; found 1 harts

[OpenOCD output] Info : hart 0: XLEN=32, misa=0x40000101

[OpenOCD output] Info : starting gdb server for tap_02E050DD.0.niosv_0.cpu on 0

[OpenOCD output] Info : Listening on port 46563 for gdb connections

INFO: Found gdb port 46563

[OpenOCD output] Ready for Remote Connections

[OpenOCD output] Info : tcl server disabled

[OpenOCD output] Info : Listening on port 33965 for telnet connections

INFO: Found telnet port 33965

INFO: OpenOCD is ready.

INFO: Loading image via GDB. Running "riscv32-unknown-elf-gdb -batch -ex set arch riscv:rv32 -ex set remotetimeout 60 -ex target extended-remote localhost:46563 -ex load sw/app_ucosii/build/hello_ucosii.elf -ex set $mstatus &= ~(0x00000088)".

The target architecture is set to "riscv:rv32".

warning: No executable has been specified and target does not support

determining executable automatically. Try using the "file" command.

0x00000000 in ?? ()

Loading section .entry, size 0x20 lma 0x0

Loading section .exceptions, size 0x29c lma 0x20

Loading section .text, size 0x22ef4 lma 0x2bc

Loading section .rodata, size 0x1128 lma 0x231b0

Loading section .rwdata, size 0x1bf0 lma 0x25ec8

Start address 0x00000614, load size 155336

Transfer rate: 146 KB/sec, 11095 bytes/write.

[Inferior 1 (Remote target) detached]

5.2.6 ISSP (In-System Source & Probe)によりCPUをリセット

下記のコマンドを実行して、リセット信号をトグルさせ、デザインをリセットします。

quartus_stp -t scripts/toggle_issp.tcl

出力

Info: *******************************************************************

Info: Running Quartus Prime Signal Tap

Info: Version 23.3.0 Build 104 09/20/2023 SC Pro Edition

Info: Copyright (C) 2023 Intel Corporation. All rights reserved.

Info: Your use of Intel Corporation's design tools, logic functions

Info: and other software and tools, and any partner logic

Info: functions, and any output files from any of the foregoing

Info: (including device programming or simulation files), and any

Info: associated documentation or information are expressly subject

Info: to the terms and conditions of the Intel Program License

Info: Subscription Agreement, the Intel Quartus Prime License Agreement,

Info: the Intel FPGA IP License Agreement, or other applicable license

Info: agreement, including, without limitation, that your use is for

Info: the sole purpose of programming logic devices manufactured by

Info: Intel and sold by Intel or its authorized distributors. Please

Info: refer to the Intel FPGA Software License Subscription Agreements

Info: on the Quartus Prime software download page.

Info: Processing started: Tue Nov 28 01:06:33 2023

Info: System process ID: 10957

Info: Command: quartus_stp -t scripts/toggle_issp.tcl

Info: The application is running in 'DNI' mode.

Info (23030): Evaluation of Tcl script scripts/toggle_issp.tcl was successful

Info: Quartus Prime Signal Tap was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 737 megabytes

Info: Processing ended: Tue Nov 28 01:06:34 2023

Info: Elapsed time: 00:00:01

Info: System process ID: 10957

5.2.7 ターミナル上にHello from taskを表示

下記コマンドを実行して、デザインに実装したJTAG-UARTをホスト上にメッセージ表示させます。終了するには"CTRL+C"を押してください。

juart-terminal

出力

juart-terminal: connected to hardware target using JTAG UART on cable

juart-terminal: "USB-BlasterII [1-6.1]", device 1, instance 0

juart-terminal: (Use the IDE stop button or Ctrl-C to terminate)

Hello from main...

Hello from task1: 0

Hello from task2: 0

Hello from task3: 0

Hello from task3: 1

Hello from task2: 1

Hello from task3: 2

Hello from task1: 1

Hello from task3: 3

Hello from task2: 2

Hello from task3: 4

Hello from task3: 5

Hello from task2: 3

Hello from task1: 2

Hello from task3: 6

.....

.....

.....

Hello from task2: 31

Hello from task1: 19

juart-terminal: exiting due to ^C on host

5.3 FreeRTOS™編

次にFreeRTOS™のサンプルをコンパイルし、実行します。

5.3.1 Board Support Package(BSP)生成

下記コマンドを使用してFreeRTOS™用のBSPを生成します。bsp設定ファイルとしてsw/bsp_freertos/settings.bspが用意されています。Typeにはfreertosを指定してください。

niosv-bsp -c --quartus-project=hw/top.qpf --qsys=hw/sys.qsys --type=freertos sw/bsp_freertos/settings.bsp

出力

2023.11.28.01:10:14 Info: Searching for BSP components with category: os_software_element

2023.11.28.01:10:16 Info: Creating BSP settings.

2023.11.28.01:10:16 Info: Searching for BSP components with category: driver_element

2023.11.28.01:10:16 Info: Searching for BSP components with category: software_package_element

2023.11.28.01:10:16 Info: Loading drivers from ensemble report.

2023.11.28.01:10:16 Info: Finished loading drivers from ensemble report.

2023.11.28.01:10:16 Info: Evaluating default script "/home/ubuntu_usr/intelFPGA_pro/23.3/quartus/../niosv/scripts/bsp-defaults/bsp-set-defaults.tcl".

2023.11.28.01:10:16 Info: Tcl message: "STDIO character device is jtag_uart"

2023.11.28.01:10:16 Info: Tcl message: "System timer device is cpu"

2023.11.28.01:10:16 Info: Tcl message: "Default linker sections mapped to ram"

2023.11.28.01:10:16 Info: Tcl message: "No bootloader located at the reset address."

2023.11.28.01:10:16 Info: Tcl message: "Application ELF allowed to contain code at the reset address."

2023.11.28.01:10:16 Info: Tcl message: "The alt_load() facility is enabled."

2023.11.28.01:10:16 Info: Tcl message: "The .rwdata section is copied into RAM by alt_load()."

2023.11.28.01:10:16 Info: Saving BSP settings file.

2023.11.28.01:10:16 Info: Default memory regions will not be persisted in BSP Settings File.

2023.11.28.01:10:16 Info: Generated file "/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/bsp_freertos/settings.bsp"

2023.11.28.01:10:16 Info: Generating BSP files in "/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/bsp_freertos"

2023.11.28.01:10:16 Info: Default memory regions will not be persisted in BSP Settings File.

2023.11.28.01:10:16 Info: Generated file "/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/bsp_freertos/settings.bsp"

2023.11.28.01:10:16 Info: Finished generating BSP files. Total time taken = 2 seconds

5.3.2 CMafileLists.txt生成

CMakefileLists.txtを生成します。アプリケーションディレクトリやソースコードはFreeRTOS™用のものがsw/app_freertosの中に用意されていますのでそちらを使用します。

niosv-app --bsp-dir=sw/bsp_freertos --app-dir=sw/app_freertos --srcs=sw/app_freertos --elf-name=hello_freertos.elf

出力

2023.11.28.01:12:10 Info: Elf name is set to "hello_freertos.elf".

2023.11.28.01:12:10 Info: Source file "hello_freertos.c" added from directory "sw/app_freertos".

2023.11.28.01:12:10 Info: "sw/app_freertos/CMakeLists.txt" was generated.

5.3.3 Makefile生成

下記コマンドを実行して、CMakeLists.txtよりMakefileを生成します。初めて生成する際にはsw/app_freertos/build/CMakeCache.txtを削除する必要があります。

rm sw/app_freertos/build/CMakeCache.txt

次にMakeFileを生成します。

cmake -S sw/app_freertos -G "Unix Makefiles" -B sw/app_freertos/build

-- Defaulting build type to Debug.

-- The ASM compiler identification is GNU

-- Found assembler: /home/ubuntu_usr/intelFPGA_pro/23.3/riscfree/toolchain/riscv32-unknown-elf/bin/riscv32-unknown-elf-gcc

-- The C compiler identification is GNU 12.1.0

-- Detecting C compiler ABI info

-- Detecting C compiler ABI info - done

-- Check for working C compiler: /home/ubuntu_usr/intelFPGA_pro/23.3/riscfree/toolchain/riscv32-unknown-elf/bin/riscv32-unknown-elf-gcc - skipped

-- Detecting C compile features

-- Detecting C compile features - done

-- The CXX compiler identification is GNU 12.1.0

-- Detecting CXX compiler ABI info

-- Detecting CXX compiler ABI info - done

-- Check for working CXX compiler: /home/ubuntu_usr/intelFPGA_pro/23.3/riscfree/toolchain/riscv32-unknown-elf/bin/riscv32-unknown-elf-g++ - skipped

-- Detecting CXX compile features

-- Detecting CXX compile features - done

-- Configuring done (0.2s)

-- Generating done (0.0s)

-- Build files have been written to: /home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/app_freertos/build

5.3.4 hello_ucosii.elf生成

下記コマンドを実行して、hello_freertos.elfを生成します。

make -C sw/app_freertos/build

出力

make: Entering directory '/home/ubuntu_usr/ws/ws_pro/niosv_hello_world/top_project/sw/app_freertos/build'

[ 1%] Building ASM object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_log_macro.S.obj

[ 2%] Building ASM object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_mcount.S.obj

[ 3%] Building ASM object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/crt0.S.obj

[ 4%] Building ASM object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/machine_trap.S.obj

[ 5%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/FREERTOS/src/alt_env_lock.c.obj

[ 6%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/FREERTOS/src/alt_malloc_lock.c.obj

[ 7%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/FREERTOS/src/heap_wrapper.c.obj

[ 8%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/FreeRTOS-Kernel/croutine.c.obj

[ 9%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/FreeRTOS-Kernel/event_groups.c.obj

[ 10%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/FreeRTOS-Kernel/list.c.obj

[ 11%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/FreeRTOS-Kernel/portable/GCC/RISC-V/port.c.obj

[ 12%] Building ASM object bsp_freertos/CMakeFiles/freertos_bsp.dir/FreeRTOS-Kernel/portable/GCC/RISC-V/portASM.S.obj

[ 13%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/FreeRTOS-Kernel/queue.c.obj

[ 14%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/FreeRTOS-Kernel/stream_buffer.c.obj

[ 15%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/FreeRTOS-Kernel/tasks.c.obj

[ 16%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/FreeRTOS-Kernel/timers.c.obj

[ 17%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_alarm_start.c.obj

[ 18%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_busy_sleep.c.obj

[ 19%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_close.c.obj

[ 20%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_dcache_flush.c.obj

[ 21%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_dcache_flush_all.c.obj

[ 22%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_dcache_flush_no_writeback.c.obj

[ 23%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_dev.c.obj

[ 24%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_dev_llist_insert.c.obj

[ 25%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_dma_rxchan_open.c.obj

[ 26%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_dma_txchan_open.c.obj

[ 27%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_do_ctors.c.obj

[ 28%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_do_dtors.c.obj

[ 29%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_environ.c.obj

[ 30%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_errno.c.obj

[ 31%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_execve.c.obj

[ 32%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_exit.c.obj

[ 33%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_fcntl.c.obj

[ 34%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_fd_lock.c.obj

[ 35%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_fd_unlock.c.obj

[ 36%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_find_dev.c.obj

[ 37%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_find_file.c.obj

[ 38%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_flash_dev.c.obj

[ 39%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_fork.c.obj

[ 40%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_fs_reg.c.obj

[ 41%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_fstat.c.obj

[ 42%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_get_fd.c.obj

[ 43%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_getchar.c.obj

[ 44%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_getpid.c.obj

[ 45%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_gettod.c.obj

[ 46%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_gmon.c.obj

[ 47%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_icache_flush.c.obj

[ 48%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_icache_flush_all.c.obj

[ 49%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_iic.c.obj

[ 50%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_iic_isr_register.c.obj

[ 50%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_instruction_exception_register.c.obj

[ 51%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_io_redirect.c.obj

[ 52%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_ioctl.c.obj

[ 53%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_irq_handler.c.obj

[ 54%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_isatty.c.obj

[ 55%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_kill.c.obj

[ 56%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_link.c.obj

[ 57%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_load.c.obj

[ 58%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_log_printf.c.obj

[ 59%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_lseek.c.obj

[ 60%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_main.c.obj

[ 61%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_open.c.obj

[ 62%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_printf.c.obj

[ 63%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_putchar.c.obj

[ 64%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_putcharbuf.c.obj

[ 65%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_putstr.c.obj

[ 66%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_read.c.obj

[ 67%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_release_fd.c.obj

[ 68%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_remap_cached.c.obj

[ 69%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_remap_uncached.c.obj

[ 70%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_rename.c.obj

[ 71%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_sbrk.c.obj

[ 72%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_settod.c.obj

[ 73%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_stat.c.obj

[ 74%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_tick.c.obj

[ 75%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_times.c.obj

[ 76%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_tls.c.obj

[ 77%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_uncached_free.c.obj

[ 78%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_uncached_malloc.c.obj

[ 79%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_unlink.c.obj

[ 80%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_usleep.c.obj

[ 81%] Building C object bsp_freertos/CMakeFiles/freertos_bsp.dir/HAL/src/alt_wait.c.obj