概要

この記事はIntel®のFPGA(Field Programmable Gate Array)開発を始めたばかりの初心者の方、特にIntel® Quartus® Prime SoftwareでPlarform Designerを触り始めたけど、IP(Intellectual property)のインターフェースがよくわからないという方向けに書かれた記事です。Avalon® Interfaceにはいくつか種類があるのですが(こちらを参照してください)、中でも使用頻度の高いAvalon® Memory-Mapped Interfacesについて紹介し、信号の検証に使用するAvalon Verification IP Suiteについても説明したいと思います。特にAvalon® Verification IP SuiteについてはこちらのAvalon Verification IP Suite Design Filesをクリックするとテストベンチがダウンロードできるので、実際に動かします。なおテストベンチはIntel® Quartus® Prime Software Standard Editionがあれば動かせるので、実機は必要ありません。

※データのやりとりにおいては、Master⇔Slaveという関係がよく出てきます。この記事では「誰が信号を送っているのか」という説明においては主語をくどいほど明記します。

Avalon® Interfaceとは?

Avalon® InterfaceとはIPのポート、つまりクロックやデータ等、信号の「出入り口」のことです。ただし出入り口と言ってもただ物理的な出入り口があるだけでなく、そこには様々なルールが存在します。

例えば空港を考えてみると、そこには物理的に乗り降りする搭乗ゲートがあるだけではなく、どの便がどのゲートに繋がっているか、何時何分に飛行機が出発or到着するか、など事前に様々な「ルール」が決められているはずです。

その決まり事に従わないと飛行機は空港を行き来することはできません。同じことはAvalon® Interfaceにも当てはまり、これは物理的な「出入口」を意味すると同時に、その出入口を利用するためのプロトコル(ルール)も定義されているのです。

Avalon® Interfaceにはどのようなプロトコルが存在するでしょうか。具体的には

- Avalon® Clock and Reset Interfaces

- Avalon® Memory-Mapped Interfaces

- Avalon® Interrupt Interfaces

- Avalon® Streaming Interfaces

- Avalon® Streaming Credit Interfaces

- Avalon® Conduit Interfaces

- Avalon® Tristate Conduit Interface

などがあります。今回は、中でも使用頻度の高いAvalon® Memory-Mapped Interfacesについて詳しく見てみましょう。

Avalon® Memory-Mapped Interfacesとは?

Avalon® Memory-Mapped Interfacesは、先ほど述べたように物理的な出入口とプロトコル(ルール)の両方を指しています。主に以下のIPの出入り口として使用されます。

- Microprocessors

- Memories

- UARTs

- DMAs

- Timers

SDRAMのようなメモリについて考えてみるとわかりやすいのですが、Masterのreadやwrite信号に応じてデータを双方向にやり取りするためのプロトコルと言えるでしょう。

以下ではAvalon® Memory-Mapped Interfacesにおいてよく使われる信号をテーブルにまとめています。

| Signal Role | Width | Direction | Required | Desctiption |

|---|---|---|---|---|

| address | 1-64 | Master → Slave | No | データのアドレス指定に使用される信号です。当然のことですが、Masterがread信号をassert(信号をactiveにすること。deassertはその逆でinactiveにすること。)している場合、アドレスを指定しないとどのデータをreadしたいのかSlaveは判断できませんし、Masterがwrite信号をassertしている場合、アドレスを指定しないとどこにデータを書き込みたいのかSlaveは判断できません。ただし、Slave側で用意されているレジスターが1つしかない場合に限り、アドレス指定は不要です。 |

| byteenable | 2, 4, 8, 16, 32, 64, 128 | Master → Slave | No | readdata, writedataのうちどのバイトを読み書きしたいのかを指定するための信号です。例えば、32ビットデータに対してbyteenable=0b0001であれば下位8bitを読み書きし、byteenable=0b1000であれば上位8bitが読み書きされます。特にSlave側がバイト単位のアクセスに対応している場合はbyteenable信号を用いて送受信を行います。対応していない周辺機器を使用する場合は、マニュアルでアクセス方法を確認してください。 |

| read | 1 | Master → Slave | No | Masterがreadをassertすれば、SlaveはMasterがデータの読み込みをしたいと判断できます。また、writeのみを行いたい場合read信号は必要ありません。 |

| readdata | 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024 | Slave → Master | No | Masterからのread信号を受け取った後、Slave → Masterに送信されるデータ。read信号を使用しない場合、readdata信号も必要ありません。 |

| response[1:0] | 2 | Slave → Master | No | Slaveが送信する受信ステータス信号。やり取りが正常に行われたかというステータスを知らせるために使用されます。 |

| write | 1 | Master → Slave | No | Masterがwriteをassertすれば、SlaveはMasterがデータを書き込みたいと判断できます。また、readのみを行いたい場合write信号は必要ありません。 |

| writedata | 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024 | Master → Slave | No | Masterがwrite信号と同時に送信する、Slaveへ書き込むデータ。write信号を使用しない場合、writedata信号も必要ありません。 |

Avalon® Memory-Mapped Interfacesの信号パターン

以下ではマニュアルに記載されているいくつかの信号パターンについて見ていきましょう。各サイクル付近において信号がどういう状態なのか説明します。

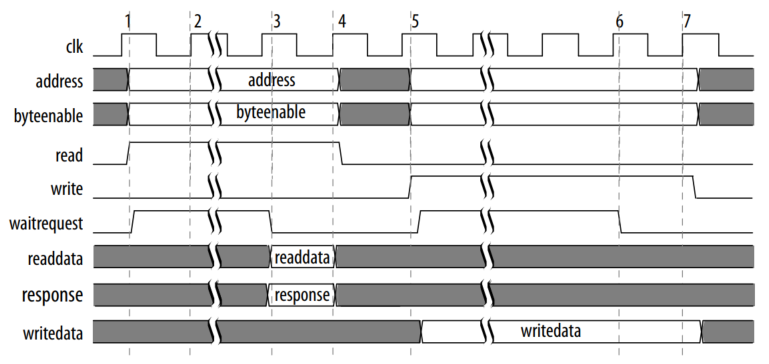

3.5.1. Typical Read and Write Transfers

典型的なread, write信号のやり取りです。各信号をMasterとSlaveのどちらがassertしているのか意識して見てください。

画像引用元: Avalon® Interface Specifications Figure 7. Read and Write Transfers with Waitrequest

- address, byteenable, readがMasterによりassertされる。ただし、Slaveがwaitrequestをassertするので、Slave→Masterへのデータ送信は行われない。

- Slaveがwaitrequestをassertしているので、データの送信は行われない。

- Slaveがwaitrequestをdeassertし、Slave→Masterへデータの送信が行われる。

- Master側でreaddataの受信が完了する。

- readもwriteもdeassertされているため、データの送受信は行われない。

- Master側はwritedataを送り続けているが、waitrequestがassertされているためSlave側はまだデータを受け取らない。

- waitrequestがdeassertされているため、SlaveはMasterからのaddress, byteenable, write, writedataを受け取る。

※信号が灰色になっている部分は不定値です。

※信号はクロックの立ち上がりに対して少し遅れて出力されます。例えば1番目のクロックの立ち上がり付近に着目すると、Masterはaddress, byteenable, read信号をassertしますが、これらはクロックの立ち上がりから少し遅れてassertされていることがわかります。これはD flip-flopから出力が得られるのに少し時間がかかるためです。

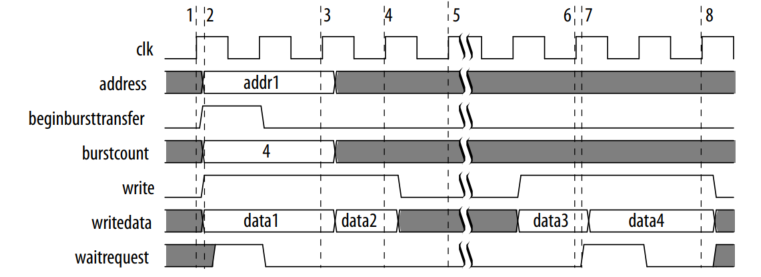

3.5.5.1. Write Bursts

Burstモードで書き込みを行う際の信号例です。ちなみにBurstモードとは連続してデータを送るモードのことです。最初にアドレスとburstcount(何個連続でデータを受信or送信するか)を指定すると、アドレスの位置からデータをburstcount個だけ受信or送信することができます。

画像引用元: Avalon® Interface Specifications Figure 14. Write Burst with constantBurstBehavior Set to False for Master and Slave

- address, beginbursttransfer, burstcount, write, writedataがMasterによりassertされる。ただし、Slaveがwaitrequestをassertするので、Slave→Masterへのデータ送信は行われない。

- Slaveはwaitrequestをassertするので、Slaveはwritedataの受信を完了しない。

- Slaveはwaitrequestをdeassertしているので、Slaveはデータ1を受信する。

- Slaveはwaitrequestをdeassertしているので、Slaveはデータ2を受信する。

- Masterはwriteをdeassertしているので、Slaveはwritedataを受信しない。

- Slaveはwaitrequestをdeassertしているので、Slaveはデータ3を受信する。

- Slaveはwaitrequestをassertするので、Slaveはwritedataを受信しない。

- Slaveはwaitrequestをdeassertしているので、Slaveはデータ4を受信する。

Avalon® Verification IP Suite Design Exampleを動かしてみよう

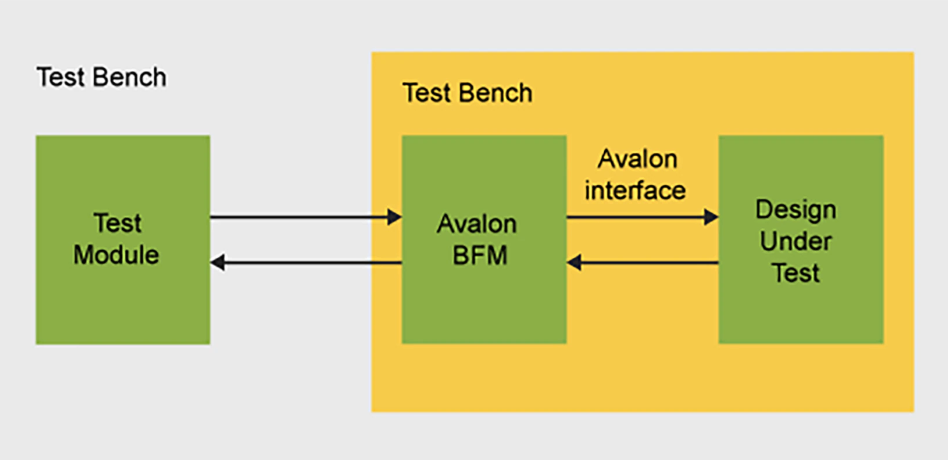

Avalon® Verification IP SuiteとはAvalon® Interfacesの信号を観察するためのシミュレーションライブラリです。以下の図にあるように、Test Moduleをユーザー側で定義し、どのようなシミュレーションを行うか指定できます。Design Exampleのダウンロードで使用するDesign Exampleでは、SystemVerilogを使用してUser Test Benchが記述されています。

画像引用元: Avalon® Verification IP Suite Design Example Figure 1. Verification testbench using Avalon Verification IP Suite.

必要環境

Windows 10 21H2

Intel® Quartus® Prime Software Standard Edition

Design Exampleのダウンロード

こちらのug_avalon_verification.zipをクリックして、Design Exampleをダウンロードしてください。

※Avalon Verification IP Suite User Guide (PDF)はマニュアルです。

ダウンロードが完了したらzipを解凍し、中に

- avlmm_1x1_verilog.zip

- avlmm_1x1_vhdl.zip

- avlmm_2x2_verilog.zip

- avlmm_2x2_vhdl.zip

- ug_avalon_verification.zip

が含まれることを確認してください。

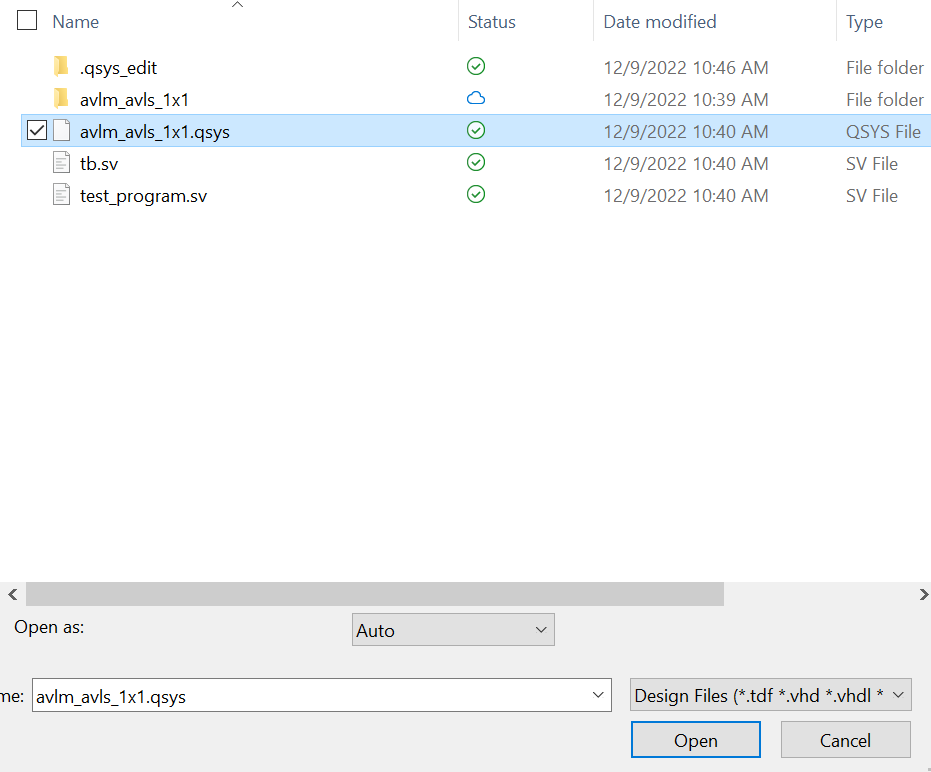

今回使用するのは、avlmm_1x1_verilog.zip のみですので、こちらも解凍してください。

これで準備は完了です。

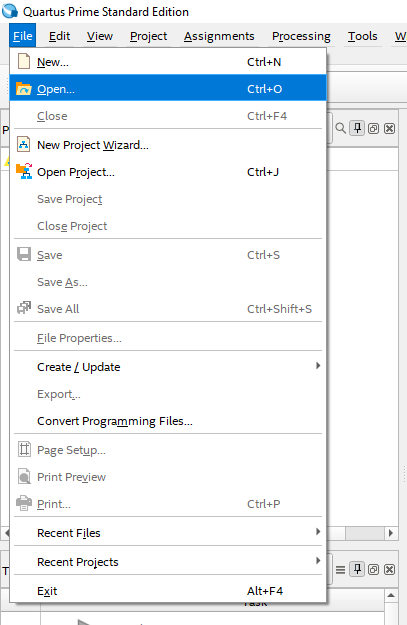

Intel® Quartus® Prime Softwareの操作

Intel® Quartus® Prime Softwareを開き、File>Openをクリックしてください。

File Explorerが起動するので、avlmm_1x1_verilog/avlm_avls_1x1.qsysを選択してOpenをクリックしてください。

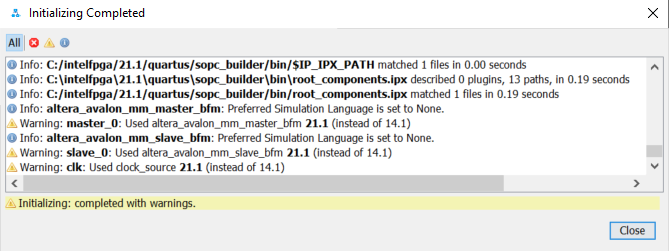

Platform Designerと以下のWindowが起動します。IPのバージョンに関するWarningが出ていますが、特に問題ないのでCloseをクリックしてください。

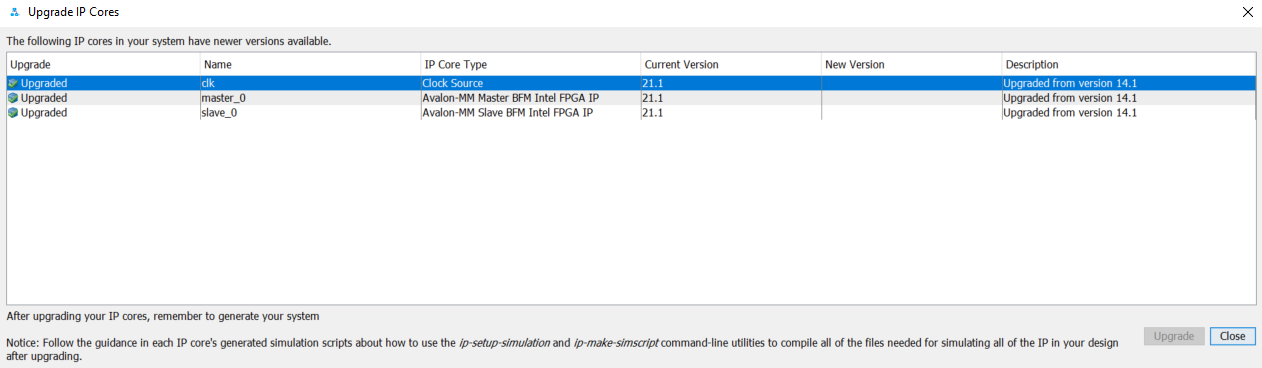

IPをupgradeしたことを知らせる以下のwindowも表示されますので、Closeをクリックして閉じてください。

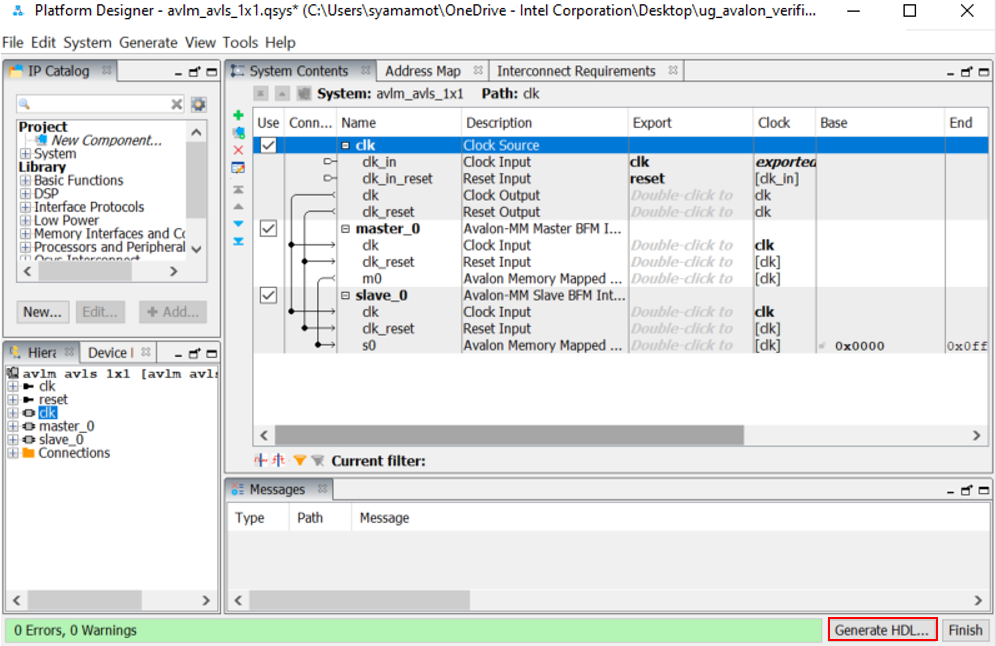

Platform Designer右下のGenerate HDL...をクリックしてください。

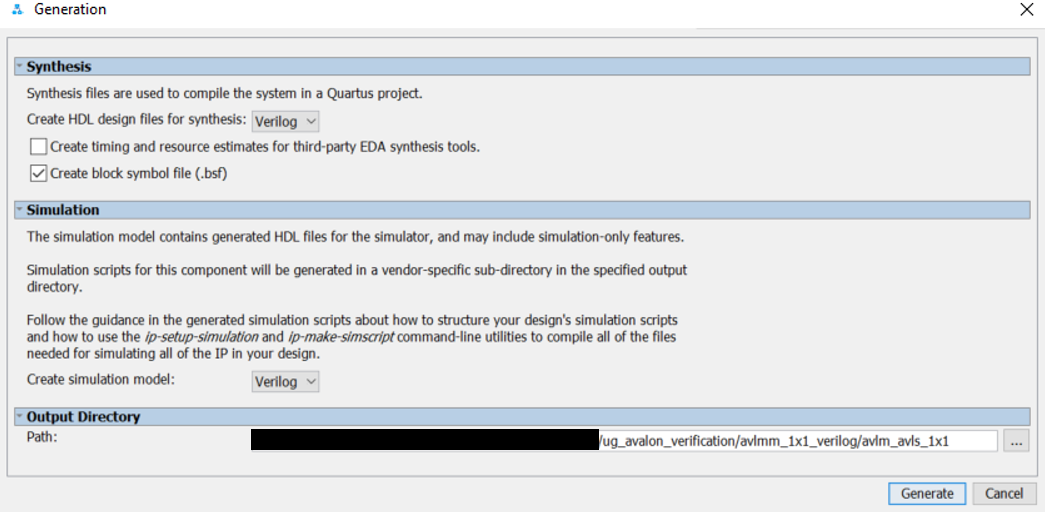

Generationのwindowが表示されるので、以下の画像のように設定し、Generateをクリックしてください。

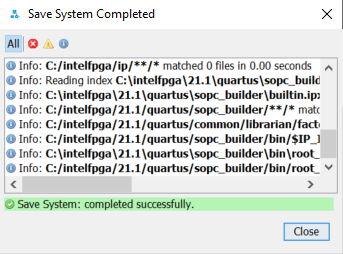

Save System Completedのwindowが表示されるので、Closeをクリックして閉じてください。

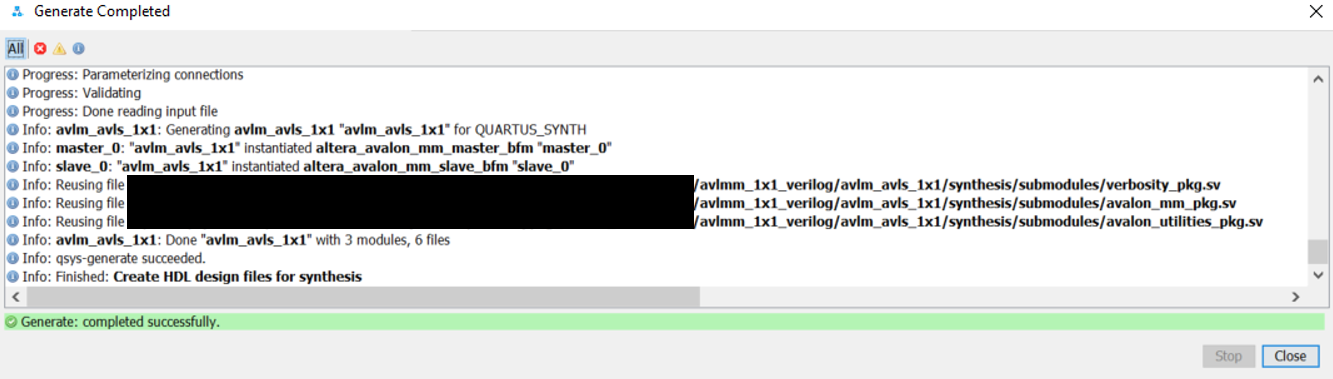

Generate Completedのwindowが表示されるので、Closeをクリックして閉じてください。

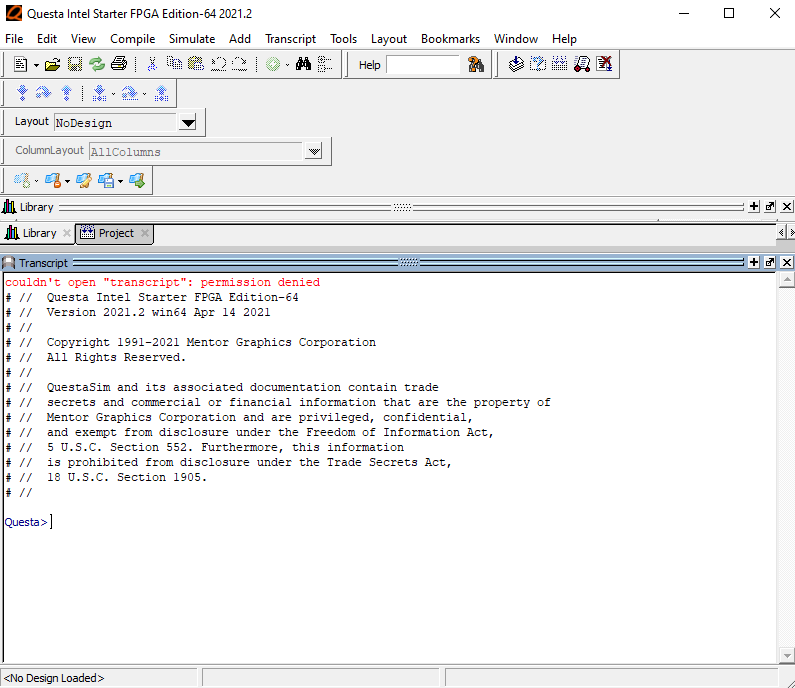

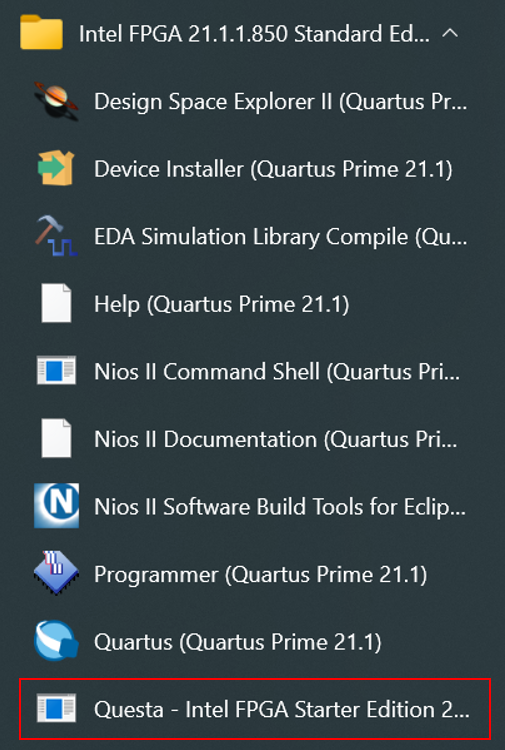

Windowsのスタートメニューから、Questaを起動してください。

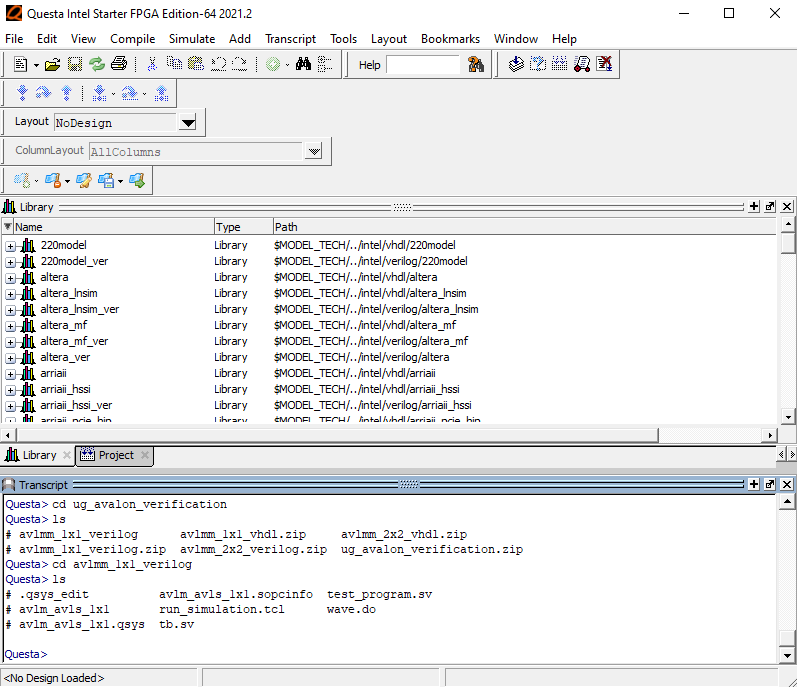

Transcriptからavlmm_1x1_verilogの場所に移動し、

do run_simulation.tcl

を実行してください。以下の画像のように、avlmm_1x1_verilogの中にはrun_simulation.tclが含まれているはずです。

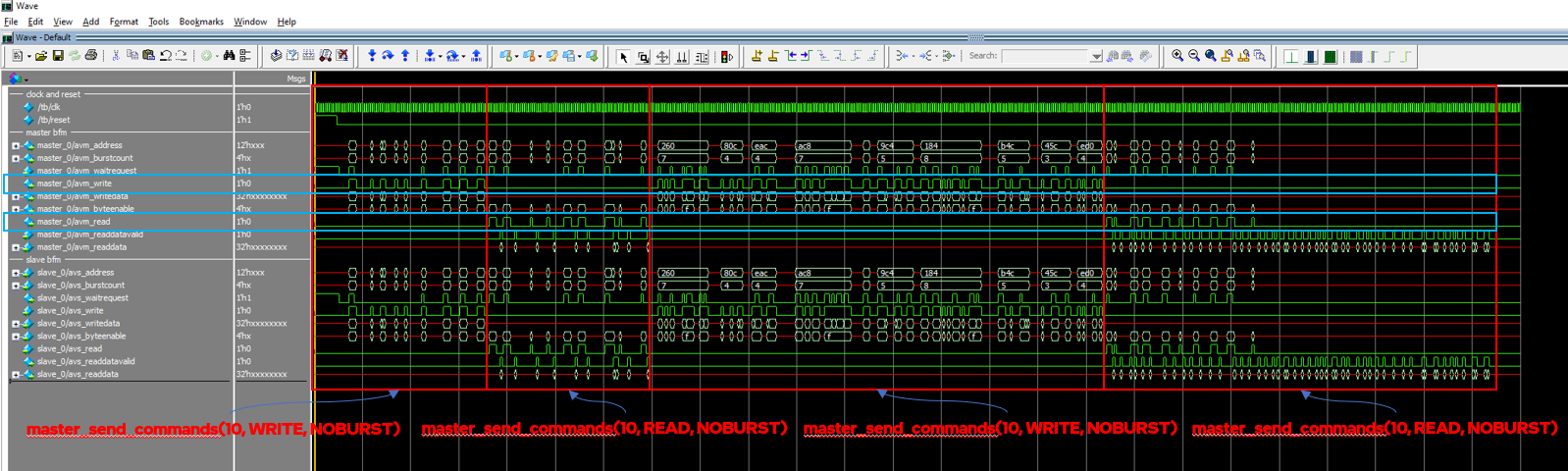

以下のようなシミュレーション結果が表示されることを確認してください。

キーボードのiでzoom inができ、oでzoom outができます。波形が捉えづらい場合は適当な大きさにズームして見るとよいです。

左側の灰色のpaneのavm_write信号とavm_read信号(水色の四角)に着目すると

- masterがwrite信号をassert (no burst)

- masterがread信号をassert (no burst)

- masterがwrite信号をassert (burst)

- masterがread信号をassert (burst)

のように、赤い4つの四角のパートで分けられることがわかります。

Avalon® memory-mapped interfaceが3.5.1. Typical Read and Write Transfersや3.5.5.1. Write Burstsで説明したような動作をしているか、シミュレーション結果をよく観察してみましょう。以下では、4つの赤いブロックの各パートについて解説します。

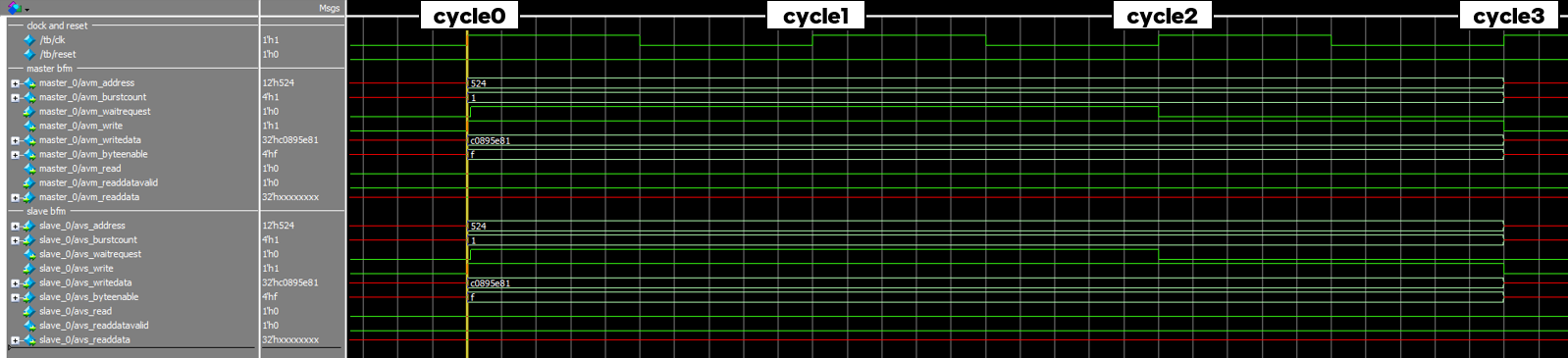

masterがwrite信号をassert (no burst) 開始位置=1.45ns

最初にavm_writeがno burstでassertされるタイミングを見てみましょう。

- cycle0: Masterはavm_address, avm_burstcount, avm_write, avm_writedata, avm_byteenableをassertします。MasterはSlaveがwritedataを受信することを期待します。少し遅れて(これはMasterが上記の信号をSlaveに送信するのと、Slaveから信号が出てくるのに遅延が生じるからです)Slaveがwaitrequestをassertします。

- cycle1: waitrequestがassertされているので、SlaveはMasterからのデータを受信完了しません。

- cycle2: ここでSlaveがwaitrequestをdeassertします。その他信号は一定です。

- cycle3: waitrequestはdeassertされているので、ようやくSlaveはMasterからのデータを受信します。

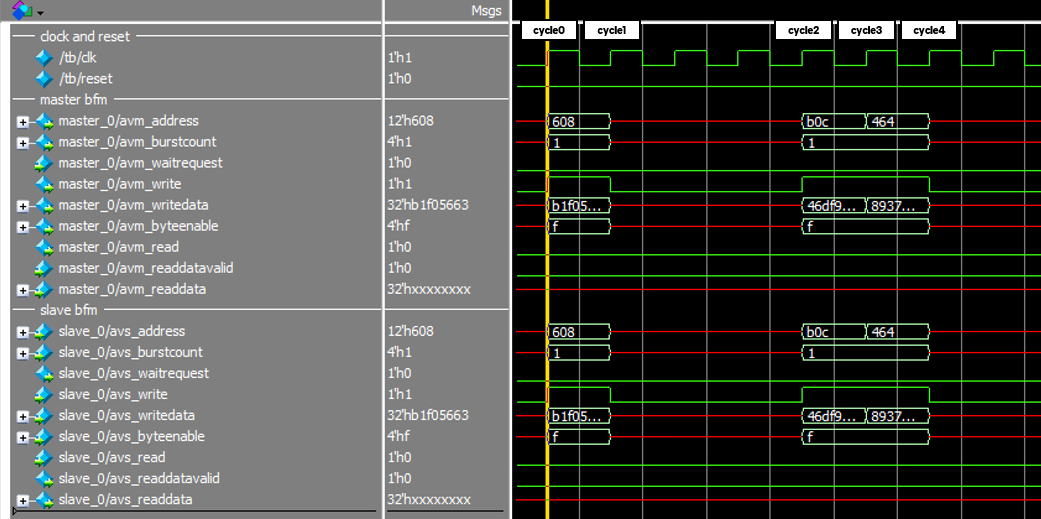

masterがread信号をassert (no burst) 開始位置=2.35ns

- cycle0: Masterはavm_address, avm_burstcount, avm_write, avm_writedata, avm_byteenableをassertします。MasterはSlaveがwritedataを受信することを期待します。

- cycle1: Slaveはwaitrequestをassertしていないので、SlaveはMasterからのデータを受信します。

- cycle2: Masterはavm_address, avm_burstcount, avm_write, avm_writedata, avm_byteenableをassertします。MasterはSlaveがwritedataを受信することを期待します。

- cycle3: Slaveはwaitrequestをassertしていないので、SlaveはMasterからのデータを受信します。同時に、Masterは次のデータを送信するために、新しいaddressとwritedataをassertします。

- cycle4: Slaveはwaitrequestをassertしていないので、SlaveはMasterからのデータを受信します。

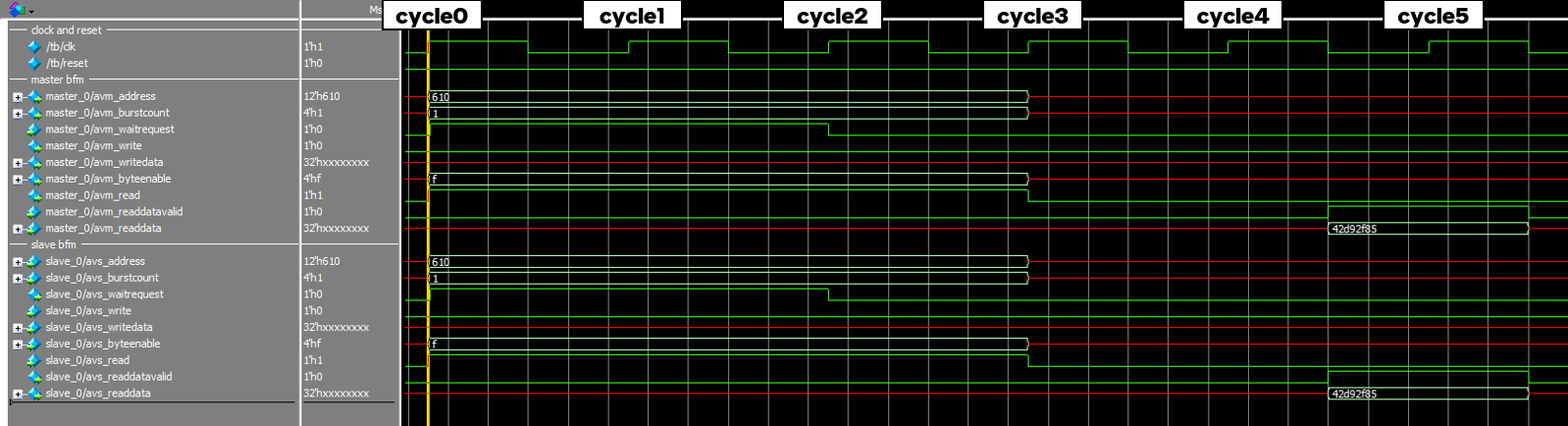

masterがwrite信号をassert (burst) 開始位置=7.25ns

- cycle0: Masterはavm_address, avm_burstcount, avm_read, avm_byteenableをassertします。MasterはSlaveがreaddataを送信することを期待します。また、少し遅れてSlaveがwaitrequestをassertします。

- cycle1: waitrequestがassertされているので、SlaveはMasterからのデータを受信完了しません。

- cycle2: waitrequestがassertされているので、SlaveはMasterからのデータを受信完了しません。Slaveはwaitrequestをdeassertします。

- cycle3: waitrequestがdeassertされているので、SlaveはMasterからavm_address, avm_burstcount, avm_read, avm_byteenableを受信します。

- cycle4: MasterもSlaveも何も信号を出していません。

- cycle5: cycle0にてMasterがSlaveに要求したデータがMasterに届きます。

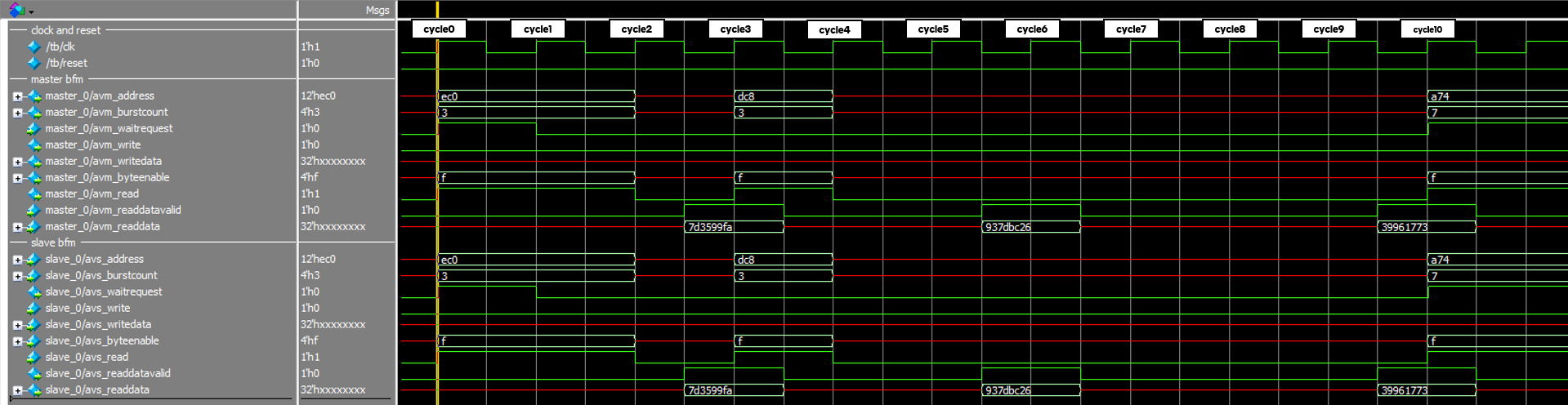

masterがread信号をassert (burst) 開始位置=32.85ns

急に見るべきcycleが増えましたが、辛抱して以下のフローを確認してください。

- cycle0: Masterはavm_address, avm_burstcount, avm_read, avm_byteenableをassertします。MasterはSlaveがreaddataを送信することを期待します。burstcount=3であることに着目してください。また、少し遅れてSlaveがwaitrequestをassertします。

- cycle1: waitrequestがassertされているので、SlaveはMasterからのデータを受信完了しません。Slaveはwaitrequestをdeassertします。

- cycle2: waitrequestがdeassertされているので、SlaveはMasterからavm_address, avm_burstcount, avm_read, avm_byteenableを受信します。

- cycle3: Masterはavm_address, avm_burstcount, avm_read, avm_byteenableをassertします。MasterはSlaveがreaddataを送信することを期待します。少し遅れてSlaveがwaitrequestをassertします。cycle0にてMasterがSlaveに要求したデータ1がMasterに届きます。

- cycle4: waitrequestがdeassertされているので、SlaveはMasterからavm_address, avm_burstcount, avm_read, avm_byteenableを受信します。

- cycle5: MasterもSlaveも何も信号を出していません。

- cycle6: cycle0にてMasterがSlaveに要求したデータ2がMasterに届きます。

- cycle7: MasterもSlaveも何も信号を出していません。

- cycle8: MasterもSlaveも何も信号を出していません。

- cycle9: MasterもSlaveも何も信号を出していません。

- cycle10: Masterはavm_address, avm_burstcount, avm_read, avm_byteenableをassertします。MasterはSlaveがreaddataを送信することを期待します。また、cycle0にてMasterがSlaveに要求したデータ3がMasterに届きます。これにより、cycle0にてMasterがSlaveに要求したデータが全てSlaveからMasterに送信されたことになります。

まとめ

さて、いかがだったでしょうか。シミュレーション結果から、Avalon® memory-mapped interfaceの動作が理解できたのではないかなと思います。

忙しいAさんと、忙しいBさんがコミュニケーションを取るためにはルール(プロトコル)が必要ということですね。IPにも同じことが当てはまり、コミュニケーションはルール化され、忙しい時には「ちょっと後にして」という信号(waitrequest)を出したり、メッセージを受け取りたい(read)のか送りたい(write)のか、などルールを理解することはとっても大事ということです。

Notices & Disclaimers

Intel technologies may require enabled hardware, software or service activation.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

https://edc.intel.com/content/www/us/en/products/performance/benchmarks/overview/