ノンブロッキング代入

実習1 シフトレジスタの設計

以下のshiftregister.vで設計される回路を実習ボードの実装して、その動作を確かめること。

ただし、top-level entity はshiftregister とする。

入出力の割り当ては表のとおりにすること。

`default_nettype none

module shiftregister(

input wire clock,

input wire data,

output reg [3:0] q

);

always @ (posedge clock) begin

q[0] <= data; // ノンブロッキング代入 <= では

q[1] <= q[0]; // これら4つの代入が

q[2] <= q[1]; // 同時に実行されるような

q[3] <= q[2]; // 回路が構築される

end

endmodule

| shiftregisterのポート | I/Oデバイス |

|---|---|

| clock | GCLK3(プッシュスイッチ) |

| data | SA0(トグルスイッチ) |

| q[3:0] | DA3~DA0(個別LED) |

解説

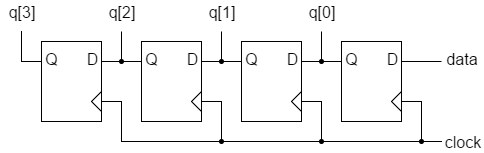

ノンブロッキング代入(<=)を用いたshiftregister.vでは、クロック信号clockの立上りのタイミングにおいて、reg型変数q[0], q[1], q[2], q[3]への4個の代入が同時にただ一度だけ実行されるような回路が構成される。その結果、回路としては下図に示すような1bitシフトレジスタが構成される。

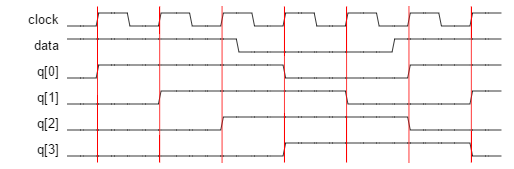

下図にこの回路の動作例をタイムチャートで示す。

ブロッキング代入

実習2 Dフリップフロップの設計

以下のdflipflop.vで設計される回路を実習ボードの実装して、その動作を確かめること。

ただし、top-level entity はdflipflop とする。

入出力の割り当ては表のとおりにすること。

`default_nettype none

module dflipflop(

input wire clock,

input wire data,

output reg [3:0] q

);

always @ (posedge clock) begin

q[0] = data; // ブロッキング代入 = では

q[1] = q[0]; // 上から下へ順に代入が

q[2] = q[1]; // 行われるような

q[3] = q[2]; // 回路が構築される

end

endmodule

| dflipflopのポート | I/Oデバイス |

|---|---|

| clock | GCLK3(プッシュスイッチ) |

| data | SA0(トグルスイッチ) |

| q[3:0] | DA3~DA0(個別LED) |

解説

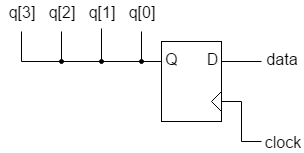

ブロッキング代入(=)を用いたdflipflop.vでは、クロック信号clockの立上りのタイミングにおいて、reg型変数q[0], q[1], q[2], q[3]への4個の代入が上の代入式から順に実行されるような回路が構成される。まず、q[0]がdataの値で更新され、次にq[1]が更新後のq[0]の値、すなわち、dataの値に更新される。同様にq[2], q[3]もdataの値に更新される。すなわち、clockの立上りのタイミングでq[3], q[2], q[1], q[0]のすべてが、dataの値で更新されるような回路が構成される。構成される回路図を以下に示す。

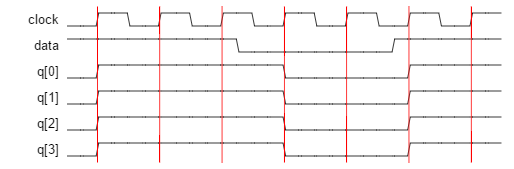

この回路の動作例を下図に示す。