概要

ビジュアルプログラミングで組み合わせ回路を組み立てて、シュミレーションして、verilogを生成します。

高位合成です。

実は、今の実装では、半加算器、全加算器が高位合成できません。

半加算器の高位合成を計画します。

設計編

半加算器を動作させて、真理値表を作る。

こちらに、simcirjsがあります。動作させて、真理値表を作成しましょう。

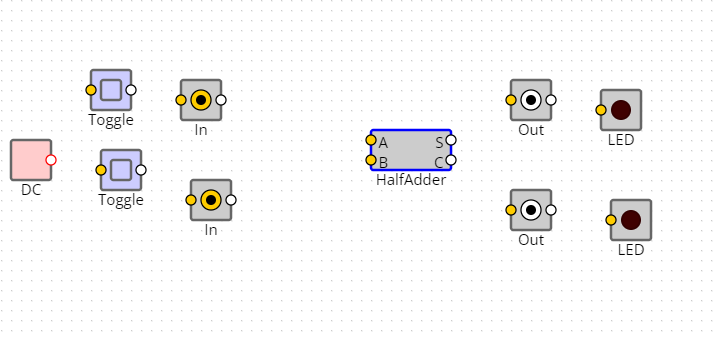

左のデバイス一覧から、HalfAdder、DC、In、Out、Toggle、LEDをドラッグします。

ワイヤーをつなぎます。

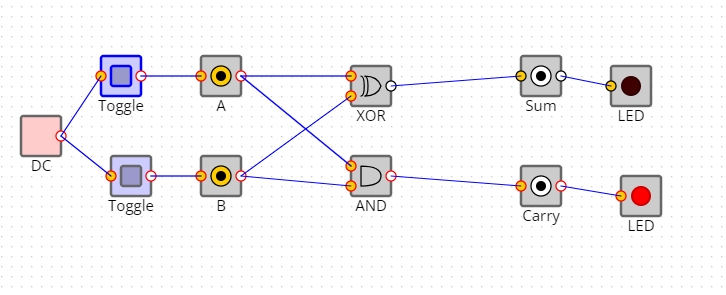

Toggleボタンを押して、シュミレーションします。

真理値表を書きます。

| A | B | Sum | Carry |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

SumはXORで、CarryはANDですね。置き換えます。

これを、高位合成するのが、目標です。

以上。