概要

高位合成言語アセンブラを作る。

練習問題、やってみた。

全加算器を作れ。

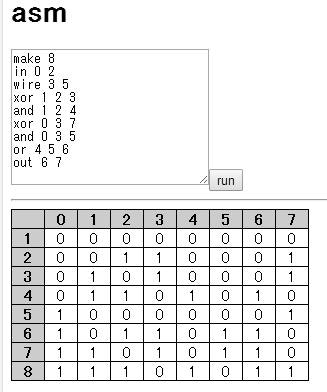

make 8

in 0 2

wire 3 5

xor 1 2 3

and 1 2 4

xor 0 3 7

and 0 3 5

or 4 5 6

out 6 7

真理値表を表示。

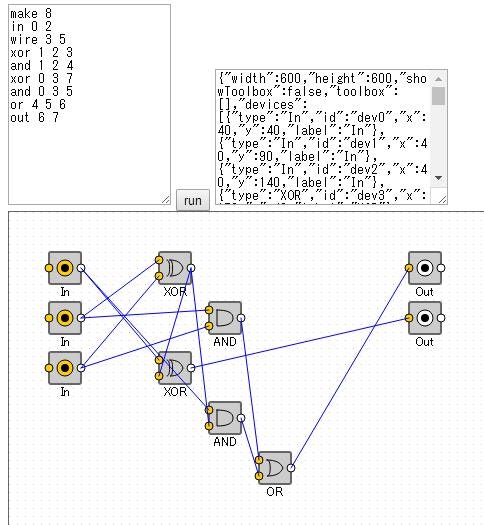

成果物

回路図を表示。

成果物

コンパイルして、verilog生成。

module x(input a, input b, input c, output g, output h);

assign d = b ^ c;

assign e = b & c;

assign h = a ^ d;

assign f = a & d;

assign g = e | f;

endmodule

module testbench;

reg a, b, c;

x u(.a(a), .b(b), .c(c), .g(g), .h(h));

initial

begin

$display("a b c g h ");

$monitor("%b %b %b %b %b ", a, b, c, g, h);

a = 0; b = 0; c = 0; #10;

a = 0; b = 0; c = 1; #10;

a = 0; b = 1; c = 0; #10;

a = 0; b = 1; c = 1; #10;

a = 1; b = 0; c = 0; #10;

a = 1; b = 0; c = 1; #10;

a = 1; b = 1; c = 0; #10;

a = 1; b = 1; c = 1; #10;

$finish;

end

endmodule

成果物

実行結果

a b c g h

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 0 1 0

1 1 1 1 1

以上。