Dr.STONE で出てきた『パラメトロン5個の加算回路』を本気で解説する

はじめに

Dr.STONE、TVアニメ第4期第3クール『Dr.STONE SCIENCE FUTURE』。見てますか。面白いですね。ストーンワールドで、コンピュータプログラマーの達人SAIが復活して、千空達は月へ向かうために、ファミコンレベルのコンピュータを作ることになりました。そのために千空が選んだのがパラメトロンという日本発の素子です。アニメでは5個のパラメトロン素子を使って、1 XOR、1 ANDの加算回路を作りました。

「なぜ5個で済むのか?」「そもそもパラメトロンって何?」を自分なりに理解したので、解説記事を作成しました。

前提条件

PC-1というパラメトロン素子を使ったコンピュータがありました。1954年に東大大学院生の後藤英一さんが発明。この名前は覚えてください。

パラメトロンってなに?(素子の物理)

トランジスタとの根本的な違い: 「電圧」ではなく「位相」で 0/1 を表す

現代の代表的素子トランジスタでは、0Vを論理0、Vcc(例えば5)Vを論理1と見なします。トランジスタの回路によって、XORやANDゲートを作成します。

パラメトロンは位相0を論理0、位相πを論理1と見なします。難しいですね。IIJの所長の書いた記事を読みましたがさっぱりでした。

もう少しかみ砕くと、

普通の電圧式デジタル回路(トランジスタ):

- 5V = 1

- 0V = 0

値は「線にかかってる電圧の高さ」

パラメトロン:

- 線には常に交流が流れている(例えば1MHzの正弦波)

- 全部のパラメトロンが同じ周波数で振動している

- ある基準のパラメトロンと 同じタイミングで揺れていれば 0

- ある基準のパラメトロンと 正反対のタイミングで揺れていれば 1

つまり「電圧の高い/低い」ではなく「波のタイミング(位相)のずれ」で情報を表します。

「基準パラメトロンが必要なのね」その理解でOKです。いまは。

まずは「ゆれ」について説明します。

ブランコの比喩: パラメータ励振の物理現象

ブランコをこいでいる時ですが、一番低い点の時には足を折りたたみ、前方の一番高い点で足を伸ばして弾みをつけます。また、後方の一番高い点で後ろに体を動かして弾みをつけます。

このように1回の往復で2回力を加えることによって、どんどん振り幅を大きくします。

これは以下のような関係にあります。

- ブランコの揺れ = 周波数 f

- 弾みをつける動作 = 周波数 2f

これが 「パラメータ励振」 という現象の本質です。「パラメータ(=振り子の長さ)」を「励振(=揺さぶる)」する、という意味です。

そして大事なポイント:

「2f で揺さぶる」と、「f の振動」が成長する

これは数学的にもちゃんと証明できる現象で、専門用語では「マシュー方程式の不安定領域」と呼ばれますが、名前は忘れてOKです。「2倍の周波数で揺さぶると、半分の周波数で勝手に振動が育つ」、これだけ覚えてください。

LC共振回路を 2f で揺さぶると f の振動が育つ

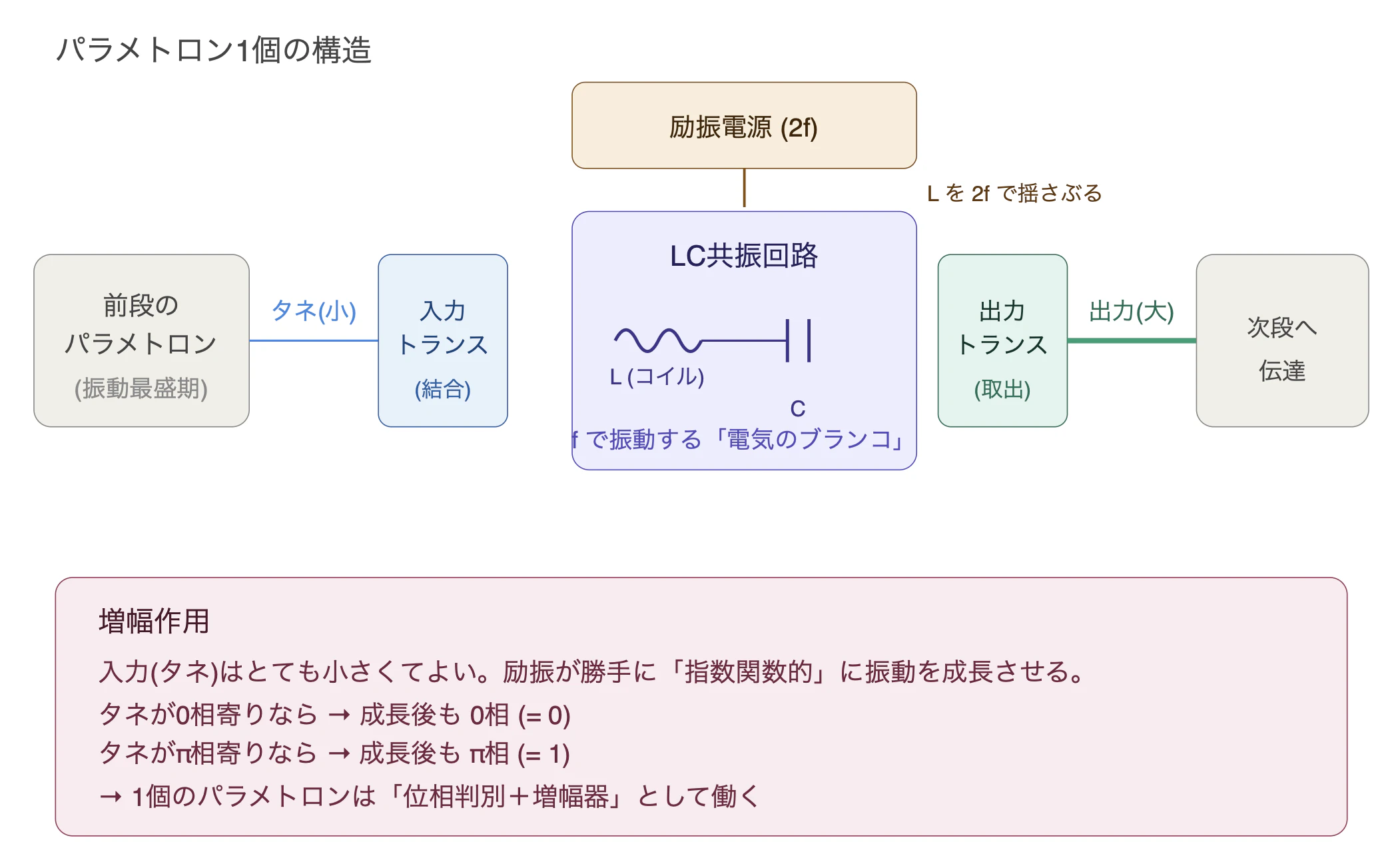

パラメトロンの実体は、フェライトコアに巻かれたコイルとコンデンサを組み合わせたLC共振回路です。

LC共振回路:コイル(L)とコンデンサ(C)を組み合わせた回路。一定の周波数 f で電気的に振動する性質がある。これがブランコの「振り子」に相当します

この回路に、2f の励振電流を流します。すると回路の中で何が起こるか?

- コイル L のインダクタンス(電気的な「振り子の長さ」みたいなもの)が、励振電流の影響で周期的に変動する

- 変動の周波数 = 励振電流の周波数 = 2f

- つまり「振り子の長さが 2f で変動するブランコ」になる

これはまさにブランコこぎと同じ状況です。

その結果:

- f の電気振動が勝手に育っていく

これがパラメトロンが「振動する」原理です。LC回路という「電気のブランコ」に、2f の漕ぎを加えると、f の振動が育つ ── 物理現象そのままです。

「タネ」と「増幅作用」: 弱い入力を勝手にフルスイングまで育てる

ブランコをただ揺さぶっているだけでは、最初に「前向きに揺れるか後ろ向きに揺れるか」決まりません。 50:50 のランダムです。

ところが、揺さぶる前にちょっとだけ前向きに押してあげると、その方向で揺れが成長します。後ろ向きに押せば、後ろ向きに育ちます。

物理的に言えば:

- 励振が始まる前の 「初期のごく小さな振動」 が、成長後の位相を決める

- 初期振動が 0相寄りなら → 成長後も 0相

- 初期振動が π相寄りなら → 成長後も π相

- そして、初期振動はものすごく小さくてもいい。励振が勝手に増幅してくれるから

「ものすごく小さくてもいい」という部分が増幅作用です。

数値で言うと:

- 初期の「タネ」は、成長後の振動の 1/100 とか 1/1000 くらいの大きさでも十分

- パラメトロンが励振されると、指数関数的に振動が成長する

- 成長は、回路の損失と励振の強さで決まる「飽和レベル」で止まる

つまり1個のパラメトロンは:

- 入力の100倍〜1000倍の出力を、勝手に作る増幅器

になっています。これがあるから、論理ゲートを縦にいくらでも繋げます。前段の出力を後段の入力にしても、信号がどんどん減衰していくということがない。1段ごとに勝手に再生されます。

基準パラメトロンはどうやって作るか

実は、パラメトロン方式の核心部分で、「基準パラメトロンは作らない」 が答えです。落ち着いて聞いてください。説明します。

基準は「励振電源」そのもの

パラメトロン全体を動かすために、外から 2f の交流電源(励振電源)を供給します。これが共通の基準クロックです。

- パラメトロンの共振周波数を f とすると

- 励振電源は その2倍の周波数 2f で全パラメトロンに供給

- この励振電源の波形が 絶対的な「時間の基準」

すべてのパラメトロンはこの2f電源を「揺さぶり」として受け取って、自分の中で f の振動を作ります。

でも、0相とπ相のどちらが「0」かは決められない

励振電源は「2f」なので、1周期に2回揺さぶります。パラメトロンの振動は f なので、励振の1周期に対して、パラメトロンは半周期しか進まない。

つまり、励振電源の山が来たときに、パラメトロンが上向きで応答するか、下向きで応答するかは、物理的にはどちらも等価で、励振電源だけからは決まりません。

ブランコでたとえると ── ブランコを揺さぶる人は「漕ぐリズム」だけ提供する。でも前向きに揺らすか後ろ向きに揺らすかは、ブランコの最初の微妙なズレ次第。

これが「0 と π はどちらも安定状態で、対称」というパラメトロンの性質です。

では「これが 0 だ」をどう決めるのか? ── 答え:相対的に決める

ここが本質です。絶対的な「0 を表す基準パラメトロン」は存在しません。

代わりに、こうします:

「常に 0 を出力するパラメトロン」と「常に 1 を出力するパラメトロン」を、回路の中に常時配置しておく。

具体的には:

- 常時0パラメトロン = 入力に何もつながず、ただ励振されているだけのパラメトロン。電源投入時にどちらかの位相に落ちる。これを 「これが 0 だ」と人間が定義する

- 常時1パラメトロン = 常時0パラメトロンの出力を、逆向きに巻いた線で受け取る。すると位相が反転して常に π相 = 1 になる

つまり「0」は 任意に決めた基準点で、「1」は「0をひっくり返したもの」として相対的に定義されます。

電源投入時の位相は、どうやって決まるのか?

「常時0パラメトロン」が電源投入時に 0相になるか π相になるかは、理論的には50:50のランダムです。これを困った問題と思うかもしれませんが、解決策はシンプルで:

電源投入直後に、外から強制的に「タネ」を注入して位相を確定させる

PC-1 では、起動シーケンスで明示的に「ここが基準だ」と決め打ちする回路があります。その位相を起点に、回路全体の 0/1 が伝播していきます。

ブランコでたとえると ── 公園のブランコ100台を一斉に揺らし始める時、誰か1人が「このブランコは前向きから漕ぎ始めるぞ!」と最初に押す。そのブランコが「0の基準」になり、他のブランコは順次連鎖的にタイミングを揃えていく。

もう一つの大事な仕組み ── 3相励振

実は1個の基準パラメトロンだけだと、信号が伝わりません。なぜなら A → B → C と伝えたいとき、AとBが同時に振動していたら、AからBへ位相情報を伝える「タイミング」が取れない からです。

そこでパラメトロンは 3つのグループ(Phase I, II, III) に分けて、順番に励振 → 休止 → 励振 → 休止 を回します。

Phase I のパラメトロンが共振している間に、その位相が Phase II のパラメトロンに種として伝わり、Phase II の励振が始まると、引き継いだ位相で発振する

これによって、

- Phase I が振動 → 休止

- Phase II が振動(Iの位相を引き継いで)→ 休止

- Phase III が振動(IIの位相を引き継いで)→ 休止

- 再び Phase I へ

という3拍子のクロックで信号が伝播します。これが現代のCPUの「クロック」に相当する仕組みです。

基準パラメトロンが3相ということは、最低3つのパラメトロンがベースとして必要ということ?

結論を先に言うと:

「基準(参照用)パラメトロン」と「3相励振」は別の話です。

混ざりやすいので、ひとつずつ分けます。

区別すべき2つの「基準」

-

基準A:論理的な基準(0 を表す参照点)

「どっちの位相が 0 か」を決めるための参照点。 -

基準B:時間的な基準(信号を順送りする仕組み)

信号を A → B → C と伝えるためのクロック。

それぞれ何個必要か?

基準A(論理的基準)── 原理的には 1個で足りる

「これが 0 だ」と決めるためのパラメトロンは、論理的には1個あれば十分です。多くの場合、それすら専用に置かず、「入力を全部0に固定したパラメトロン」を必要な場所に都度作るだけです。

つまり基準Aは、原理的に常駐させる必要はなく、必要に応じて作ればいい。1個でも100個でもよくて、全部の常時0パラメトロンは「同じ位相」で揃うように電源投入時に同期させます。

基準B(時間的基準=3相励振)── これは原理的に必要

こちらは PC-1 の都合ではなく、パラメトロンという素子の物理的な必然です。

なぜか?

「あるパラメトロンが、自分の位相を次のパラメトロンに伝える」 という動作は、送り手と受け手が同時に振動していてはできない からです。

ブランコの比喩で言うと:

自分が全力で漕いでいるブランコAに乗りながら、隣のブランコBを「同じリズムで漕ぎ始めて」と押すには、自分のブランコがゆっくり減速しているタイミングで、Bに優しく押し出してあげる必要がある。Aが全力で揺れている瞬間にBに触ろうとすると、Bを蹴飛ばしてしまうか、自分が止まってしまう。

なので、

- 送り手(Phase I)が振動の最盛期に位相情報を確立し、

それが減衰して休止に向かうフェーズで、 - 受け手(Phase II)が励振開始 ── 弱い「タネ」を受け取ってゼロから成長

という時間差が必要です。これを成立させるには、最低でも振動 → 休止 → 振動 のサイクルを区別できる仕組みが要ります。

「3相」でなければダメ?

「3相」は最小ではなく、最も実用的な数です。

理論的には:

- 2相でも動く ── ただし、I が休止に入る瞬間に II が立ち上がる、というギリギリの動作になり、タイミングマージンがゼロに近い。励振電源のスイッチング誤差や素子バラツキで簡単に破綻します。

- 3相だと余裕がある ── I が振動最盛期、II が立ち上がり、III が休止、という3状態が常に1つずつ存在するので、信号が「次のフェーズへ余裕をもって渡される」ことが保証されます。さらに、I → II → III → I に戻ってくるまでに2ステップ分の遅延があるので、組み合わせ回路を作るときに信号の通り道を3拍子で計画できる。

- 4相以上でも動くが、回路は無駄に遅くなる。

つまり、

「3相」は物理的最小限ではなく、信号性が安定する最小の数

ということです。後藤英一さんが3相を選んだのは、当時の素子バラツキや励振電源の精度を考えると、2相は危険、4相は遅すぎるという工学的判断です。

3相励振は何個のパラメトロンを使うのか?

「3相だから3個」ではありません。

全部のパラメトロンを3つのグループに分けて、グループ単位で励振電源をオン/オフします。

PC-1 の場合:

- 約4,200個のパラメトロン全部

- これを Phase I, II, III の3グループに振り分け

- 各グループに専用の励振電源線が3本走っている

- 励振電源は3本の線に位相をずらして交流を流す

- 結果、1,400個ずつくらいが同じタイミングで振動 → 休止 → 振動を繰り返す

つまり、3相励振のために追加のパラメトロンが要るわけではなく、もともとあるパラメトロンを3グループに分けるだけです。コストは「励振電源を3系統用意する」ことだけです。

2fの3相交流電源が一つあれば、phase I/II/IIIのパラメトロンが作れますか

2f の3相交流電源が1つあれば、それで Phase I/II/III のパラメトロンを全部駆動できます。

これがパラメトロン方式のシステム設計上のシンプルさで、実際 PC-1 もまさにこの構成です。

実際には電力用の3相交流電源では無く、3本の励振線を出力する電源装置です。

構成イメージ

電源装置(真空管発振器)が1台あって、そこから3本の励振線が出ます:

- 励振線A:2f の交流(位相 0°)→ Phase I のパラメトロン全部に接続(約1,400個)

- 励振線B:2f の交流(位相 120°ずれ)→ Phase II のパラメトロン全部に接続

- 励振線C:2f の交流(位相 240°ずれ)→ Phase III のパラメトロン全部に接続

3本の励振線を機械の中に張り巡らせて、各パラメトロンは「自分はどの相に属するか」によって、3本のうち1本にだけ接続される、というだけです。

Phase I の励振線は「2.2MHz の波が一定時間 → 休止 → また一定時間 → 休止」というパターンになります。つまり、

- 搬送波が 2.2MHz

- オン/オフのサイクルが約 30kHz(PC-1 の動作周波数)

という二段構えの波形です。励振がオンの間は普通に2.2MHzで揺さぶる、オフの間は何もしない、という変調が3つの線で順送りされます。

初期の「タネ」はどうやって与えるか

具体的には、パラメトロンには入力トランスという部品がついています。

3つの前段パラメトロンの出力を1個のパラメトロンに集めるように配線します。

時間軸で「タネ」はいつ受け取られるか

Phase II のパラメトロンが「休止 → 振動」へ立ち上がる瞬間に、何が起こっているか時系列で追ってみます:

| 時刻 | Phase I | Phase II | 何が起こっているか |

|---|---|---|---|

| t1 | 振動最盛期 | 休止 | I の出力が大きく振動。II は静か。 |

| t2 | 振動最盛期 | 励振開始直前 | I の出力線から、II の入力トランスに小さな電流が流れ込む。これが「タネ」 |

| t3 | 減衰中 | 励振開始 | II の励振電源がオン。LC回路がタネを引き継いで成長を始める |

| t4 | 休止に向かう | 振動成長中 | II の振動が指数関数的に大きくなる |

| t5 | 完全に休止 | 振動最盛期 | II が位相を確定。次は III に向かってタネを送る側になる |

ポイントは:

タネを受け取るタイミングは「II が休止から立ち上がる瞬間」だけ

II が完全に振動してしまった後では、もうタネは効きません。「位相が確定する前のごく短い時間」だけが、入力を受け付ける窓です。

これがあるから、3相励振が必須でした。「Iがまだ振動していて出力が出ている」かつ「IIがちょうど休止から立ち上がる」というタイミングが揃わないと、信号が伝わらない。

3相だと、この「振動中グループ」と「立ち上がり中グループ」が常に存在するので、信号が途切れず順送りされる、というわけです。

「ものすごく小さなタネ」が自動的に増幅される ── これがすごい

ここでパラメトロンの最大の利点を強調します。

普通のデジタル回路(トランジスタ)では:

- 信号は「電圧」で伝わる

- 何段も論理ゲートを通すと、配線抵抗や容量で信号が減衰する

- だから途中に**バッファ(増幅器)**を入れる必要がある

パラメトロンでは:

- 信号は「位相」で伝わる

- 1個のパラメトロンを通るたびに自動的に増幅される

- 何段繋げても信号が減衰しない(むしろ常にフルスイングに再生される)

この性質を「信号再生効果」と言います。後藤英一氏が論文で強調していた、パラメトロンのキラー機能です。

別の言い方をすると:

「タネは方向だけ伝えればよく、強さは関係ない」

これは情報理論的に見るとアナログ的な性質を持ちながら完全にデジタル動作する、という不思議な素子です。位相という連続量で情報を表しているのに、結果は0かπの2状態しか取らない。

パラメトロン素子のまとめ

- 2f で揺さぶると f が育つ(パラメータ励振という物理現象)

- LC共振回路を 2f の電流で揺さぶることで実現(電気のブランコ)

- 初期の小さな「タネ」が成長後の位相を決める(位相判別)

- タネは何百倍にも増幅される(増幅作用)

- タネを受け取るのは「休止から立ち上がる瞬間」だけ(タイミング窓)

- 何段繋げても信号は減衰せず、常に再生される(信号再生効果)

多数決論理 (パラメトロンの強み)

波の重ね合わせ = 多数決演算

これだけは押さえておきたい物理現象です:

2つの波が同じ場所で出会うと、振幅は単純に足し算される。

- 同じ向きの波同士 → 強め合う(振幅が2倍)

- 逆向きの波同士 → 打ち消し合う(振幅がゼロ)

これは波打ち際で2つの波がぶつかったり、音響の実験で2つのスピーカーから同じ周波数を出したりすると見られる、ごく普通の物理現象です。

パラメトロンは0相とπ相の2つしか位相を取らないので、波の足し算は次の3パターンに集約されます:

| 波A | 波B | 重ね合わせの結果 |

|---|---|---|

| 0相(↑) | 0相(↑) | 0相(強さ2倍) |

| π相(↓) | π相(↓) | π相(強さ2倍) |

| 0相(↑) | π相(↓) | 打ち消し合ってゼロ |

3つの波を重ねるとどうなるか?

入力トランスのところで、「3つの前段パラメトロンの出力を1個のパラメトロンに集める」という配線をすると説明しました。

3つの波 a, b, c を重ねると:

| a | b | c | 合成波 |

|---|---|---|---|

| 0 | 0 | 0 | 0相 × 3 → 0相(最大の強さ) |

| 0 | 0 | 1 | 0相 × 2 + π相 × 1 → 1個分が打ち消されて、0相(弱め) |

| 0 | 1 | 0 | 同上 → 0相(弱め) |

| 1 | 0 | 0 | 同上 → 0相(弱め) |

| 0 | 1 | 1 | 0相 × 1 + π相 × 2 → π相(弱め) |

| 1 | 0 | 1 | 同上 → π相(弱め) |

| 1 | 1 | 0 | 同上 → π相(弱め) |

| 1 | 1 | 1 | π相 × 3 → π相(最大の強さ) |

合成波の位相だけ取り出して並べ替えると:

| a | b | c | 合成波の位相 |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

これですが、

3入力の多数決:1が多ければ1、0が多ければ0

論理関数として書けば:

MAJ(a, b, c) = (a・b) + (b・c) + (a・c)

これがそのまま実現されています。わざわざANDやORを組み合わせる必要なし。波の干渉だけで多数決ができます。

増幅作用が「弱い多数決」を「強い断定」に変える

上の表で、合成波には「強い0相」と「弱い0相」がありました。3:0 で揃ったときと、2:1 で勝ったときでは、合成波の強さが違います。

ところが ── ステップ2で説明した通り、パラメトロンは入力の強さを無視して、位相だけを取り出して増幅します。

これが重要です。

タネが弱くても強くても、励振が勝手にフルスイングまで成長させる

なので、2:1で僅差で勝ったときでも、3:0で圧勝したときでも、出力は同じ「フルスイングの 0相」。これがあるから、後段でも同じ強さで信号が届き、何段でも繋がっていけます。

「弱い多数決」が「強い断定」に変わる ── パラメトロンの増幅作用が、論理回路として完璧に機能する理由です。

1個で AND/OR/NOT/MAJ がぜんぶ作れる (入力固定 + 巻線反転)

3入力多数決ゲートで、1入力を固定すれば AND と OR が作れます。

AND を作る場合:1入力を 0 に固定

| a | b | 0(固定) | MAJ = a AND b |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 |

OR を作る場合:1入力を 1 に固定

| a | b | 1(固定) | MAJ = a AND b |

|---|---|---|---|

| 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 |

NOT を作る場合:入力線を逆向きに巻く

トランスの巻線を逆にするだけ。物理的には信号の符号を反転させるだけなので、ゲートとして数える必要すらありません。

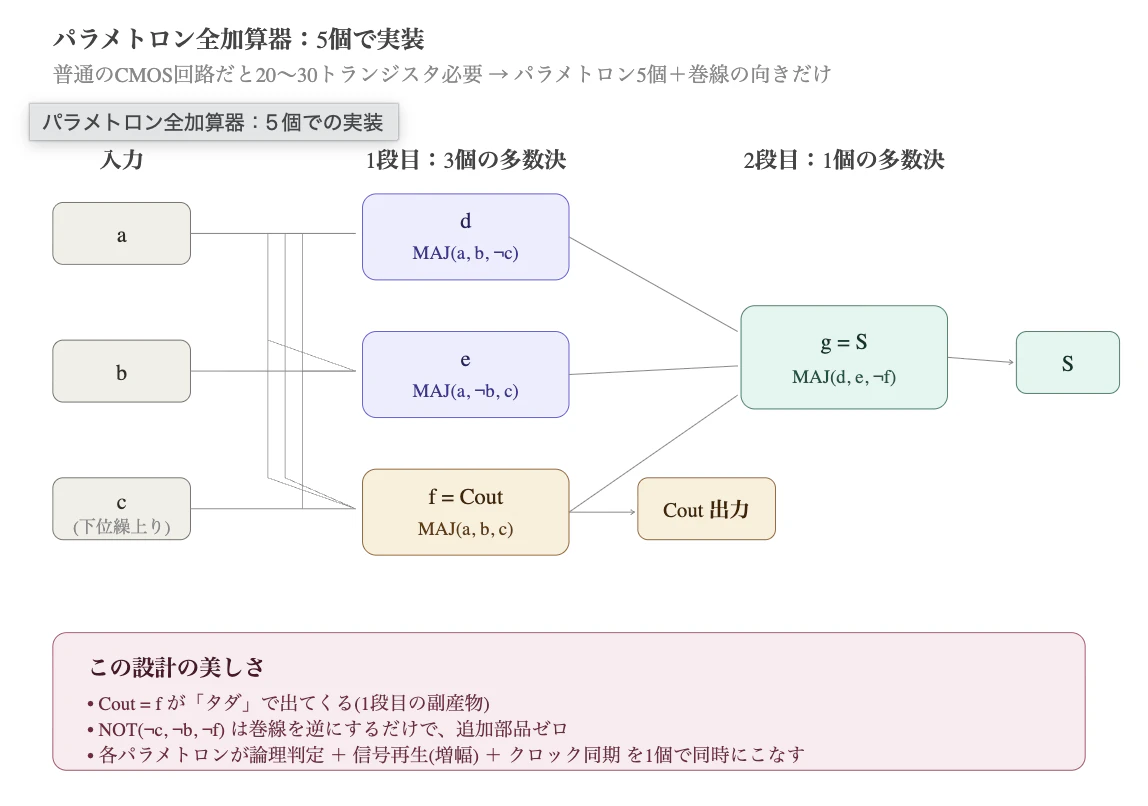

5個で全加算器 (山田の回路)

CY(桁上がり)= AND

ここで、SAIが説明した「ANDとXORで加算回路ができる」を思い出してください。

普通のデジタル教科書だと、全加算器はこう書かれます:

- 和 S = a XOR b XOR c

- 桁上がり Cout = (a AND b) OR (b AND c) OR (a AND c)

桁上がりの式をよく見てください:

- Cout = (a AND b) OR (b AND c) OR (a AND c)

これは実は3入力多数決そのものです。つまり:

Cout = MAJ(a, b, c)

1個のパラメトロンで桁上がりが完成します。普通の回路だと AND × 3 + OR × 2 で 5 ゲート要るのに、たった1個です。

3入力 XOR は1段の多数決では作れない (Knuth の定理)

問題は和 S の方です。

- S = a XOR b XOR c

XOR は「奇数個の 1 があれば 1」という関数です:

| a | b | c | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

この関数は 1段の多数決では絶対に作れません。

なぜか? 多数決は本質的に「単調」な関数です。入力の1の数が増えれば、出力は0から1に向かって変化していくだけ。一方 XOR は、入力の1の数が増えると 0 → 1 → 0 → 1 と振動します。単調じゃない関数は1段の多数決では実現不可能、というのが定理です。

ここで山田博氏の天才性が発揮されます。

山田博氏の発見: 2段の多数決で XOR が作れる

まずは図を見てください。

1段目の3つのパラメトロン:

- d = MAJ(a, b, ¬c) (c だけ反転)

- e = MAJ(a, ¬b, c) (b だけ反転)

- f = MAJ(a, b, c) (反転なし → これがそのまま Cout)

f はもう既に桁上がりです。

問題は d と e。これが何を意味しているか、真理値表で見てみましょう。

| a | b | c | d=MAJ(a,b,¬c) | e=MAJ(a,¬b,c) | f=MAJ(a,b,c) |

|---|---|---|---|---|---|

| 0 | 0 | 0 | MAJ(0,0,1)=0 | MAJ(0,1,0)=0 | 0 |

| 0 | 0 | 1 | MAJ(0,0,0)=0 | MAJ(0,1,1)=1 | 0 |

| 0 | 1 | 0 | MAJ(0,1,1)=1 | MAJ(0,0,0)=0 | 0 |

| 1 | 0 | 0 | MAJ(1,0,1)=1 | MAJ(1,1,0)=1 | 0 |

| 0 | 1 | 1 | MAJ(0,1,0)=0 | MAJ(0,0,1)=0 | 1 |

| 1 | 0 | 1 | MAJ(1,0,0)=0 | MAJ(1,1,1)=1 | 1 |

| 1 | 1 | 0 | MAJ(1,1,1)=1 | MAJ(1,0,0)=0 | 1 |

| 1 | 1 | 1 | MAJ(1,1,0)=1 | MAJ(1,0,1)=1 | 1 |

2段目のパラメトロン:

- g = MAJ(d, e, ¬f)

これも計算してみましょう。

| a | b | c | d | e | f | ¬f | g=MAJ(d,e,¬f) | 期待値S=a⊕b⊕c |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | MAJ(0,0,1)=0 | 0 ✓ |

| 0 | 0 | 1 | 0 | 1 | 0 | 1 | MAJ(0,1,1)=1 | 1 ✓ |

| 0 | 1 | 0 | 1 | 0 | 0 | 1 | MAJ(1,0,1)=1 | 1 ✓ |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | MAJ(1,1,1)=1 | 1 ✓ |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | MAJ(0,0,0)=0 | 0 ✓ |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | MAJ(0,1,0)=0 | 0 ✓ |

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | MAJ(1,0,0)=0 | 0 ✓ |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | MAJ(1,1,0)=1 | 1 ✓ |

全部一致! 山田の回路は本当に正しく XOR を計算しています。

NOT は巻線の向きで実現 → 追加部品ゼロ

パラメトロン加算回路のまとめ

1個1個のパラメトロンが何をしているかをまとめると:

1個のパラメトロンは、3つの仕事を同時にやっている素子

- 論理ゲート:入力の波を重ね合わせて、多数決の結果を位相として取り出す

- 増幅器:弱いタネを強い出力に育てる

- クロック同期:3相励振に従って、タイミング良く前段→後段へ信号を渡す

普通の半導体回路だと、これは別々の部品:

- 論理ゲート(NANDなど)

- バッファ(信号再生)

- フリップフロップ(クロック同期)

パラメトロンは、これらが1個に統合されています。これが、半導体が未熟だった1950年代の日本において、計算機を作るための合理的な選択だった理由です。素子の数が圧倒的に少なくて済みます。

Dr.STONEでは?

ここまで理解できると、千空とSAIたちが「20万個のパラメトロン」と言った数字の意味も分かってきます。

- 1ビット全加算器 = 5個

- 16ビット加算器 = 80個(×16桁)

- レジスタ、メモリ、制御回路を含めて、ちゃんとしたコンピュータを作るには、最低でも数千〜数万個のパラメトロンが必要

- 千空たちの目標規模なら 20万個は妥当な数

そして、これをストーンワールドで作る難しさは:

- フェライトコア20万個(高精度な焼結が必要)

- 巻線40万本以上(人海戦術)

- 励振電源1台(実は最大の難所 ── 真空管か半導体が必要)

- 配線の総延長は数キロメートル

現実のパラメトロンコンピュータのひとつ(PC-2)では1万3000個のパラメトロンを使っていて、回路図を見ながら1本1本結線したらしいのですが、20万個ともなると確かに杠さん率いる手芸部の出番です。

ここまでのまとめ

パラメトロン素子5個で、加算回路ができることがわかりました。Dr.STONEの調査力には脱帽です。ここから先は、さらに深い話になります。付いてきてください。

おまけ1: 5個のパラメトロンをphase I/II/IIIに割り当てるには、適当でいいのですか

結論から言うと:

「適当」ではダメで、明確なルールがあります。 ただし、複雑なルールではなく、1個のシンプルな原則だけです。

ルール:信号の流れに沿って I → II → III → I → II → III ... と順番に割り当てる

これだけです。シンプルですが、これを破ると回路は動きません。

なぜか? 説明した通り、パラメトロンは「振動中のグループから、休止から立ち上がるグループへ、タネを伝える」という時間順送りの仕組みで動いています。

つまり:

- Phase I のパラメトロンの出力は、Phase II のパラメトロンの入力にしか繋げない

- Phase II の出力は、Phase III の入力にしか繋げない

- Phase III の出力は、Phase I の入力にしか繋げない

これを破ると、「振動中のパラメトロンに信号を入れようとする」ことになってしまい、タネが効きません。

山田の回路に当てはめてみる

5個のパラメトロンを信号の流れ順に並べると:

| パラメトロン | 入力 | 出力 |

|---|---|---|

| d, e, f(1段目の3個) | a, b, c(外部入力) | 1段目出力 |

| g(2段目) | d, e | 2段目出力(=和S) |

| f(→外部) | (上記と同じ) | Cout |

割り当ては:

- a, b, c の信号源 ← Phase I に置く(または外部から Phase I 相当のタイミングで入力)

- d, e, f(1段目) ← Phase II

- g(2段目) ← Phase III

これが正しい割り当てです。

ここで「困った問題」が発生する

実は、ここから話が一気に深くなります。この質問は本質を突いていて、実装上の最大の悩みどころを引き出しています。

問題1:3段以上の論理を組むには?

論理回路では、3段で足りないこともあります。例えば10段の組合せ回路を作ろうとすると:

I → II → III → I → II → III → I → II → III → I

と、Phaseが10回循環します。これは原理的にOKです。問題はないんです。3相は周期的にいくらでも繰り返せるので、深い論理回路でも問題なく組めます。

問題2:信号を「2段先」に送りたい時

例えば「Phase I の出力を、Phase II をスキップして直接 Phase III に送りたい」というケース。

これはできません。なぜなら、Phase III が休止から立ち上がる瞬間に、Phase I はもう休止に入っているので、タネが届かないからです。

回避策:間に「中継だけのパラメトロン」を Phase II に置きます。論理的には何もしない(=入力をそのまま出力する)パラメトロンを挟むだけです。これを 「遅延パラメトロン」 や 「中継パラメトロン」 と呼びます。

Phase I の信号 → (Phase II の中継パラメトロン) → Phase III に到着

説明した「1個のパラメトロンが論理ゲート+増幅器+クロック同期」という性質のうち、クロック同期だけ使う使い方ですね。

問題3:信号を「同じPhase内」で複数のパラメトロンに配りたい時

例えば、a の信号を d, e, f の3個に同時に配るケース(山田の回路でまさにこれ)。

これは全く問題ありません。1個のパラメトロンの出力を、複数の次段パラメトロンの入力に並列に繋げばOK。ファンアウトと呼ばれる、普通のデジタル回路と同じ概念です。

ただし制限があります:

- ファンアウト数は素子の特性による。PC-1 では1個のパラメトロンの出力で約10個の次段パラメトロンを駆動できた(らしい)

- 多すぎると、出力電流が不足してタネが弱くなりすぎる

問題4:論理が複雑になって「Phase の循環」が合わなくなる時

これが最も厄介な実装上の問題です。具体例で見てみましょう。

例えば、ある信号 X を:

- 経路A: Phase I → II → III と3段かけて作る

- 経路B: Phase I → II と2段で作る

この2つを最後にまた合流させたい場合、経路Aは Phase III から出てきて、経路Bは Phase II から出てきます。Phase が違うので合流できません。

解決策:経路Bの最後に遅延用の中継パラメトロン(Phase III)を1個追加して、経路Aと経路Bの Phase を揃える。

これが、実機のパラメトロン計算機で大量の「遅延だけが目的のパラメトロン」が必要になる理由です。論理的には不要なのに、Phaseのタイミングを揃えるためだけに追加されるパラメトロンが、しばしば回路全体の半分近くを占めることもあります。

PC-1 が4,200個も使っていた、PC-2 が13,000個も使っていた、その内訳を見ると、実は論理を担当しているパラメトロンは半分以下で、残りは遅延・中継・電源用だった、というのも珍しくありません。

問題5:「逆向きに信号を送る」ことができない

普通のデジタル回路だと、フィードバックループ(出力を入力に戻す)でフリップフロップ(記憶素子)を作ったりします。

パラメトロンでも記憶を作れますが、Phase III の出力を Phase I に戻す形で「3個1組」のループを作る必要があります:

Phase I → Phase II → Phase III → Phase I(同じ場所に戻る)

3個のパラメトロンを輪っか状につないで、信号がぐるぐる回り続けることで「1ビット記憶」になります。つまり1ビットのレジスタ = 3個のパラメトロン。これがメモリ系で大量のパラメトロンを使う理由です。

まとめると、Phase 割り当ての法則

| 状況 | ルール |

|---|---|

| 適当に割り当てていいか? | いいえ。明確なルールがある |

| ルールは何か? | 信号の流れに沿って I → II → III → I → II → III ... の順 |

| 同じ Phase 内の通信 | 不可能 |

| 1段飛ばしの通信 | 不可能。中継パラメトロンが必要 |

| 同 Phase 内のファンアウト(並列配信) | OK(素子の駆動能力の範囲内) |

| Phase を逆方向(III → II など)に流す | 不可能 |

| ループを作りたい | 3個1組で I → II → III → I で輪を作る |

山田の回路の場合、実は…

これを踏まえて改めて山田の回路を見ると、設計の巧妙さが分かります。

- 入力 a, b, c は同じ Phase(=前段から同じタイミングで来る)

- 1段目の d, e, f は次の Phase

- 2段目の g はそのさらに次の Phase

- f は1段目(中間 Phase)から取り出して、そのまま Cout として外部出力

これがすごいのは、

Cout が「2段目の Phase まで待たずに、1段目で確定する」

ということ。つまり次の桁の加算回路は、こちらの2段目の計算が終わるのを待つ必要がなく、Cout が決まった瞬間に次の桁の加算を始められる。

これがパラメトロン計算機の高速化技法 「桁上げ先回り」 の基礎になります。後藤英一氏が誇った高速桁上げ回路の仕組みも、根っこはこの「Phase をうまく使った時間設計」です。

なるほどシステム設計だ

ここまで来ると、パラメトロン計算機の設計が

「論理設計」と「Phase 設計」を同時にやる作業

だということが分かります。普通のデジタル回路は論理だけ考えればよく、配線の遅延は後から調整するもの。ところがパラメトロンは、最初から3相のタイミングを織り込んで論理を書く必要があります。

これが、SAIが「壁一面に16進数の手書きアセンブリを書く」シーンの背景にある、計算機設計の本質的な複雑さです。論理を書くだけでなく、3拍子のリズムに合わせて全部の演算をスケジュールする仕事が必要です。

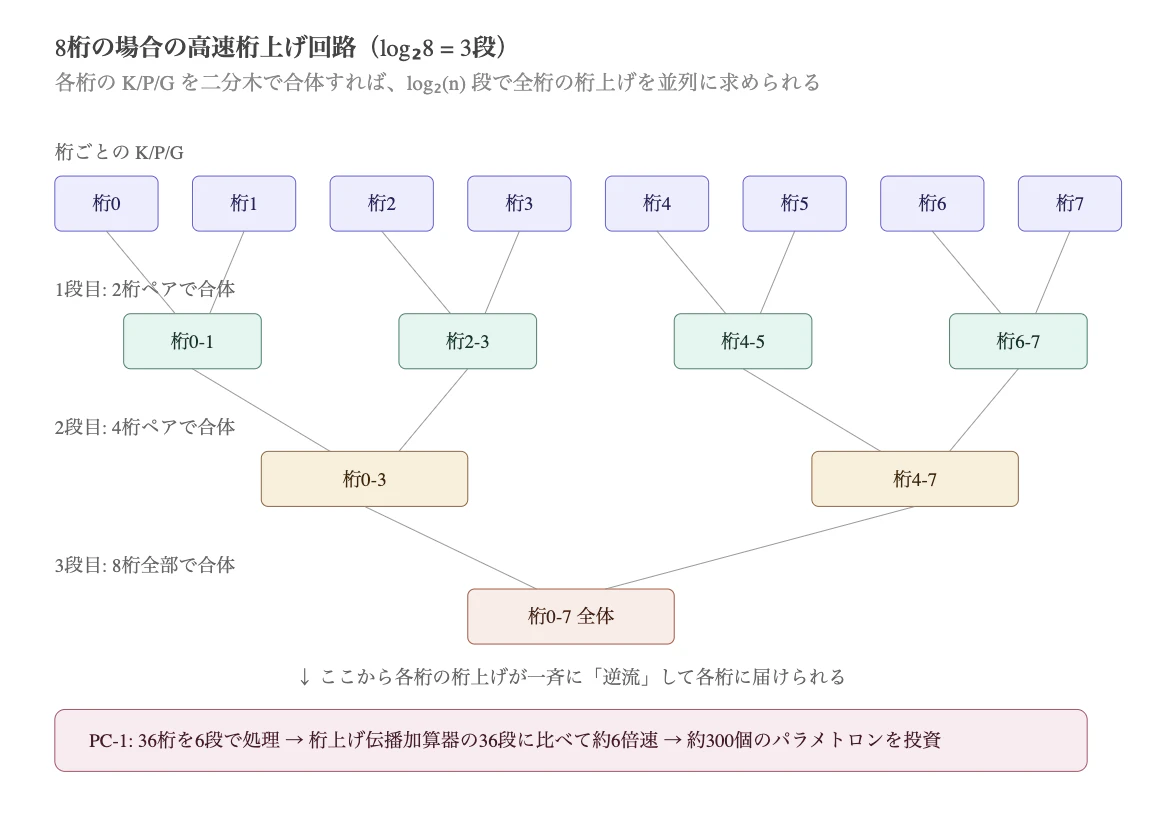

おまけ2: 「桁上げ先回り」が PC-1 でどう実装されたかを教えて

これは後藤英一氏の天才性が最も発揮された設計で、パラメトロン計算機を語る上で外せない名作です。Knuth の TAOCP にも引用されているレベルの古典です。

順を追って組み立てていきます。

ステップA:まず「桁上げ」が遅さの原因である

n ビットの加算器を作るとき、最も素朴な方法は 「桁上げ伝播加算器」(Ripple Carry Adder) です。1ビット全加算器を n 個並べて、桁上げを下から上へバケツリレーします。

例えば 36 ビット加算(PC-1 の語長)の場合:

桁0 → 桁1 → 桁2 → ... → 桁35

最悪の場合、桁0 で発生した桁上げが桁35 まで届くのに、36段分の遅延が必要です。

パラメトロンは1段で位相を確定させるのに 3 Phase(つまり3拍)かかるので、36段だと

36 × 3 = 108 拍

PC-1 の動作周波数は 1 サイクル = 約 0.4 ms 程度なので、これだと加算1回に数十ms かかってしまう。これは遅すぎます。

「桁上げをいかに速く伝えるか」が、加算器の高速化の本質的な課題です。

ステップB:桁上げの本質を見抜く

ここで後藤英一氏の発想が光ります。各桁での「桁上げの振る舞い」を観察してみましょう。

ある桁で、入力 a, b と下位からの桁上げ Cin を受け取ったとき、その桁の桁上げ出力 Cout は次のように分類できます:

| a | b | この桁の振る舞い |

|---|---|---|

| 0 | 0 | Cin に関係なく Cout = 0 → 「絶対に桁上げしない」(Kill) |

| 0 | 1 | Cin が来たら Cout = 1、来なければ 0 → 「Cin をそのまま伝える」(Propagate) |

| 1 | 0 | 同上 → Propagate |

| 1 | 1 | Cin に関係なく Cout = 1 → 「絶対に桁上げする」(Generate) |

つまり、a と b の値だけ見れば、その桁の振る舞いが3種類に分類できる:

- K (Kill):a=0 かつ b=0 → 下位から何が来ても桁上げを止める

- P (Propagate):a と b が違う → 下位の桁上げをそのままスルーする

- G (Generate):a=1 かつ b=1 → 下位に関係なく桁上げを発生させる

各桁の K/P/G は、a と b だけで決まる(Cin に依存しない)ので、全桁同時に並列計算できる。これが鍵です。

ステップC:複数桁の K/P/G を「合成」する

ここからが本当の魔法です。魔法だけにとっても難しいです。

例えば、桁i と 桁i+1 を合体させて、「2桁分の連続した振る舞い」を考えてみます。下位(桁i-1)から桁上げ Cin が来たとき、上位(桁i+1)から出ていく桁上げ Cout はどうなるか?

| 桁i+1 の振る舞い | 桁i の振る舞い | 2桁合体での振る舞い |

|---|---|---|

| K | * | K(上位がKillだから何でもK) |

| G | * | G(上位がGenerateだから何でもG) |

| P | K | K(上位はパススルー、下位がKillだからK) |

| P | G | G(上位はパススルー、下位がGenerateだからG) |

| P | P | P(両方パススルーだからP) |

これを式で書くと:

- 2桁合体の振る舞い = 上位が K → K

- 上位が G → G

- 上位が P → 下位の振る舞いがそのまま

これは、

「2桁の振る舞いを合体させると、また K/P/G のいずれかになる」

ことを意味しています。つまり「振る舞いの合体」は閉じた演算で、結合則も成り立ちます:

- (桁A と 桁B の合体) と 桁C を合体する=桁A と (桁B と 桁C の合体) を合体する

ステップD:結合則があれば、二分木で並列計算できる

結合則が成り立つ演算は、どんな順序で計算しても結果が同じなので、二分木で並列に計算できます。

例えば 8 桁の場合:

8桁なら 3段 で全桁の振る舞いが分かります。一般に n 桁なら log₂(n) 段 で済みます。

n=36 桁なら、log₂(36) ≈ 6 段。

36段 → 6段 に短縮できる

これだけでも理論的に 6倍速 になります。

このページからの引用です。

この基本回路 a)を組合わせると3入力のパラメトロンn段の回路で2n桁の桁上げまで一斉に作ることができ, b)は8桁の例である. 26=64>36であるからPC-1のでは 6段すなわち2τの遅れで桁上げを一斉に得られ, この高速桁上げ回路には約300個のパラメトロンが使用されている. この回路によりPC-1では桁上げを完全に処理する加減算命令が4τで実行可能となった.

解説すると、

- 3入力のパラメトロンn段の回路で2ⁿ桁の桁上げまで一斉に作れる」

→ 1段ごとに合体できる桁数が倍々になる、という二分木の話そのまま - 「2⁶=64 > 36 だから PC-1 では 6段で全桁の桁上げを得られる」

→ 36ビットなので6段で十分 - 「2τ の遅れで桁上げを一斉に得られる」

→ τ は PC-1 の基本クロック単位(1τ = 1サイクル ≈ 1/30kHz)。3相 × 数段の動作を1つの「τ」とみなしている特殊な単位 - 「この高速桁上げ回路には約300個のパラメトロンが使用されている」

→ 36ビットの桁上げ伝播のために、専用に300個。これは結構な投資 - 「加減算命令が 4τ で実行可能」

→ PC-1 全体のクロックサイクルとして、加算1回が約 0.4ms で完結する

基本ブロックの構造

「3入力のパラメトロン1個」が、合体演算 (K/P/G の結合) を実現する基本ブロックとして使われます。

ここがすごいところですが、多数決パラメトロン1個で K/P/G の合体ができます。

仮に下位の振る舞いを c1(桁上げ伝播)、上位の振る舞いを c2 とすると、合体した振る舞いは:

合体 = (c2 が P かつ c1 が伝える桁上げ) または (c2 が G の場合の桁上げ)

これを論理式で書くと、引用文にもある通り:

a)の回路は (x2, y2)が(0, 0)または(1, 1)ならば(z, z')は(0, 0)または (1, 1)となる. すなわち(x2, y2)では次の桁への桁上げが定まる場合には(z, z')は(x2, y2)で定まる. 次に (x2, y2)が(1, 0)または(0, 1)ならば(z, z')は (x1, y1)で定まる. すなわち(x2, y2) では次の桁への桁上げが定まらない場合にはその前の桁から定まる.

つまり:

- 上位 (x2, y2) が K か G なら(=(0,0) か (1,1))→ 上位の値で確定

- 上位 (x2, y2) が P なら(=(1,0) か (0,1))→ 下位の値が透過

これがまさに合体演算で、多数決の組み合わせで実現できるわけです。

図にしてみる

「桁上げを下から上に流す」のではなく「上から下に逆流させる」

ここがアイデアの真骨頂です。

普通の桁上げ伝播加算器は「下位から上位へ」桁上げを順に渡していきます。これが遅さの原因です。

PC-1 の高速桁上げ回路は逆で:

- 下から上に向かって、二分木で「振る舞い」を log₂(n) 段で集約していく(K/P/G の合体)

- 最上位まで集約された後、上から下に向かって、各桁の確定した桁上げ値を一斉に配る

つまり情報が一度上に上って、また下に降りてくるのです。これにより、最下位の桁だけでなく、全桁が同時に確定した桁上げを得ることができます。

これで全加算器の和の計算 (S = a XOR b XOR Cin) も全桁同時に並列実行できる、というわけです。

これがどれくらい先進的だったか

この 「並列接頭辞和(Parallel Prefix Sum)」 という考え方は:

- 後藤英一氏が PC-1 の設計で 1957 年に独自に発明

- 国際的には Kogge-Stone アルゴリズム(1973年)として知られているが、PC-1 はそれより16年早い

- 現代の CPU でも64ビット加算器に同じ原理が使われている

つまり現代の Intel や AMD の CPU の中にある加算器のアルゴリズムは、本質的に PC-1 と同じということです。

引用元の和田英一氏の記事にもあった通り:

これらの桁上げ分離演算及び同時制御方式は最近外国でも計算速度向上の為に種々研究されていて, パラメトロンに限らず, 如何なる種類の素子を用いる電子計算機にも, 殆んどそのまま適用する事が出来るのである

「素子に依存しない」と言い切っているのがすばらしい。素子の特性に頼らない、純粋なアルゴリズムとしての発明だ、という自信がみえます。

自己双対関数

引用に少し難しい言葉が出てきました:

全加算器には定数入力がない. これを自己双対関数という. つまり上の表で0 と1 を交換すると表 を下から読むのと同じになる. もう一つの有用な自己双対なものは高速桁上げ回路

これは何を言っているかというと:

自己双対関数とは「すべての入力を反転すると、出力も反転する」関数のことです。

例えば全加算器の真理値表で、

- 入力 (a, b, c) = (0, 0, 0) のとき出力 (S, Cout) = (0, 0)

- 入力 (a, b, c) = (1, 1, 1) のとき出力 (S, Cout) = (1, 1)

入力を全部反転すると出力も全部反転する。これが自己双対です。

なぜこれがパラメトロンにとって重要か?

パラメトロンの世界では、ステップ1で説明した通り「位相0 = 0」「位相π = 1」という割り当ては任意でした。「逆向きに巻いた線で受ければ NOT になる」という性質から、0 と 1 を全部入れ替えても全く同じ回路が動くわけです。

自己双対関数をパラメトロンで実装すると、「0 寄り」と「1 寄り」のどちらにも偏らないバランスの取れた回路になります。これは:

- 設計が対称で美しい

- 電源ノイズの影響を受けにくい

- 0/1 の確率が偏らないので、消費電力も均衡する

という工学的メリットがあります。後藤英一氏は美学的にも自己双対性を重視していた、という側面が読み取れる部分です。

まとめ

「桁上げ先回り」を PC-1 で実現した方法を整理すると:

| ポイント | 内容 |

|---|---|

| 課題 | 桁上げ伝播は最悪 n 段の遅延 → n=36 で約108拍 |

| アイデア | 各桁の振る舞いを K/P/G に分類し、二分木で並列に合体 |

| 必要素子 | 約300個のパラメトロン(PC-1 全体 4,200個の約7%) |

| 効果 | 36段 → 6段 → 6倍以上の高速化 |

| 結果 | 加減算が 4τ で完結する高性能機に |

| 歴史的意義 | Kogge-Stone より16年早い、世界最先端の並列加算アルゴリズム |

| 副次効果 | 自己双対性によるノイズ耐性と回路の対称美 |

ストーンワールド的視点

千空が「20万個のパラメトロン」と言っているスケール感も、これで腑に落ちます。

- 全加算器1個 = 5個

- 36ビット加算器(桁上げ伝播) = 5 × 36 ≒ 180個

- 36ビット加算器(高速桁上げ付き) = 約480個(300個 + 180個)

- レジスタ3本(36ビット × 3)= 36 × 3 × 3 = 324個(3個1組のループ × 108ビット)

- メモリ、制御回路、バス、入出力

- 遅延・中継パラメトロン(論理用と同じくらい必要)

これらを全部足すと、実用的な計算機を作るには本当に数万〜20万個のパラメトロンが必要になるのが分かります。アニメの数字は誇張でもなんでもなく、むしろ控えめかもしれません。

最後に

パラメトロンを調べていてとても奥が深いことになりました。Dr.STONE、これをさらっと紹介するとは、なんて恐ろしい子。