IBMのPOWER8が昨年8月に発表されたとき、ひときわ怪しかったのがCAPIなる機能。

From https://twitter.com/Daniel_Bowers/status/372101503936253952

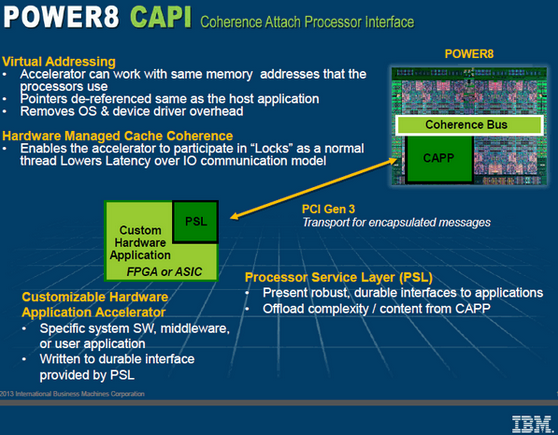

CAPIはCoherence Attache Processor Interfaceの略で、外部ハードウェア上のメモリとCPUキャッシュ間のコヒーレンス(整合性)をものっすごい高帯域で維持してくれるインタフェース。そして注目すべきは、その外部ハードウェアとして左下にちらっと「FPGA or ASIC」と書かれていること。つまりIBMは、POWER8を外部のFPGAやASICとつないで、それをほとんどCPUの一部分のような速度で使うための仕組みを用意した、というわけだ。

これを見て、うーむ、こいつはPOWER8とFPGAの組み合わせで何か面白いもの出してくるな! とニラんでところ、案の定。つい先日開催されたIBM Impact 2014でXilinxとAlteraがPOWER8+FPGAの事例を出してきたと@ogawa_tterさんが教えてくれた。以下はXilinxのプレスリリース。

From http://press.xilinx.com/2014-04-25-Xilinx-Demonstrates-FPGA-Based-Acceleration-Technology-for-Next-Generation-Data-Centers-at-IBM-Impact-2014

POWER8+FPGAでKey Value Storeを実装

このプレスリリースで注目すべきは次の部分:

The Xilinx demonstration is a broadly applicable CAPI-based key value store workload acceleration engine (i.e. Memcached and NoSQL) that delivers significant performance/watt acceleration at substantially lower latency and compliments the OpenCL™ design environment for Xilinx devices.

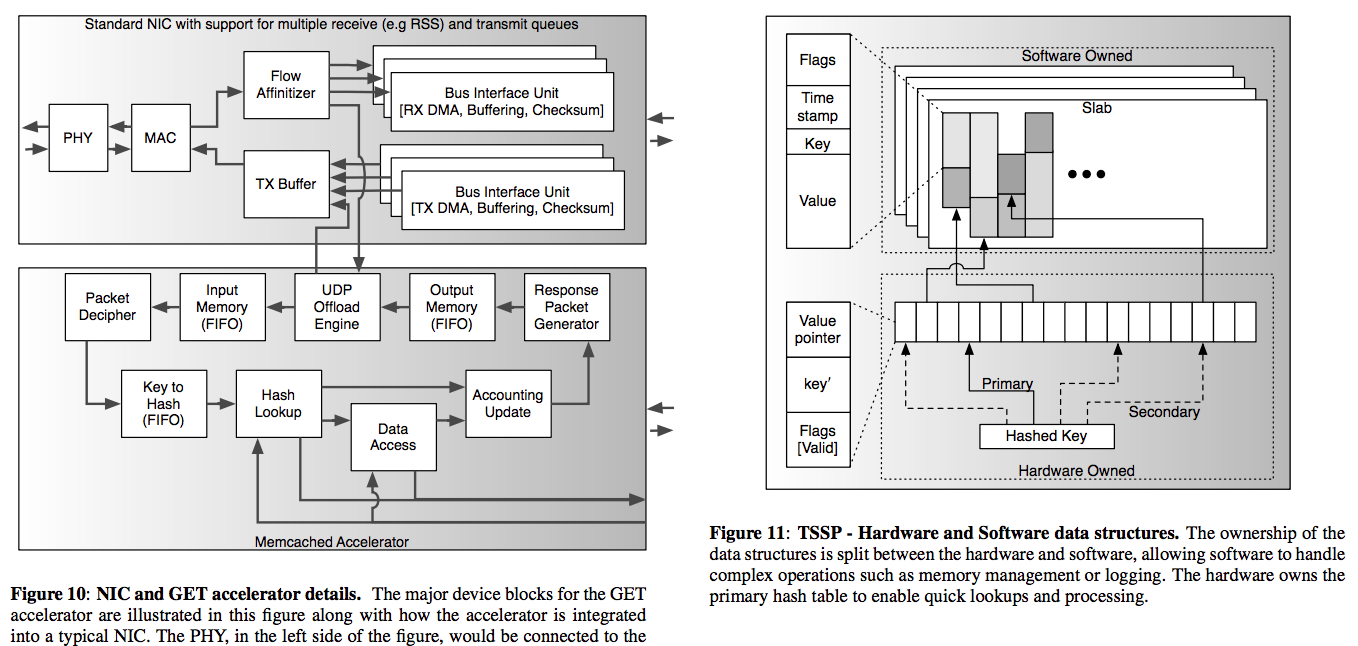

つまり、Key Value StoreのアクセラレーションをFPGAで実装しているって点だ。Xilinxはこれまでにも実効10Gbpsで動くMemcachedのFPGA実装を発表したりと、FPGAのデータ処理やアプリケーション処理への応用に積極的。しかし実用化を考えると、FPGA単独でのアプリロジック実装には限界がある。例えばMemcacheの例ではメモリ領域管理やエラーハンドリングなど、複雑なロジックが要求される部分をすべてハードウェア実装するのは難しく、大幅な機能面での制約が生じてしまうのだ。

そこでキーとなるのが、FPGAによるハード実装とCPUによるソフト実装の協調設計。HP Labs/Facebook/ARM/Univ of Michiganが発表したThin Servers with Smart Pipesというコンセプトでは、ARM+FPGAのヘテロコアの利用を前提に、get()等の単純処理はFPGAで、put()や例外処理等の複雑な処理はCPUで、という協調実装が提案されている。つまり、POWER8のCAPIは、こうしたソフト+ハード協調実装が今後どんどん普及していくことを見込んで投入された技術なのだ。

From http://web.eecs.umich.edu/~twenisch/papers/isca13.pdf

Alteraはモンテカルロによる金融リスク分析をデモ

@ogawa_tterさん情報によると、IBM Impact 2014ではAlteraからも*Financial Risk Modeling with CAPI Accelerator (Monte Carlo)*という発表があったらしい(が資料は見当たらない)。おそらくは、モンテカルロ・シミュレーションの部分のみをFPGA上のハード実装で大規模並列に実行し、その前後処理はPOWER8が担当、といったものと想像される。

というわけで、CPUとFPGAによるハード+ソフト協調実装のビッグウェーブが遠くから押し寄せつつあるのを感じる今年のGWであった。

Disclaimer この記事は個人的なものです。ここで述べられていることは私の個人的な意見に基づくものであり、私の雇用者には関係はありません。