はじめに

Linux では DMA Bufferを mmap した時に、ある条件が揃うと CPU Cache が無効になり、パフォーマンスが極端に落ちる場合があります。そこで、何故そのようなことが起こるのか説明します。少し長くなるので、次のように記事を幾つかに分けて投稿します。

- はじめに

- Cache Coherence 問題

2.1 Cache Coherence 問題とは何か

2.2 Cache Coherence 問題の解決方法(この記事) - Cache Aliasing 問題

- Linux Kernel の Cache 問題の扱い

- Linux では Cache Coherence Hardware を持っていないとDMA Buffer をmmap する際に CPU Cache が無効になる

- Raspberry Pi の例

- RISC-V CPU の注意点

- 所感

1〜3は、コンピューターアーキテクチャの基本的な事項を、簡単に説明したものです。すでにご存じの方は読み飛ばしてください。

4 はこれらの問題を Linux Kernel 内でどのように扱っているかを説明します。

5 がこれらの記事群の結論です。結論だけ知りたい方はここだけ読んでください。

前回の記事 『Linux で DMA Bufferを mmap した時に CPU Cacheが無効になる場合がある (Cache Coherence 問題とは何か)』 では、「Linux で DMA Bufferを mmap した時に CPU Cacheが無効になる場合がある」原因の一つである Cache Coherence 問題について説明しました。この記事では、その Cache Coherence 問題の解決方法を説明します。すでにご存じの方は読み飛ばしてください。

Cache Coherence 問題の解決方法

ここでは、Cache Coherence 問題を解決する方法として次の3つを説明します。

キャッシュを使わない

Cache Coherence 問題の解決方法が、いきなり「キャッシュを使わない」というのはどうかと思いますが、実はよく使われます。なぜなら、比較的簡単にできるからです。

Linux が動作するような CPU は、通常、仮想アドレスをサポートしています。そして仮想アドレスを物理アドレスに変換するための MMU(Memory Management Unit) を搭載しています。じつは MMU には仮想アドレスを物理アドレスに変換する際に、その仮想アドレスに対するアクセスの属性(実行可/不可、書き込み可/不可など) を指定することができます。その属性に キャッシュ可/不可もあります。したがって、ページ単位でキャッシュ可/不可を容易に変更することができるのです。

そのかわり、当然ですが、CPU からのアクセス速度はとてもとても遅くなります。

特徴

- ソフトウェアの実装負担:軽い

- 実質 MMU の設定のみ

- ハードウェアの実装負担:軽い

- MMU が必要だが、Linux が動作する CPU はすでに実装済み

- CPU からのアクセス:とても遅い

ソフトウェアでなんとかする方法

前節では「キャッシュを使わない」方法を説明しましたが、せっかくキャッシュがあるんだから、もう少しなんとかならないのか、というわけでソフトウェアでキャッシュを制御する方法が考え出されました。この節ではその方法を説明します。

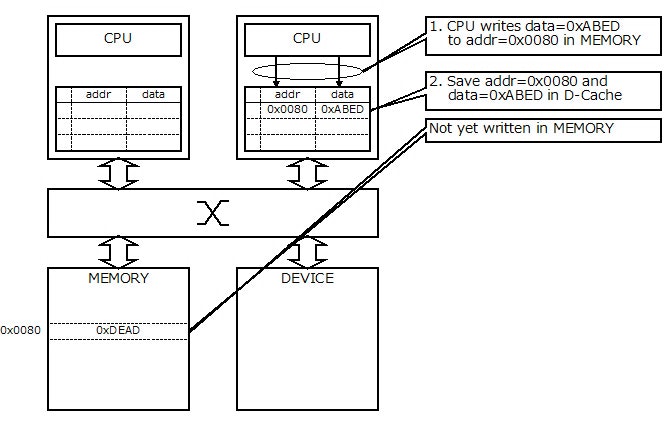

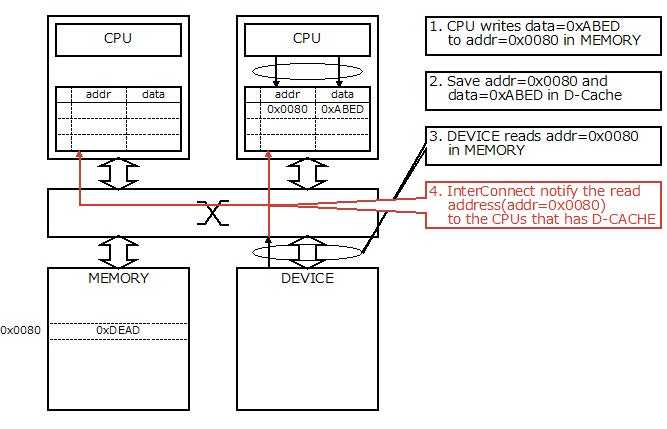

CPU が DMA Buffer に書き込んで DEVICE が読む場合

まず、CPU が DMA Buffer にデータを書き込んで、DEVICE が DMA を使って DMA Buffer を読む場合を考えます。その場合は次の図のように処理が進みます。

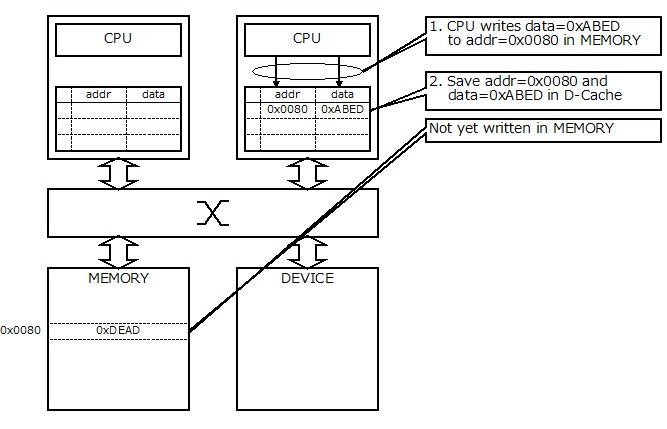

Fig.1 Software Solution to Cache Coherence Problem 1-1

- CPU が MEMORY 上の DMA Buffer にデータの書き込みを要求します。

図の例ではaddr=0x0080 に data=0xABED の書き込みを要求しています。 - CACHE が有効な場合は、MEMORY への書き込みは保留され、まずCACHE に書き込んだアドレスとデータが記憶されます。

図の例では D-Cache に addr=0x0080 と data=0xABED が記憶されます。

この状態では、まだ MEMORY 上にはデータが書き込まれていません。

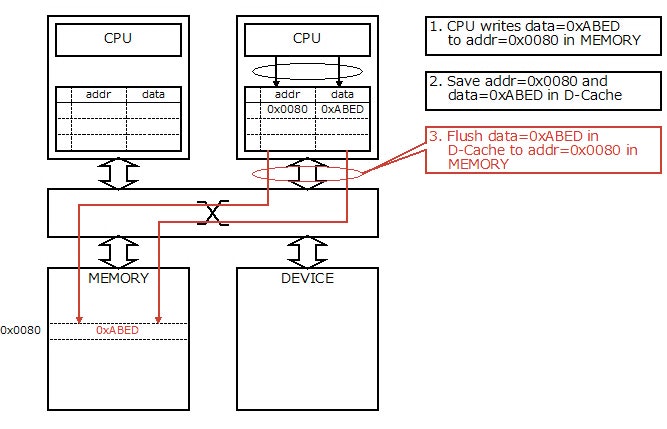

Fig.2 Software Solution to Cache Coherence Problem 1-2

- ここで CPU が CACHE に対して該当するアドレスの内容を強制的に MEMORY に吐き出させます(Flush します)。

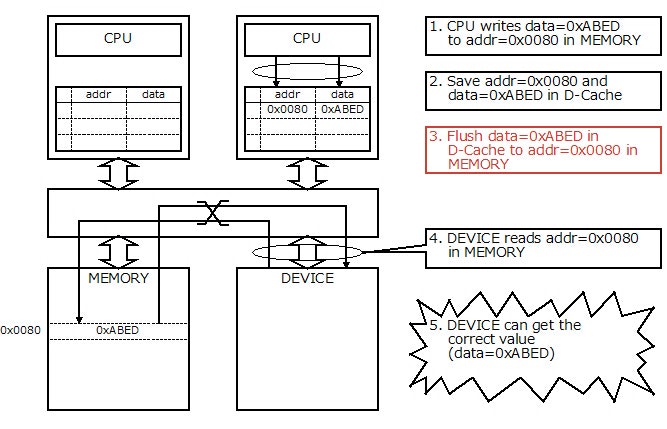

Fig.3 Software Solution to Cache Coherence Problem 1-3

- 次に DEVICE が DMA を使って DMA Buffer を読みに行きます。

- MEMORY にはすでに CPU が書き込みを要求した値が反映されているので、 DEVICE は CPU が書き込んだ値を得ることができます。

これが、CPUが DMA Buffer に書き込んで DEVICE が読む場合の Cache Coherence 問題をソフトウェアで解決する方法です。

DEVICE が DMA Buffer に書き込んで CPU が読む場合

次に、DEVICE が DMA Buffer にデータを書き込んで CPU が読む場合を考えます。その際、次の図のように CPU の Cache になんらかのデータがすでにキャッシュされているとします。

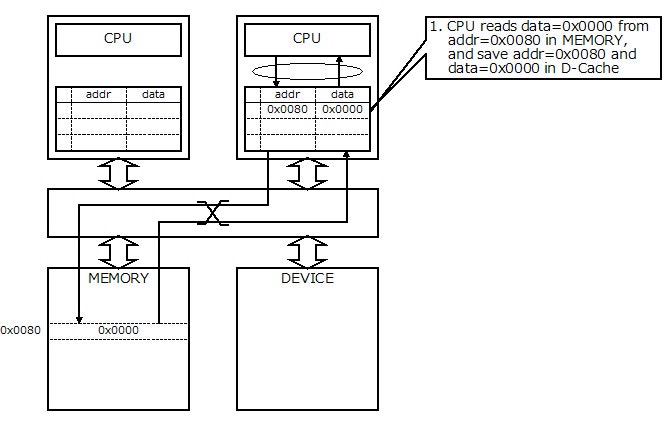

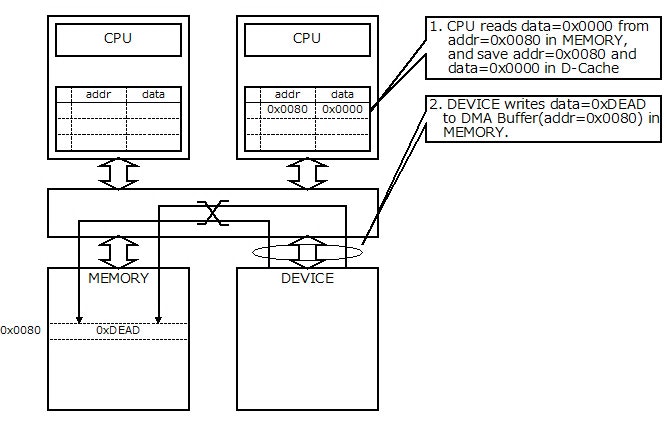

Fig.4 Software Solution to Cache Coherence Problem 2-1

- CPU が DMA Buffer からのデータを読み込んでその内容が CACHE に記録されている、あるいは CPU が DMA Buffer を初期化してその内容がすでに MEMORY に反映されているとします。この図の例では addr=0x0080 の data=0x0000 が D-Cache 上にすでに記録されています。

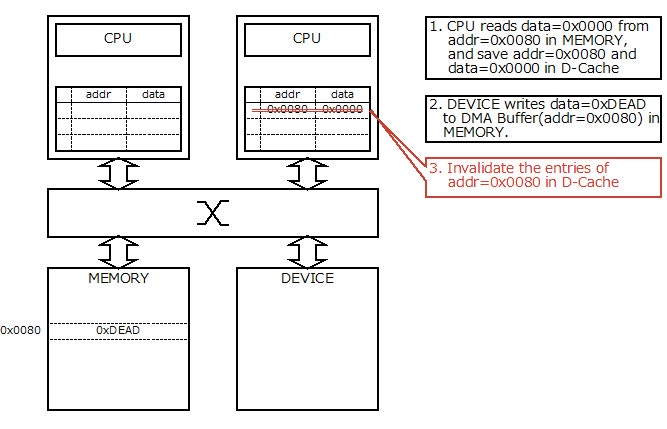

Fig.5 Software Solution to Cache Coherence Problem 2-2

- DEVICE が DMA Buffer にデータを書き込みます。

この図の例では addr=0x0080 に data=0xDEAD を書き込んでいます。

Fig.6 Software Solution to Cache Coherence Problem 2-3

- ここで CPU が CACHE に対して該当するアドレスの内容を破棄(Invalidate)するように命じます。

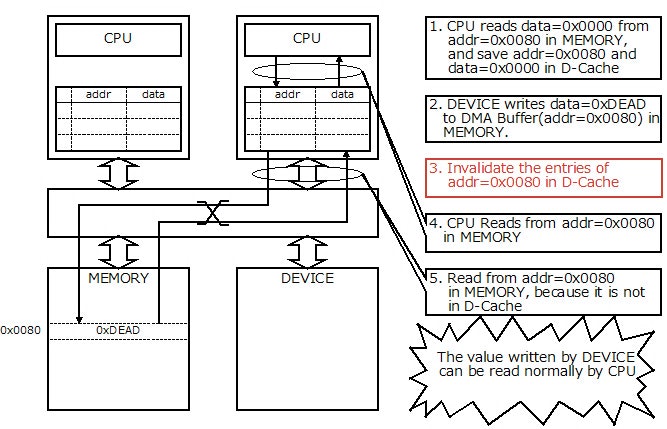

Fig.7 Software Solution to Cache Coherence Problem 2-4

- CPU が DMA Buffer のデータを読みます。

- CACHE には DMA Buffer に該当するアドレスの内容が破棄されているため、あらためて MEMORY から読まれます。そのため、DEVICE が書き込んだ値を CPU が得ることが出来ます。

これが DEVICE が DMA Buffer に書き込んで CPU が読む場合の Cache Coherence 問題をソフトウェアで解決する方法です。

特徴

- ソフトウェアの実装負担:とても重い

- CPU からのアクセスと DEVICE からのアクセスが排他的であるため、制御が必要

- DEVICE が DMAするタイミングをソフトウェアが管理できないといけない

- ハードウェアの実装負担:軽い

- キャッシュの Flush/Invalidate 機構が必要だが、たいていの CPU はすでに実装済み

- CPU からのアクセス:まあまあ速い

- CPU からのアクセスだけなら速いが、 キャッシュの Flush/Invalidate に意外と時間がかかることに注意が必要。

ハードウェアでなんとかする方法

前節ではソフトウェアでなんとかする方法を説明しましたが、特徴でも説明した通り、ソフトウェアの実装負担が重くとてもとても面倒です。

さすがに面倒臭くなったのか、最近はハードウェアでなんとかしてしまう方法が一般的です。そこで、この節では Cache Coherence 問題をハードウェアで解決する方法を説明します。

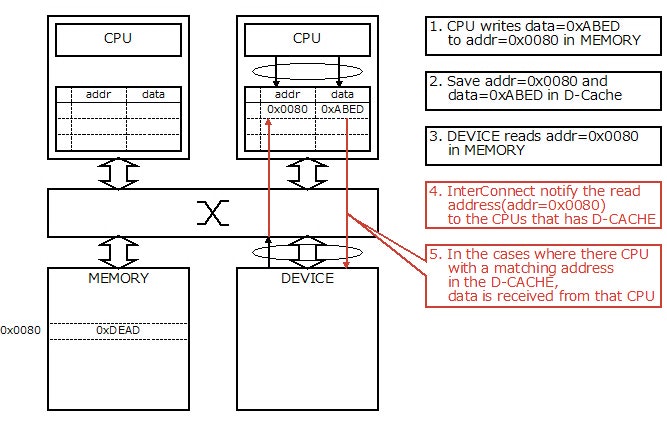

CPU が DMA Buffer に書き込んで DEVICE が読む場合

まず、CPU が DMA Buffer にデータを書き込んで、DEVICE が DMA を使って DMA Buffer を読む場合を考えます。その場合は次の図のように処理が進みます。

Fig.8 Hardware Solution to Cache Coherence Problem 1-1

- CPU が MEMORY 上の DMA Buffer にデータの書き込みを要求します。

図の例ではaddr=0x0080 に data=0xABED の書き込みを要求しています。 - CACHE が有効な場合は、MEMORY への書き込みは保留され、まずCACHE に書き込んだアドレスとデータが記憶されます。

図の例では D-Cache に addr=0x0080 と data=0xABED が記憶されます。

この状態では、まだ MEMORY 上にはデータが書き込まれていません。

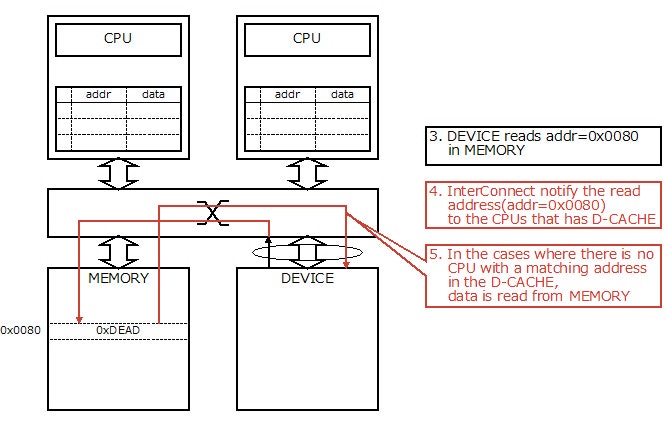

Fig.9 Hardware Solution to Cache Coherence Problem 1-2

- DEVICE はMEMORY に対して DMA Buffer からの読み出し要求を行います。

この時、Cache Coherence 問題をハードウェアでなんとかする場合、まず InterConnect が DEVICE からの要求を一旦受け付けます。 - InterConnect は DEVICE からの読み出し要求で指定されたアドレスを、キャッシュをもっている CPU に対して通知します。これをスヌープと言います。

Fig.10 Hardware Solution to Cache Coherence Problem 1-3

Fig.11 Hardware Solution to Cache Coherence Problem 1-4

- 該当するアドレスの内容を保持している CACHE をもつ CPU が存在する場合は、そのCPUからデータをもらいます。

また、該当するアドレスの内容を保持している CACHE をもつ CPU が一つも存在しない場合は、MEMORY からデータを読み取ります。

これが、CPUが DMA Buffer に書き込んで DEVICE が読む場合の Cache Coherence 問題をハードウェアで解決する方法です。

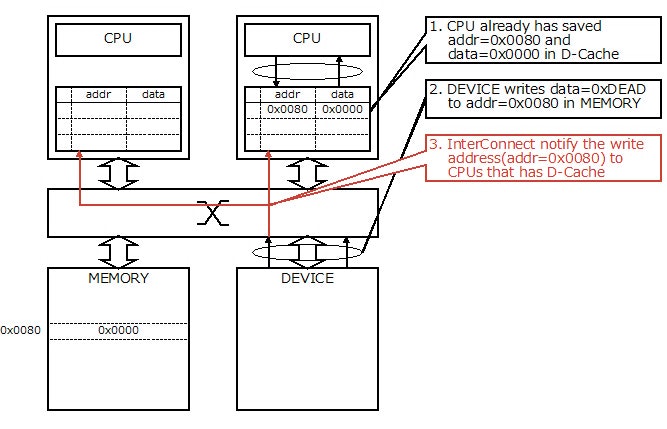

DEVICE が DMA Buffer に書き込んで CPU が読む場合

次に、DEVICE が DMA Buffer にデータを書き込んで CPU が読む場合を考えます。その際、次の図のように CPU の CACHE になんらかのデータがすでにキャッシュされているとします。

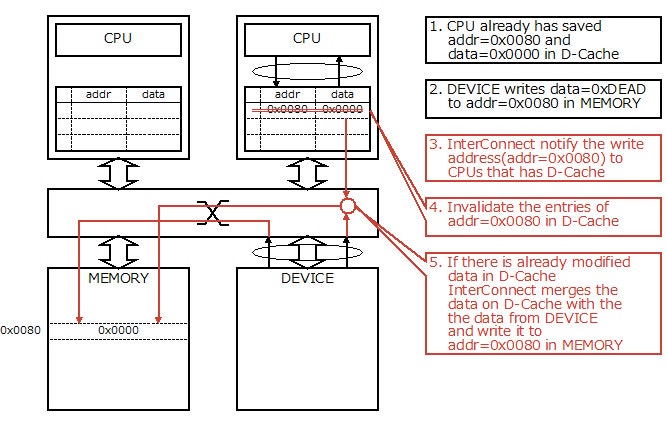

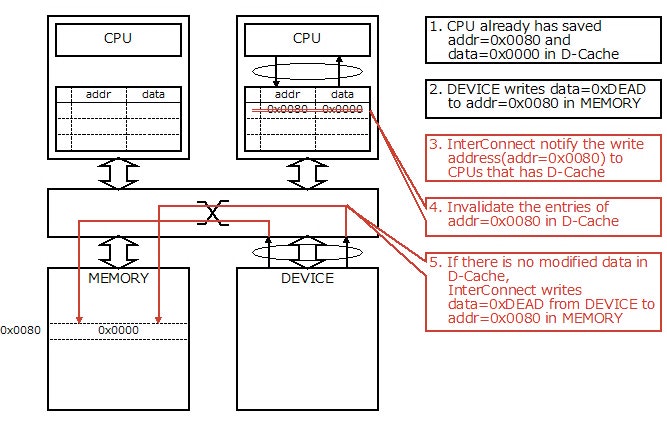

Fig.12 Hardware Solution to Cache Coherence Problem 2-1

- CPU が DMA Buffer からのデータを読み込んでその内容が CACHE に記録されている、あるいは CPU が DMA Buffer を初期化してその内容がすでに MEMORY に反映されているとします。この図の例では addr=0x0080 の data=0x0000 が D-Cache 上にすでに記録されています。

- DEVICE はMEMORY に対して DMA Buffer への書き込み要求を行います。

この時、Cache Coherence 問題をハードウェアでなんとかする場合、まず InterConnect が DEVICE からの要求を一旦受け付けます。

この図の例では MEMORY 上のaddr=0x0080 に data=0xDEAD を書き込むことを InterConnect に要求しています。 - InterConnect は DEVICE からの書き込み要求で指定されたアドレスを、キャッシュをもっている CPU に対して通知します。これをスヌープと言います。

Fig.13 Hardware Solution to Cache Coherence Problem 2-2

- CPU は InterConnect からの書き込みアドレスを受け取り、CACHE 内に該当する内容が存在するか調べます。もし存在しているならば、その内容を破棄(Invalidate)します。

- CACHE 内のデータが汚れている状態(CPU がMEMORY に対して書き込み要求を行い、まだMEMORY に反映されていない状態)の場合は、単純にその内容を破棄(Invalidate)出来ません。何故なら、CPU が要求した MEMORY への書き込みが消えてしまい、MEMORY との一貫性が失われるからです。

したがって、CACHE 内のデータが汚れている状態の場合は、InterConnect は CACHE に残っているデータと DEVICE からの書き込みデータをマージして MEMORY に書き込みます。

Fig.14 Hardware Solution to Cache Coherence Problem 2-3

- CACHE 内のデータが汚れていない状態(CPU がMEMORY に対して書き込み要求を行っていない状態)の場合は、単純にその内容を破棄(Invalidate)します。

その上で、InterConnect は DEVICE からの書き込みデータを MEMORY に書き込みます。

特徴

- ソフトウェアの実装負担:無し

- ハードウェアの実装負担:とても重い

- CACHE は CPU からだけでなく外部からのスヌープにも対応必須

- InterConnect はスヌープに対応、

かつ、 CACHE からのデータのマージ書き込みに対応必須 - 上記の機能をサポートした Inter Connect Protocol が必要

- CPU からのアクセス:速い

まとめ

この記事では、「Linux で DMA Bufferを mmap した時に CPU Cacheが無効になる場合がある」のを説明する際に、知っておいてほしい Cache Cohernce 問題について、どのような解決方法があるのかを説明しました。これら解決方法の比較を簡単に表にまとめると次のようになります。

Table.1 Cache Coherence 問題の解決方法比較

| ソフトウェアの実装負担 | ハードウェアの実装負担 | CPUからの アクセス速度 |

|

| キャッシュを使わない方法 | 軽い | 軽い | とても遅い |

| ソフトウェアによる解決方法 | とても重い | 軽い | まあまあ速い |

| ハードウェアによる解決方法 | 無し | とても重い | 速い |

次の記事 『Linux で DMA Bufferを mmap した時に CPU Cacheが無効になる場合がある (Cache Aliasing 問題とは何か)』 では、「Linux で DMA Bufferを mmap した時に CPU Cacheが無効になる場合がある」もう一つの原因である Cache Aliasing 問題について説明します。