はじめに##

自己紹介

十年間にわたり組込みOSの分野でFAE/プロジェクトマネージャを経験。

現在はヘテロマルチコア向けのソースコード解析や最適化を行うSilexicaで奮闘中。

記事内容

HLSを使ってFPGAを設計する際に直面する5つの問題についてです。

目次

HLSの使用によるFPGAへの注目

5つの課題

HLSコンパイラーによって合成不可能なC/C++コード

ハードウェアに対応していないC/C++コード

並列化の特定

ソフトウェアとハードウェアの分割

C / C ++コードへのHLSコンパイラ プラグマやディレクティブの挿入

HLSの使用によるFPGAへの注目

C/C++ ソースコードをVerilog/VHDLに変換するHLS (High-Level Synthesis: 高位合成)は15年以上前から市販されています。FPGAまた EDAベンダー のHLSツールはより高度な抽象化、検証の高速化、および設計の反復の迅速化によって生産性の向上が見込まれています。例えばC/C++によるデザインシミュレーションをする場合、RTL(レジスタ転送レベル)でシュミレーションするよりも10倍から100倍高速になりえます。また、画像処理やコンピュータービジョンの多くのアプリケーションでは視覚的な検証が必要とされてます。RTLシミュレーションを実行する場合、このような検証は設定が困難ですが、Cレベルで簡単に実装できます。 HLSベースの手法を使用しながらシミュレーションのスピードを上げることで、設計の反復が速くなり生産性の向上に大きく貢献します。迅速なシミュレーションでより速い設計の繰り返しをもたらすからです。

HLSを利用することで、組み込みソフトウェアプログラミングを専門にしているより多くのエンジニアによるFPGAの使用が注目を集めるかもしれません。従来のFPGA 設計方法はVerilog やVHDLなどハードウェア記述言語(HDL)で設計をするため、非常に特殊なスキルセットと熟練度が必要でした。このスキルセットは、組み込みソフトウェア開発者と比較して非常にまれであり、FPGAの使用がHDLでのコーディング経験のあるものに限定されてしまいます。

HLSを使用することによって、組み込みソフトウェア開発者(およびハードウェアエンジニア)は、C / C ++など高水準言語を用いてハードウェアでのアルゴリズムの実装が可能になります。

5つの課題

FPGA設計にHLSの使用がそれほど重要なのであれば、どうしてC/C++でFPGA設計をすることが標準的な設計入力方法にならなかったのでしょうか?

簡単な答えとしてはHLSの設計方法の導入は現実的に設計の過程で考えを要し、取り除かなければなならない特有な課題が存在しているからです。これらの課題は設計者により多くの負担をかけてしまい、開発時間に影響がでることでHLSの生産性が否定されてしまいます。

これら5つの課題を見ていきましょう。

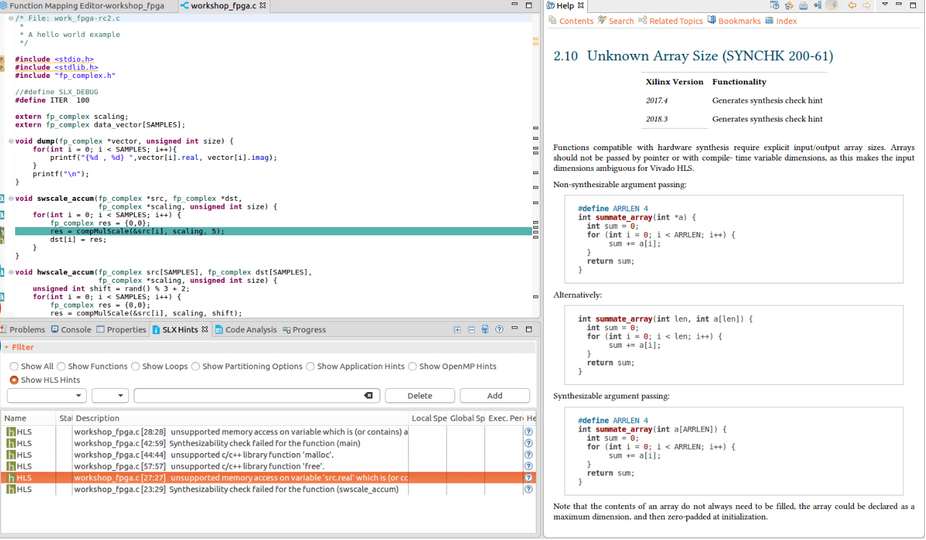

1.HLSコンパイラーによって合成不可能なC/C++コード

HLSコンパイラーのC/C++コードガイドラインは広範囲にわたります。HLS合成のためのCコードの記述やリファクタリングをする際に理解しなければならない資料は1000ページ以上に上ることもあります。例として、HLSは動的サイズの配列内の変数に対するメモリアクセスのサポートはしていません。また、特定のFPGAデバイス内のメモリ容量は固定されています。つまり、malloc、calloc、newなどの関数への呼び出しで可変サイズのオブジェクトを動的に割り当てるコードはサポートされていません。HLSツールは、効率的なハードウェア実装を実現するために、コンパイル時にアルゴリズムが要する必要なメモリリソースを知っている必要があります。

2.ハードウェアに対応していないC/C++コード

ハードウェア実装を考慮に入れない、さまざまなメモリ構成、データ型などを使用してC / C ++コードを作成すると、デバイスリソースの肥大化やパフォーマンスの低下など、意図しない結果を招く可能性があります。非常に大きく、かつ不要なデータ型を用いらないよう注意が必要です。例えばソフトウェアで10ビット整数のみが必要な時に、標準プロセッサではレジスタまたはメモリ位置がすでに固定サイズであるため、32ビット整数型の使用はそれほど問題ではありません。しかし、ハードウェアで使われていないビットを用いて実装すると、FPGAの場合は貴重なFPGAリソースを無駄に消費することになります。

3.並列化の特定

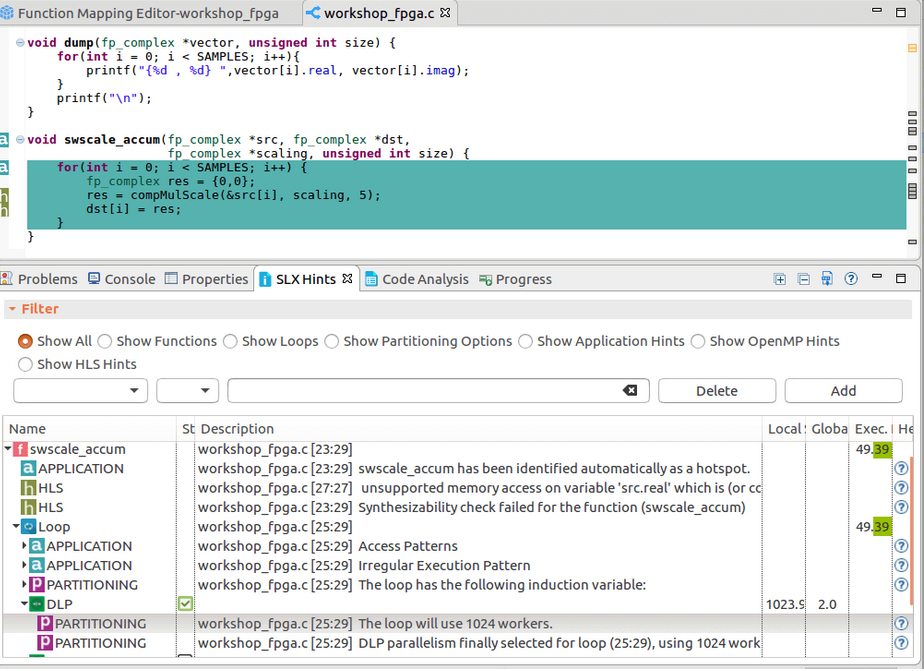

C/ C ++コードは通常、標準的なプロセッサで順次実行されますが、論理ゲートで機能を実装すると、操作を並列に実行できるため、ハードウェアでのコードの実行が高速化されます。設計内で並列処理の可能性を見つけることは、アルゴリズム、関数、コードベースの複雑さが増すにつれ極めて難しく、時間がかかる可能性があります。

4.ソフトウェアとハードウェアの分割

ヘテロジニアス(この場合エンベデッドプロセッサを搭載したFPGA)設計の場合、HLSを介してFPGAファブリックの並列性を利用するためにプロセッサ上で実行するものと、ハードウェアに移行するものを特定する作業でかなりの時間と作業の繰り返しが必要になります。合成前のシミュレーションをしている場合もです。

5.C / C ++コードへのHLSコンパイラ プラグマやディレクティブの挿入

HLSコンパイラがソフトウェアをハードウェアに効果的に実装するためには、ユーザはプラグマまたはディレクティブの形式でコンパイラにガイダンス情報を提供する必要があります。

例えば、 プラグマを使用するタイミング、パラメータの設定方法、コード内の挿入場所、およびアプリケーション内でシステムレベルでプラグマを最適化する方法を決定するのは、困難で時間がかかります。

つまり、HLS設計の利点を活用したい人にとって、これらの課題は大きな壁となっています。HLSベンダーは顧客を教育するため、様々な資料やトレーニングによってどのようにこれらの問題に取り組めばいいのかを伝えていますが、今だ手作業の過程が残っているため、習得するのに時間がかかります。

SilexicaのSLX FPGAツールは、10年以上にわたるコンパイラテクノロジの研究に基づいており、HLS設計プロセスの各ステップを通じてこれらの課題一つ一つに取り組むことで、先ほど述べた問題に対する実用的なソリューションを提供します。

まず、SLX FPGAはC / C ++ソースコードの合成可能性を解析し、合成不可能なコードのリファクタリングを自動で行い、コードリファクタリングのヒントとなる情報を提供をします。 SLXは、合成不可能なコードの各セクション情報をユーザーに知らせ、コードを自動的に変換するか、コードを合成可能にリファクタリングする方法などのヒントを与えてくれます。

今後発売されるSLX FPGAでは、効率の悪いハードウェア実装をもたらすハードウェアに不向きなデータ構造を特定します。 SLXツールは、どのようなさまざまなデータ型オプションがより効率的な実装に適しているかを確認するために、高速の「what if」分析を実行する方法を提供します。また、新しいSLXでは合成不可能なコードに対し、パフォーマンスや、リソース使用率の見積もりを提供する機能のサポートを追加し、合成可能にするためのコードリファクターすることなく、アプリケーションの細かな情報を提供します。

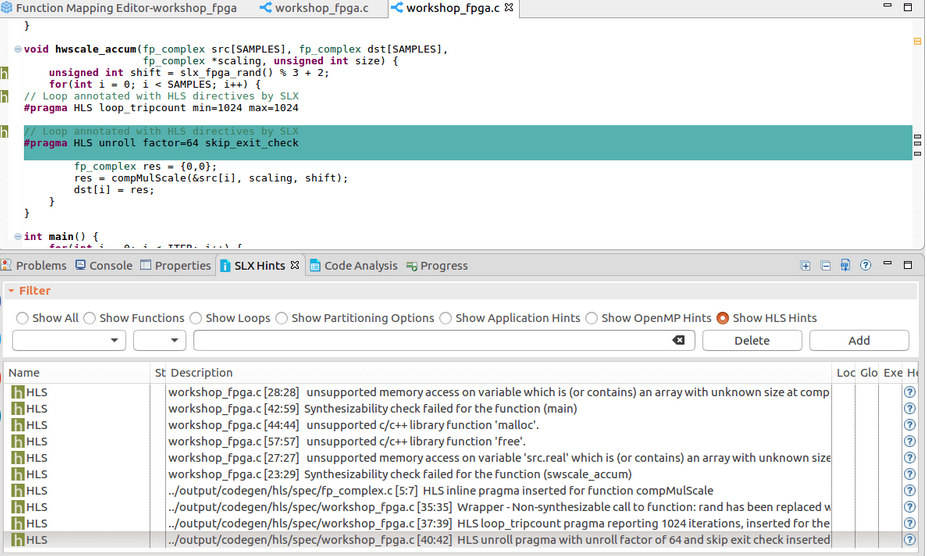

SLX FPGAが次に取り組む課題は、逐次実行から並列実行またはパイプライン実行に変換できる並列処理についてアルゴリズムまたはアプリケーションを分析することです。並列処理を識別することで、SLXはC / C ++コードの最も効率的なハードウェア実装を提供します。組み込みプロセッサを搭載したFPGAシステム使用する場合、SLX FPGAはソフトウェア ドメインとハードウェアドメイン間でコードの効率的な分散のヒントを提供するでしょう。

ソフトウエアとハードウエアの分割が定義された後、SLX FPGAはプラグマをコードに挿入し、C / C ++コードのコンパイル時にHLSコンパイラがハードウエア上に最適化されたシステムを実装できるようになります。

SLX FPGAはHLS設計フローを使用する際の課題に直接取り組む業界初のツールです。C/C++コードを最適化されたハードウェア実装に変換するための実用的な洞察を提供することで、習得にかかる時間を削減します。

最後に

ここまで読んでくださってありがとうございます。

自動車開発、コード解析、並列処理など質問や疑問に思ったことなどあれば

いつでもお待ちしております![]()