Western DigitalのRISC-V Core 「SweRV (スワーヴ)」がgithubで公開され、誰でも見られるようになりました。

ライセンスはApache2.0で、SystemVerilogで記述されています。

https://github.com/westerndigitalcorporation/swerv_eh1

docs/ 以下にマニュアルがあります。

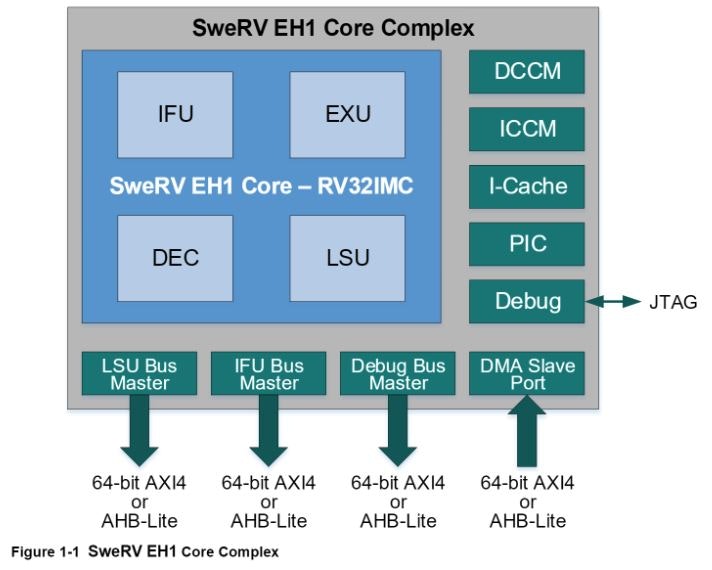

SweRV EH1 Core Complex

整数演算に特化した32bit RISC-Vです。

パラメタ指定により機能をカスタマイズできるようになっています。

出典:Western Digital "RISC-V SweRVTM EH1 Programmer's Reference Manual Revision 1.0"

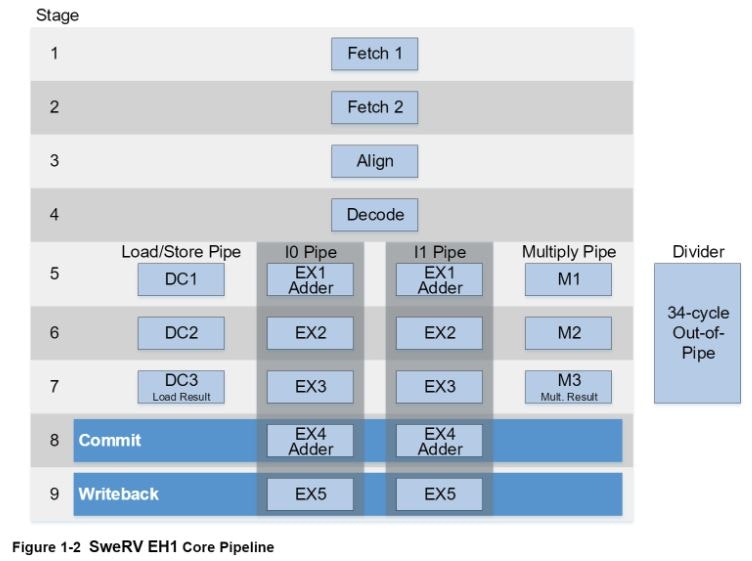

SweRV EH1 Core Pipeline

パイプラインは9段です。除算は別になっています。

出典:Western Digital "RISC-V SweRVTM EH1 Programmer's Reference Manual Revision 1.0"

ASICを前提としているので、FPGA向けにすぐ実機で動かせるというわけではなさそうです。

Verilator, vcs(Synopsys), irun(Cadense)に対応しています。