FPGAホントに何も分からんので,調べながら動かしてみて記録を残します.

な,なんとWindows11でやります.

使う物

- EBAZ4205(XC7Z010が載っている中古ボード)

- 拡張ボード(2022年6月頃からAliexpressで流通し始めたボード)

- XILINX互換のJTAGデバッガ(筆者の環境では特にドライバなど必要なかった)

拡張ボード

HDMIコネクタや,1.3インチLCDが載っている.このボードのUSB TypeC端子からFPGAボードへも電源供給できる.

シルク印刷でFPGAのどのポートに対応するかが書いてあり好感が持てる.

電源は,FPGAボードからピンヘッダ経由でもらうか(ボードの改造必要),USB TypeCケーブルで5Vを給電する.ボード上に1117-3.3が載っており,3.3Vを生成できる.

| FPGAピン番号 | 名前 | デバイス |

|---|---|---|

| E19 | ユーザLED1 | LED |

| K17 | ユーザLED2 | LED |

| H18 | ユーザLED3 | LED |

| T19 | KEY1_T19 | SW |

| U20 | KEY3_U20 | SW |

| P19 | KEY2_P19 | SW |

| U19 | KEY4_U19 | SW |

| V20 | KEY5_v20 | SW |

| D18 | DEEP_D18 | ブザー |

| ~ | ~ | HDMIコネクタ |

| ~ | ~ | 1.3”LCD |

買った物のチェック

拡張ボードは,中国で趣味の人が適当に格安PCBで作ったものと思われる.従って,はんだ付けに問題がないかを通電前にチェックした方がよさそうです.

お勉強開始

1:Linux起動

最初からFlashにLinuxが入っているので,電源を入れればLinuxが起動します.

FPGAボードのピンヘッダJ7経由でUART接続(デフォルトで115200だった)すればログインできますが,passwordの問題などで,ひと手間必要です.

参照ウェブサイト

2:VivadoでPL側の開発

SoCの選択は,XC7Z010CLG400-1.

Lチカとかなんとか

拡張ボードのスイッチKEY1_T19と,FPGAボードのRJ45横にあるLED(緑)を使ってLED ON/OFFしてみる.

| FPGAピン番号 | デバイス | 分類 |

|---|---|---|

| W13 | LED(Green) | FPGAボード |

| U19 | KEY1_T19 | 拡張ボード |

module key2led(

input sw1,

output led1

);

assign led1 = sw1;

endmodule

set_property IOSTANDARD LVCMOS33 [get_ports sw1]

set_property IOSTANDARD LVCMOS33 [get_ports led1]

set_property PACKAGE_PIN W13 [get_ports led1]

set_property PACKAGE_PIN U19 [get_ports sw1]

参照ウェブサイト

(1)vivadoでプロジェクトを作る(Spartan7向け解説)(2)Vivadoの基本的な使い方の説明

はまったこと

- XILINX(パチモン)のプログラマHS-2を接続しただけではFPGAボードに電源が入らない(拡張ボードのUSBから給電した)

- FPGAボードのスイッチS2,S3はPL側から触れない

タイマー

FPGAボードにX3が実装されていないので,なんらかの方法でクロックを持ってくる必要がある.

筆者の入手したFPGAボードにはY3(イーサネット用の25MHz)が実装されていた(実装されていない場合もあるらしい)のでこれが使える.やった~

水晶(Y3)とFPGA(U31)とをつなぐチップ抵抗R1485(FPGAボード裏面にある)が実装されていないので,0オームのチップ抵抗を付けるか,はんだでジャンパする.ジャンパするとFPGAのU18ポートにクロックが入る.電圧レベルは要確認(筆者はLVCMOS15にした).

※ 手元にY3が実装されていないボードもあったので見てみると,こちらはR1485が実装されていた.このボードには2つある冷却ファンコネクタにつながるSPEED信号?用のフォトカプラも実装されていない.

| FPGAピン番号 | デバイス | 分類 |

|---|---|---|

| U18 | Y3(XOUT.0) | FPGAボード |

| E19 | LED1 | 拡張ボード |

| K17 | LED2 | 拡張ボード |

| H18 | LED3 | 拡張ボード |

| U20 | KEY3 | 拡張ボード |

module l_chika(

input clk, //from OCR

input resetKey,

output led1,

output led2,

output led3

);

wire clk1Hz;

reg [2:0] pattern;

clkdiv clkdiv1(.ck(clk), .max(26'd25_000_000), .tc(clk1Hz));

always @(posedge clk1Hz)begin

if(!resetKey)

pattern <= 3'b000;

else

pattern <= pattern + 1'b1;

end

assign led1 = pattern[0];

assign led2 = pattern[1];

assign led3 = pattern[2];

endmodule

module clkdiv(

input ck,

input [25:0] max,

output tc

);

reg [25:0] count;

always @(posedge ck)begin

if(count > max)

// if(tc == 1'b1)

count <= 26'd0;

else

count <= count + 26'd1;

end

assign tc = (count == max);

// assign tc = (count >= max) ? 1'b1 : 1'b0; //これだとダメだった

endmodule

スーパー はまったこと

-

clkdivの2か所について当初は,上に掲載したリストのコメントアウトした部分のような記述をしていたが,それだと うまく動かなかった.

GOWINでは動いたのに,なぜだめなんだろう… - 当初,ILA(ロジアナ)がうまく動かなかった.本に書いてある通りJTAGクロック速過ぎが原因.15MHz→10MHzにしたら,動きました.本当にありがとうございました(K).

プログラマがパチモンだからでしょうね.

HDMIコネクタから出力

本(K)のHDMI出力をやってみる.

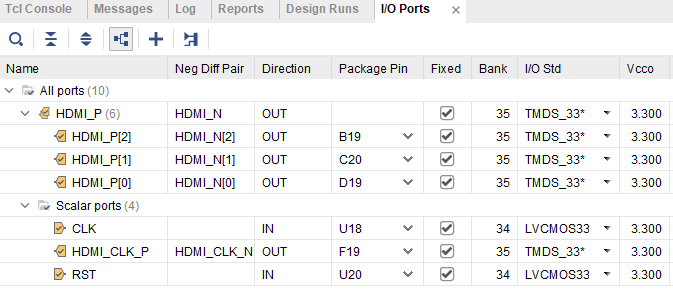

I/Oポートは次の通り.

| FPGAピン番号 | 信号 | I/O Std |

|---|---|---|

| U20 | RST | LVCMOS33 |

| B19 | HDMI_P[2] | TMDS_33* |

| C20 | HDMI_P[1] | TMDS_33* |

| D19 | HDMI_P[0] | TMDS_33* |

| U18 | CLK | LVCMOS33 |

| F19 | HDMI_CLK_P | TMDS_33* |

クロックは25MHzを入れるので,乗数を調整する.

省略

module pckgen (

input SYSCLK,

output PCK

);

wire CLKFBOUT, iPCK, locked;

BUFG iBUFG (.I(iPCK), .O(PCK));

MMCME2_BASE #(

.BANDWIDTH("OPTIMIZED"),

.CLKFBOUT_MULT_F(36.0), // 乗数M(2.000-64.000)

.CLKFBOUT_PHASE(0.0),

.CLKIN1_PERIOD(40.0), // CLKINの周期 modified: 8 -> 40

.CLKOUT1_DIVIDE(1),

.CLKOUT2_DIVIDE(1),

.CLKOUT3_DIVIDE(1),

.CLKOUT4_DIVIDE(1),

.CLKOUT5_DIVIDE(1),

.CLKOUT6_DIVIDE(1),

.CLKOUT0_DIVIDE_F(35.75), // 除数Q(1.000-128.000)

.CLKOUT0_DUTY_CYCLE(0.5),

.CLKOUT1_DUTY_CYCLE(0.5),

.CLKOUT2_DUTY_CYCLE(0.5),

.CLKOUT3_DUTY_CYCLE(0.5),

.CLKOUT4_DUTY_CYCLE(0.5),

.CLKOUT5_DUTY_CYCLE(0.5),

.CLKOUT6_DUTY_CYCLE(0.5),

.CLKOUT0_PHASE(0.0),

.CLKOUT1_PHASE(0.0),

.CLKOUT2_PHASE(0.0),

.CLKOUT3_PHASE(0.0),

.CLKOUT4_PHASE(0.0),

.CLKOUT5_PHASE(0.0),

.CLKOUT6_PHASE(0.0),

.CLKOUT4_CASCADE("FALSE"), counter with CLKOUT6 (FALSE, TRUE)

.DIVCLK_DIVIDE(1), // 除数D(1-106) modified: 5 -> 1

.REF_JITTER1(0.0),

.STARTUP_WAIT("FALSE")

)

省略

はまったこと

-

RSTは拡張ボードに載っているU20(真ん中のSW)を使ったが,負論理で入ってくるので,RSTを反転する必要があった.

// 中略

module pattern_hdmi(

input CLK,

input RST,

output HDMI_CLK_N, HDMI_CLK_P,

output [2:0] HDMI_N, HDMI_P

);

wire [7:0] VGA_R, VGA_G, VGA_B;

wire VGA_HS, VGA_VS, VGA_DE;

wire PCK;

/* パターン表示回路を接続 */

pattern pattern(

.CLK (CLK),

.RST (!RST),

.VGA_R (VGA_R),

.VGA_G (VGA_G),

.VGA_B (VGA_B),

.VGA_HS (VGA_HS),

.VGA_VS (VGA_VS),

.VGA_DE (VGA_DE),

.PCK (PCK)

);

/* HDMI信号生成IPを接続 */

rgb2dvi #(

.kClkPrimitive("MMCM"),

.kClkRange (5) // 25MHz <= fPCK < 30MHz

)

rgb2dvi (

.PixelClk (PCK),

.TMDS_Clk_n (HDMI_CLK_N),

.TMDS_Clk_p (HDMI_CLK_P),

.TMDS_Data_n(HDMI_N),

.TMDS_Data_p(HDMI_P),

.aRst (!RST),

.vid_pData ({VGA_R, VGA_B, VGA_G}),

.vid_pHSync (VGA_HS),

.vid_pVDE (VGA_DE),

.vid_pVSync (VGA_VS)

);

endmodule

参考サイト

(0)最初に入っているLinuxを起動するまで

https://qiita.com/kan573/items/e951a0b2e26e19372800?fbclid=IwAR3qXkam8JYXEdgwCZnrj3w2LtefPr4k31XmNbkINB4AlkgZWqxhx_X3u2c

(1)vivadoでプロジェクトを作る(Spartan7向け解説)

https://misoji-engineer.com/archives/xilinx-fpga.html

(2)Vivadoの簡単な使い方

https://miyo.github.io/learning_fpga/docs/book01/quickstart/

(A)マイコンでコンフィグ

https://zenn.dev/ciniml/articles/port-xvc-to-m5atom?fbclid=IwAR0NCxN3ckTmbE-3WAXauM1w9KNkM0M1UiMX-uPtYsjRwAxhd8nytgeAYJY

(B)FPGAプログラミング大全XilinxをEBAZ4205で楽しむ話

https://qiita.com/kan573/items/c4dac8908e1a86d8fce6

(C)図面とか

https://github.com/xjtuecho/EBAZ4205/tree/d41c46c1b50a12b513990dcb102a621e5fdcfe08

(D)WiKi

https://github.com/xjtuecho/EBAZ4205/wiki

(E)EBAZ4205用PetaLinux

https://github.com/KeitetsuWorks/EBAZ4205

(F)ピン

https://qiita.com/kan573/items/3c1ca1c4cd7ff94da38c

(G)拡張コネクタDATA1~DATA3とFPGAのピン番号の関係

https://qiita.com/kan573/items/44ced51037d221a4d171

(H)FPGAでHDMIから画像出力!フリーのIPを使ってみた

https://misoji-engineer.com/archives/fpga-hdmi.html

(I)Aliexpress販売元と拡張ボード回路図

https://ja.aliexpress.com/item/1005004460394748.html?spm=a2g0o.order_list.0.0.6185585apcm9mX&gatewayAdapt=glo2jpn

(J)Vivado ロジックアナライザの実行手順

https://fpga.kice.tokyo/fpga/vivado-la

(K)小林 優;FPGAプログラミング大全Xilinx編第2版,秀和システム

(L)

http://www.hellofpga.com/index.php/2021/07/16/ebaz4205_source/

(M)写真集

https://fpga.tokyo/230602-2/