概要

はじめまして。投稿初心者です。

今回は、INTEL PAC WITH INTEL ARRIA® 10 GX FPGA というアクセラレーション用カードを活用して、その実行環境を Docker / コンテナ化するフローについて説明をしたいと思います。

実際にサーバーに INTEL PAC WITH INTEL ARRIA® 10 GX FPGA カードを挿入して、ホスト側からのカードの見え方など確かめてみたいと思います。

もくじ

1.検証環境

[2.FPGA を活用したアクセラレーション](#2-FPGA を活用したアクセラレーション)

[3.INTEL PAC WITH INTEL ARRIA® 10 GX FPGA のインターフェース](#3-INTEL PAC WITH INTEL ARRIA® 10 GX FPGA アーキテクチャ)

[4.INTEL PAC WITH INTEL ARRIA® 10 GX FPGA 開発環境について](#4-INTEL PAC WITH INTEL ARRIA® 10 GX FPGA 開発環境について)

5.Docker/コンテナ化の手順

[6.実行結果] (#6-実行結果)

7.まとめ

1.検証環境

・使用した FPGA アクセラレーションカード

-インテル社製 INTEL PAC WITH INTEL ARRIA® 10 GX FPGA を使用

-Acceleration Stack ver1.2.1

(Intel® Arria® 10 GX FPGA搭載)

Download Link : https://www.intel.com/content/www/us/en/programmable/products/boards_and_kits/dev-kits/altera/acceleration-card-arria-10-gx/getting-started.html

・使用したサーバー

SuperMicro社製 SYS-7049GP-TRT

・使用した OS 環境

— CentOS Linux version 7.6 kernel 3.10

・Dockerのインストール手順は、以下のサイトを参考にしました

https://qiita.com/bezeklik/items/a6a7335acaec12edda45

2.FPGA を活用したアクセラレーション

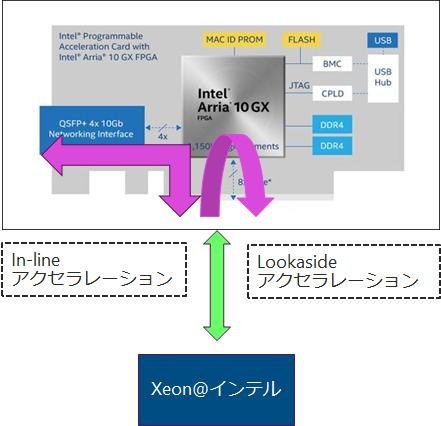

図のように、アクセラレーションの方式としては、2つの方式がある。

一つは In-line と呼ばれる、外部ネットワークインターフェースを持ち CPUの前後処理をアクセラレートする方法です。

もう一つは Lookasideと呼ばれる、外部ネットワークインターフェースを持たず PCIe 経由で CPU の処理を

アクセラレートする方法です。

INTEL PAC WITH INTEL ARRIA® 10 GX FPGA カードはその両方が実現できるカードです。

3..INTEL PAC WITH INTEL ARRIA® 10 GX FPGA のインターフェース

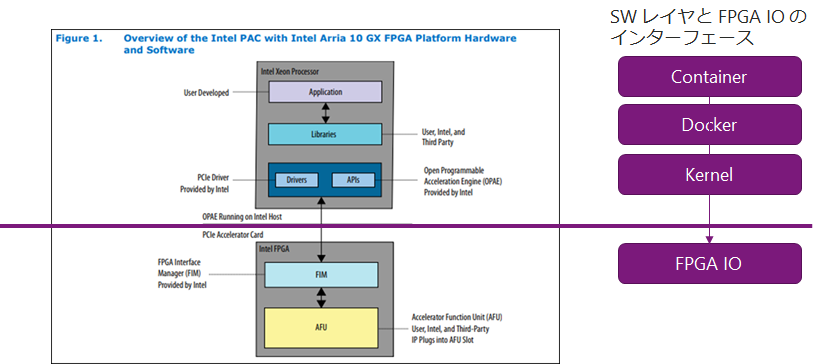

左図 Figure1 は、INTEL PAC WITH INTEL ARRIA® 10 GX FPGA カードの内部構造を示しています。

図の下側は FPGA ブロックを示します。FIMは FPGA Interface Manager の略で別名で Blue Bit stream と呼ばれ、

Intel 社から出荷時にプログラムされている領域です。上位の Xeon プロセッサとは、この FIM を介して通信を行います。

ユーザがプログラムできる領域は、現時点では黄色で示された AFU (Accelerator Function Unit)と呼ばれるブロックです。

図の右側には、SW レイヤと FPGA IO の関係を図示しました。

今回の記事の主要ポイントは、Docker/コンテナ化する際に、FPGA開発環境の IO と コンテナを結びつける作業になります。

Host 側からの FPGA IO の 見え方

Docker/コンテナ化の話に移る前に、FPGA の IF がどのように見えるのか、確認したいと思います。

以下のコマンドを使用して確認することができます。

crw------- 1 root root 234, 0 11月 26 17:26 ifpga_sec0

crw-rw-rw- 1 root root 236, 0 11月 26 17:26 intel-fpga-fme.0

crw-rw-rw- 1 root root 235, 0 11月 26 17:26 intel-fpga-port.0

Docker/コンテナ化する際に、上記の intel-fpga-fme.0, intel-fpga-port.0 とコンテナ環境を紐づける必要があります

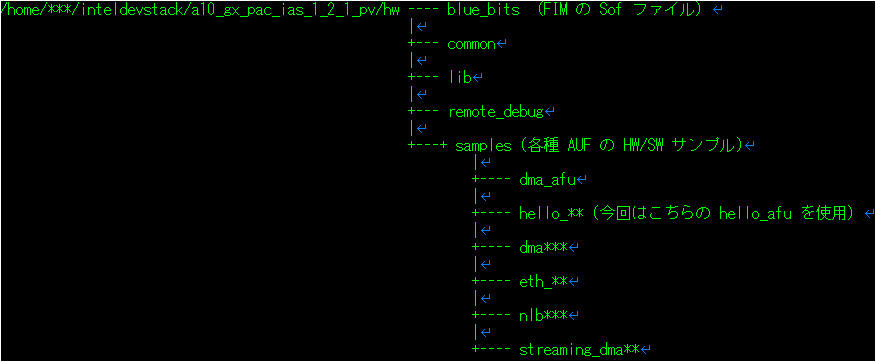

4.INTEL PAC WITH INTEL ARRIA® 10 GX FPGA 開発環境について

INTEL PAC WITH INTEL ARRIA® 10 GX FPGA の開発環境をインストールした後のフォルダ構成を以下に示します。

/home/***/inteldevstack/a10_gx_pac_ias_1_2_1_pv 配下に実行環境がインストールされます。今回は、

a10_gx_pac_ias_1_2_1_pv 配下の、 /sample/hello_afu/sw を使用してみたいと思います。

※上記のPathは、Acceleration stack for development の場合の Path です。

Acceleration stack for runtime の場合は、intelrtestack/がデフォルトの Path になります。

5.Docker/コンテナ化の手順

手順としては、

1.Acceleration stack をインストール (今回は Runtime をインストール)

※ Acceleration stackには2種類存在し、FPGA内部の開発をしない場合は、Runtime。

FPGA 内部の開発が必要な場合はDevelopmentを選択する

2.Docker Image のダウンロード

3.Docker Image の作成

の順で実施します。

前準備

//まずは前もって Acceleration Stack の 1.2.1 の Runtime をインストール

//前準備

$ cd /home/***/inteldevstack/a10_gx_pac_ias_1_2_1_pv/hw/samples/hello_afu

$ fpgaconf bin/***.gbs

$ cd sw

$ make

Docker 環境のダウンロードと作成

$ docker pull centos:centos7

$ docker run --rm -it \

--name intel_pac \

--mount type=bind,source=/home/***/inteldevstack,destination=/inteldevstack \

--mount type=bind,source=/usr/lib64,destination=/usr/lib64 \

--device /dev/intel-fpga-fme.0:/dev/intel-fpga-fme.0 \

--device /dev/intel-fpga-port.0:/dev/intel-fpga-port.0 \

--cap-add=IPC_LOCK \

centos:centos7

--mount type=bind にて、inteldevstack および usr/lib64 を Docker 内にマウントします。

Docker 内にアクセラレーションスタックをインストール後にIOのみ割りつける方法もありますが、

今回は Host にアクセラレーションスタック開発環境をインストール後に、Dockerにマウントする方法を試しました。

以下のコマンドで、前述した FPGA IO と Docker 環境の紐づけを行っています。

--device /dev/intel-fpga-fme.0:/dev/intel-fpga-fme.0 \

--device /dev/intel-fpga-port.0:/dev/intel-fpga-port.0 \

上記にて、INTEL PAC WITH INTEL ARRIA® 10 GX FPGA 開発環境の Docker 化ができましたので、

Softwareを実際に実行した結果を以下に示します。

6.実行結果

Docker Image ダウンロード

$ docker pull centos:centos7

centos7: Pulling from library/centos

Digest: sha256:0f4ec88e21daf75124b8a9e5ca03c37a5e937e0e108a255d890492430789b60e

Status: Image is up to date for centos:centos7

docker.io/library/centos:centos7

Docker の起動

$ docker run --rm -it \

> --name intel_pac \

> --mount type=bind,source=/home/***/inteldevstack,destination=/inteldevstack \

> --mount type=bind,source=/usr/lib64,destination=/usr/lib64 \

> --device /dev/intel-fpga-fme.0:/dev/intel-fpga-fme.0 \

> --device /dev/intel-fpga-port.0:/dev/intel-fpga-port.0 \

> --cap-add=IPC_LOCK \

> centos:centos7

[root@7e83b4eac411 /]#

hello_afu Software フォルダに移動

cd /inteldevstack/a10_gx_pac_ias_1_2_1_pv/hw/samples/hello_afu/sw

[root@7e83b4eac411 sw]#

Software の実行

./hello_afu

Running Test

AFU DFH REG = 1000010000000000

AFU ID LO = 9722d43375b61c66

AFU ID HI = 850adcc26ceb4b22

AFU NEXT = 00000000

AFU RESERVED = 00000000

Reading Scratch Register (Byte Offset=00000080) = 00000000

MMIO Write to Scratch Register (Byte Offset=00000080) = 123456789abcdef

Reading Scratch Register (Byte Offset=00000080) = 123456789abcdef

Setting Scratch Register (Byte Offset=00000080) = 00000000

Reading Scratch Register (Byte Offset=00000080) = 00000000

Done Running Test

7.まとめ

・INTEL PAC WITH INTEL ARRIA® 10 GX FPGA は In-line/ lookaside に対応したカード

・FPGA 開発環境を Docker/コンテナ化するためには、FPGA IO と Docker 環境の紐づけが必要

・Docker 環境から SW を実行し FPGA アクセラレーションブロックに簡単にアクセスできた

※Docker 内にアクセラレーションスタックをインストール後にIOのみ割りつける方法もありますが、今回は Host にアクセラレーションスタック開発環境をインストール後に、Dockerにマウントする方法を試しました。

参考になりましたら幸いです。