はじめに

@piacerex さんの、ElixirChipの記事に現在のPCやクラウドの仕組みでは、構造的な課題があって、これを乗り越えるものができたらいいなぁ。という話があります。CPUの処理能力も頭打ちです。

昔回路設計とかFPGA使ったりしていたので、Elixir+FPGAでなにかできないか、妄想をしてみたいと思います。

この記事は、私の考えた妄想をChatGPTと話して、お手軽にできそうなことを文章化してみました。

事実とは異なる記述がある可能性もあるのでご了承ください。

ザックリした話をしてみる

こんな問いからはじめてみました

関数型の言語ElixirやBEAMの処理をハードウエアのオフロードする事を考えます

これに対して、ずらずら返信を返してきました。

「NIF(Native Implemented Function): ElixirはC言語などで書かれたネイティブコードを呼び出す機能を持つため、FPGAで実装された計算モジュールをNIF経由で呼び出し、ハードウェアオフロードが可能です。」

こんな文章がありました。NIFって使えそうかも。とおもったので、

NIFについて学びたい

概要を説明してもらいました。

あまりアイデアにつながるようなことはありませんでした。

NIFに関連して、無茶ぶりをしてみます

XlinxのツールのC言語で書いたものを論理合成するのがあるよね。これとNIFをくっつけられるといいね?

はい、その考え方は非常に興味深いです。Xilinxのツールには、C言語で記述したコードをFPGAの論理設計として合成するための HLS(High-Level Synthesis) ツールがあります。これを使用することで、C/C++コードをハードウェア記述言語(HDL)に変換し、FPGAで実行可能なハードウェアとして合成できます。

~~省略~~

このアプローチにより、Elixirアプリケーションで計算集約的な処理をハードウェアにオフロードし、パフォーマンスを大幅に向上させることが可能です。例えば、リアルタイム画像処理や暗号化プロセス、機械学習の推論などで有効です。

おお、何か褒められた感じ。

実際にハードウエアに落とす方法を模索したいので、関係しそうなところを攻めてみます。

Zynq-7010にハードウエアとARMコアから同時にアクセスできるRAM的なものなかったっけ?

はい、Zynq-7010には、FPGAロジックとARM Cortex-A9プロセッサの両方から同時にアクセス可能なPS(Processing System)- PL(Programmable Logic)間の共有メモリとして使用できるリソースが存在します。以下は、その詳細です。

OCM(On-Chip Memory)っていう名前なのね。もうちょっと深堀してみよう

NIFで受け渡すデータをOCMに置く方針はどう?

NIFを通じて受け渡すデータをZynq-7010の OCM(On-Chip Memory) に配置する方針は、非常に合理的なアプローチです。これにより、Elixir/ErlangアプリケーションとFPGAロジックの間で効率的なデータ共有と高速なアクセスが可能になります。以下にその利点と考慮点を説明します。

~~ 省略 ~~

合理的にできそうな感じになってきた。

さらに、無茶ぶりをしてみる

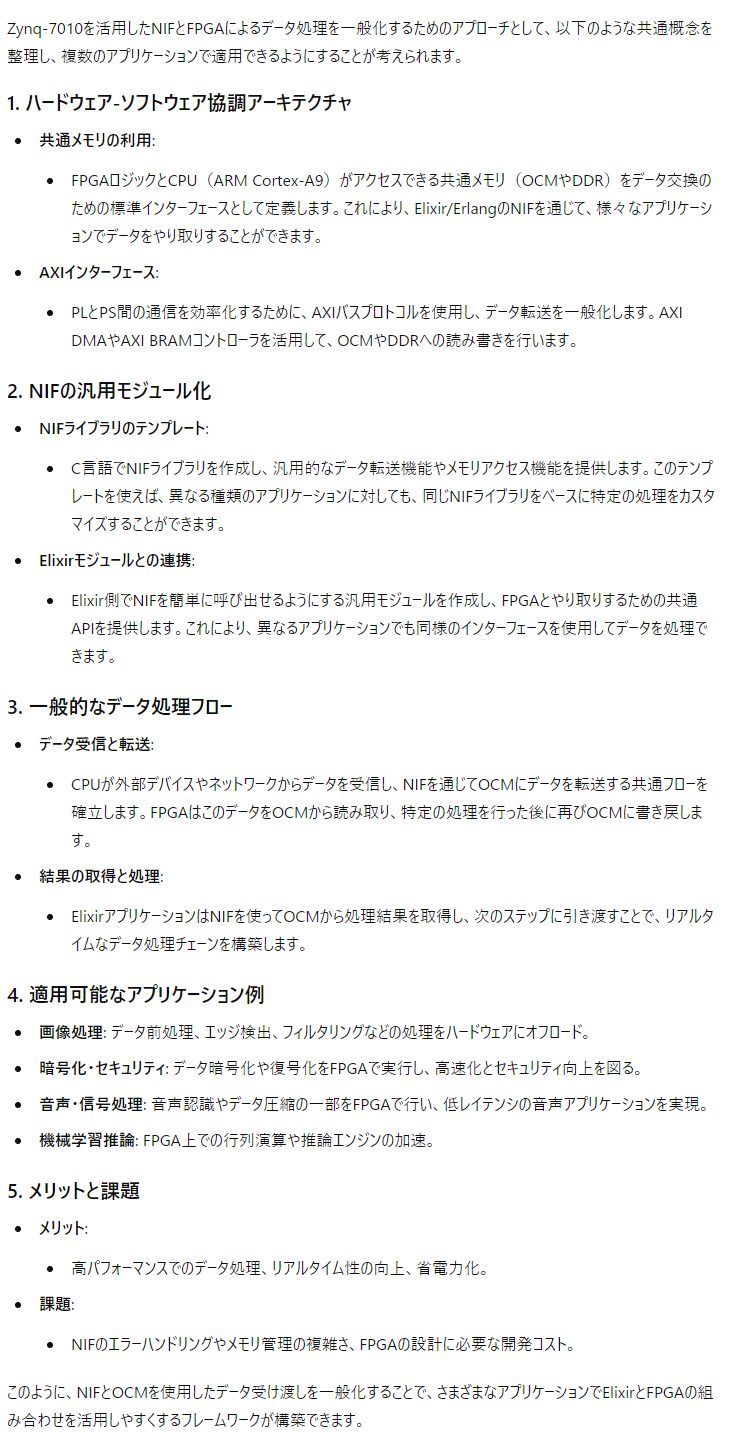

一般化できないかな?

簡単な例を示して、具体的な自実装例にもっていこう。

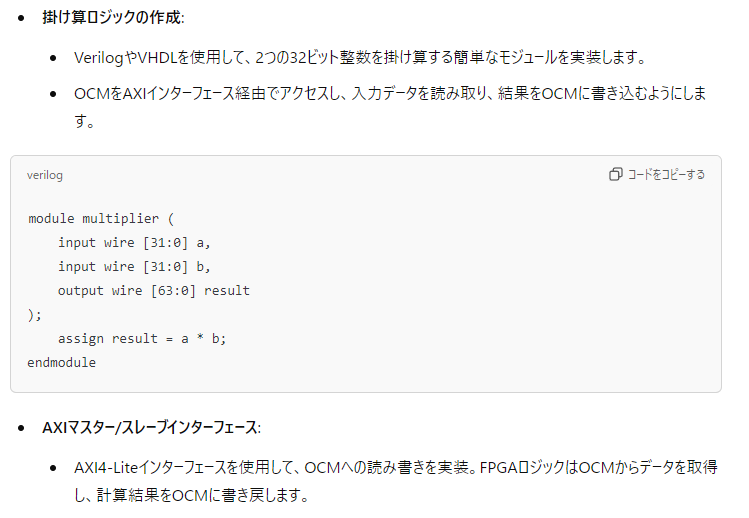

例えば、2つの32bit整数の掛け算を行う処理をFPGAで行い、ソフトウエアとしては、NIFを介在して、ハードウエアとしては、OCMを使ってやり取りする実装を考えてみて

ハードウェア側の設計(FPGA)

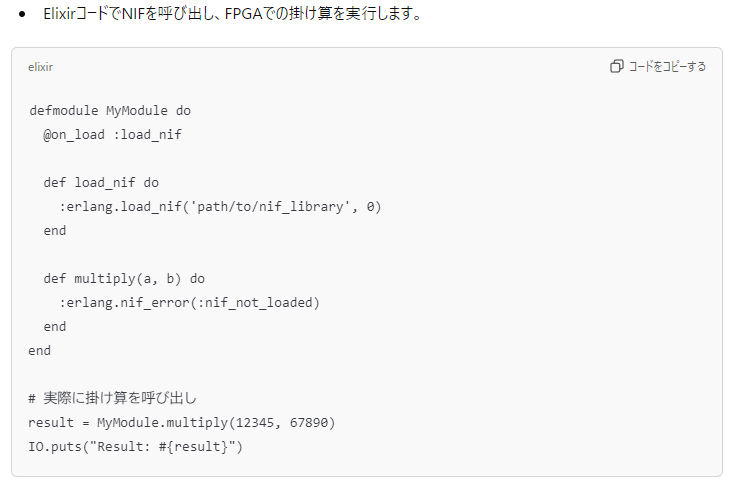

ソフトウェア側の設計(Elixir/NIF)

Elixirコード

まとめ

- ElixirとFPGAの間でデータをやりとりする部分について、妄想をしてみました

- Zynq-7010の学習も兼ねて、試してみる価値はありそうなお題ができました

- これを参考にして、Elixir+FPGAの可能性を試してみたいと思います