Windows 10 Pro (v1909)

PYNQ-Z1 (Digilent) (以下、PYNQと表記)

PYNQ v2.5 Image

Vivado v2019.1 (64-bit)

Analog Discovery 2 (以下、AD2)

概要

- GitHubで公開されているAXI UART liteのbistreamとPythonスクリプトを試す

- AD2でロジック電圧を確認

- AD2でロジックをキャプチャ

PMOD

PMODのピン配置は下記を参考にした。

GitHubコード

以下のファイルとフォルダを使った。srcにはPythonで定義したクラスがある。

- uartlitetest.tcl

- uartlitetest.bit

- src/

接続

- PMOD A:0 (RX)

- PMOD A:1 (TX)

これはGitHubのコードによって決まっている。

Jupyter Notebook

from pynq import Overlay

ol = Overlay("/home/xilinx/jupyter_notebooks/base/uartlitetest.bit")

ol.download()

from pynq import MMIO

from pynq import Overlay

import sys

sys.path.insert(1, 'base/src_AXI_UART_LITE_200813')

from uartlite import *

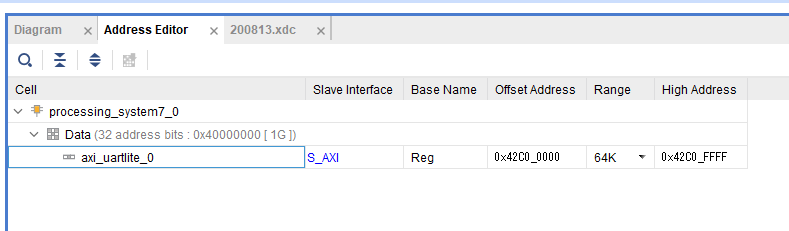

# Address of the ip core

ADDRESS = 0x42c00000

uart = UartAXI(ADDRESS)

# Setup AXI UART register

uart.setupCtrlReg()

import time

for idx in range(10):

print(idx)

uart.write('hello world\n')

sleep(1)

0

1

2

3

4

5

6

7

8

9

1秒ごとに出力されるので、その間にAD2でUART送信を確認する。

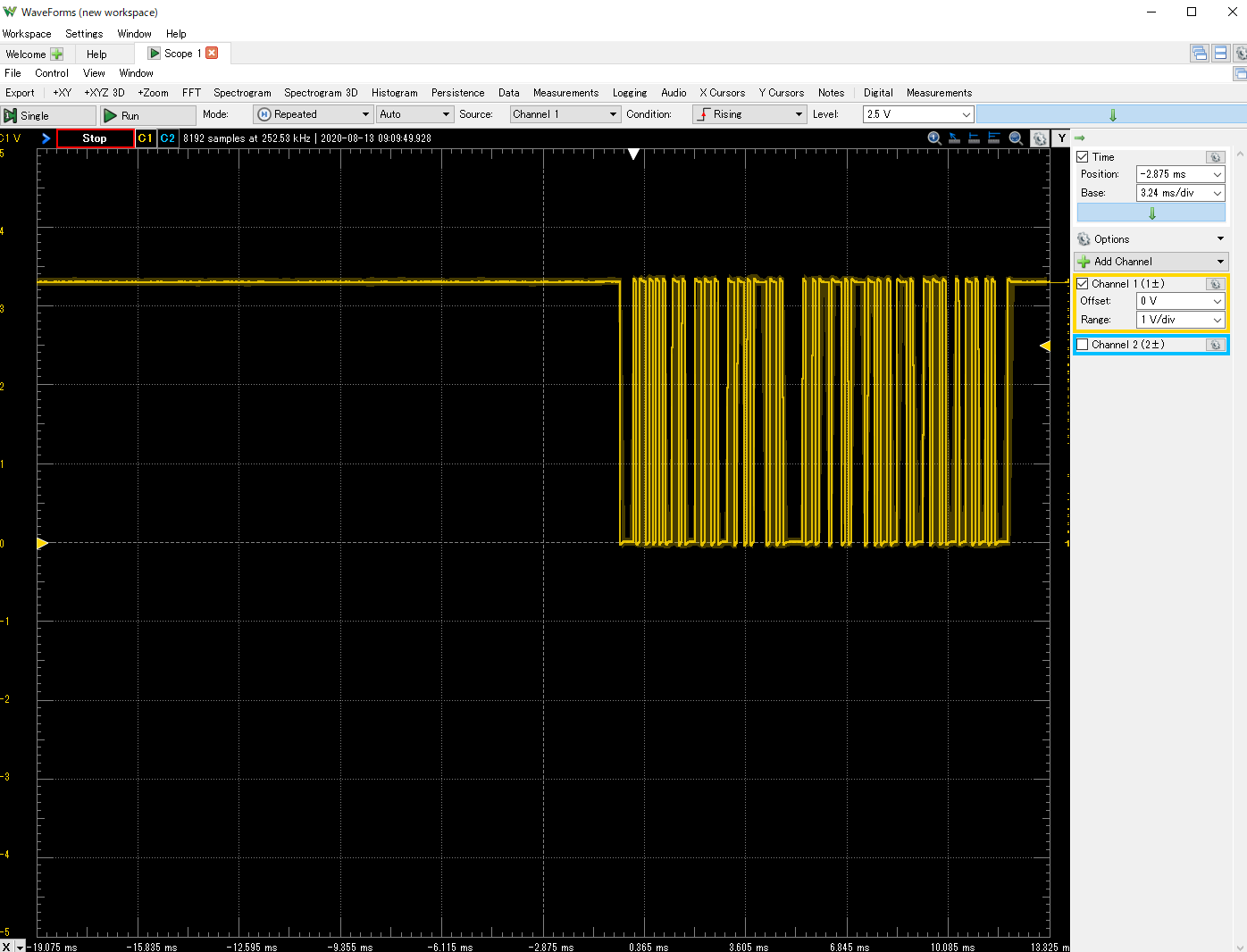

AD2 > Scope

AD2でScopeを用いて電圧を見た。

3.3V TTLレベルで動作している。

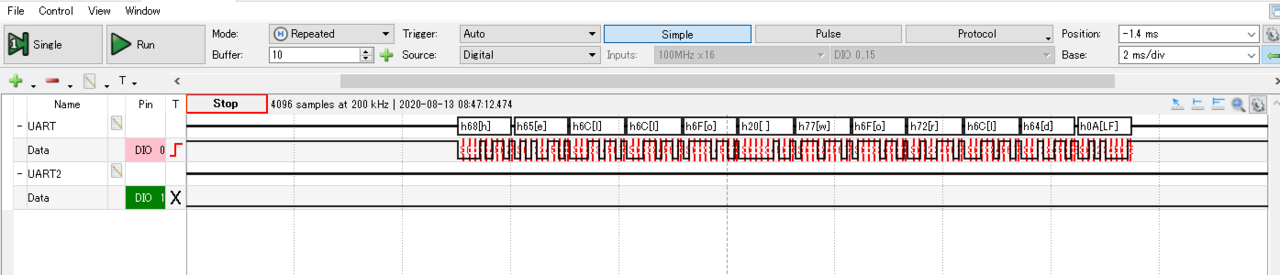

AD2 > Logic

AD2でLogicを用いて送信された文字をモニタした。

hello world<LF>が送信されていることを確認できた。

関連

- PYNQ-Z1 > SystemVerilog | UART > ボタン押下時にシリアルで0x41 ("A")を送信する (Tutorialの実行) | Jupyterの応答がなくなる

-

ZYBO / Pmod / UART > PmodからUART接続してみた (UARTLITE使用)

- 詳細に記載をしている

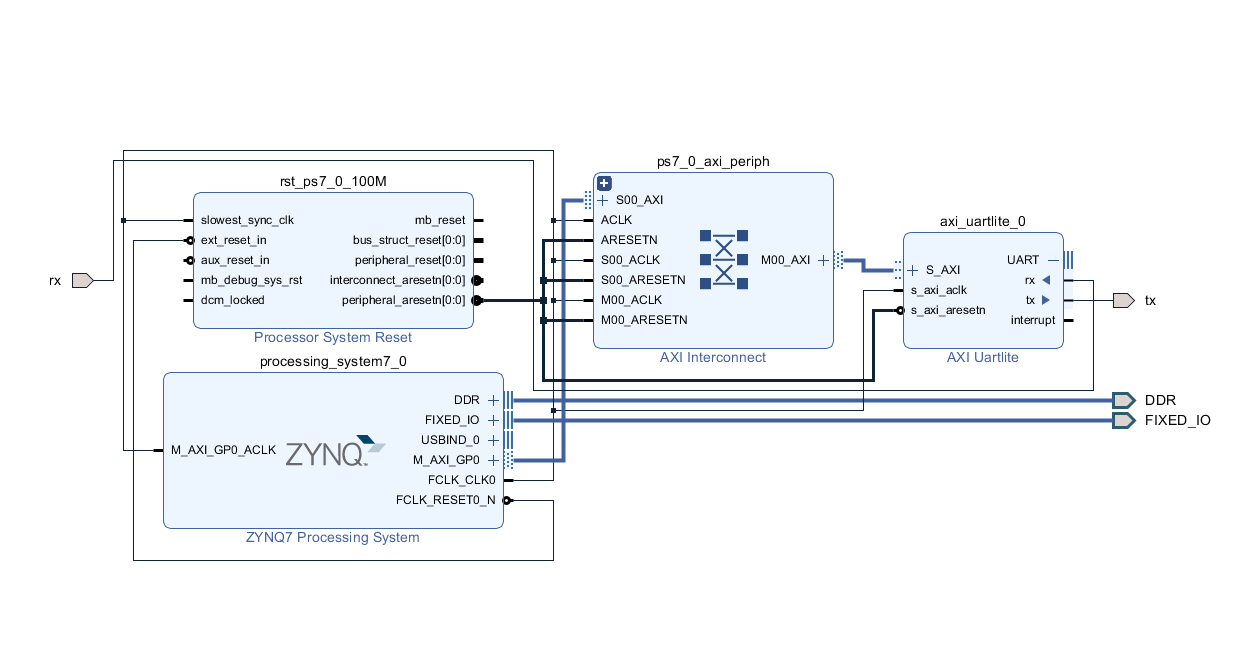

Block Design

GitHubのtclファイルをsourceコマンド読み自動生成されたBlock DesignはPYNQ-Z2用なのか、bitstream生成時に失敗する(tclはVivado v2019.2用だった)

。

[Board 49-71] The board_part definition was not found for tul.com.tw:pynq-z2:part0:1.0. The project's board_part property was not set, but the project's part property was set to xc7z020clg400-1. Valid board_part values can be retrieved with the 'get_board_parts' Tcl command. Check if board.repoPaths parameter is set and the board_part is installed from the tcl app store.

代わりに一からBlock Designを生成した (Vivado v2019.1使用)。

- PYNQ-Z1のプリセットをロード

- UART 0の制約ファイルを下記のようにする (PMOD Aの0,1を設定)

で動いた。

set_property IOSTANDARD LVCMOS33 [get_ports rx]

set_property IOSTANDARD LVCMOS33 [get_ports tx]

set_property PACKAGE_PIN Y18 [get_ports rx]

set_property PACKAGE_PIN Y19 [get_ports tx]

Block Designは下記となっている。

UARTのアドレスはデフォルトのままとした (0x42c00000)。