動作環境

Windows 10 Pro (v1909)

PYNQ-Z1 (Digilent) (以下、PYNQと表記)

PYNQ v2.5 Image

Vivado v2019.1 (64-bit)

概要

- 一つの入力(Slide SW)を一つの出力(RGBLED_R)につなげたい

- concatを1bit input, 1bit outputで使うとできた

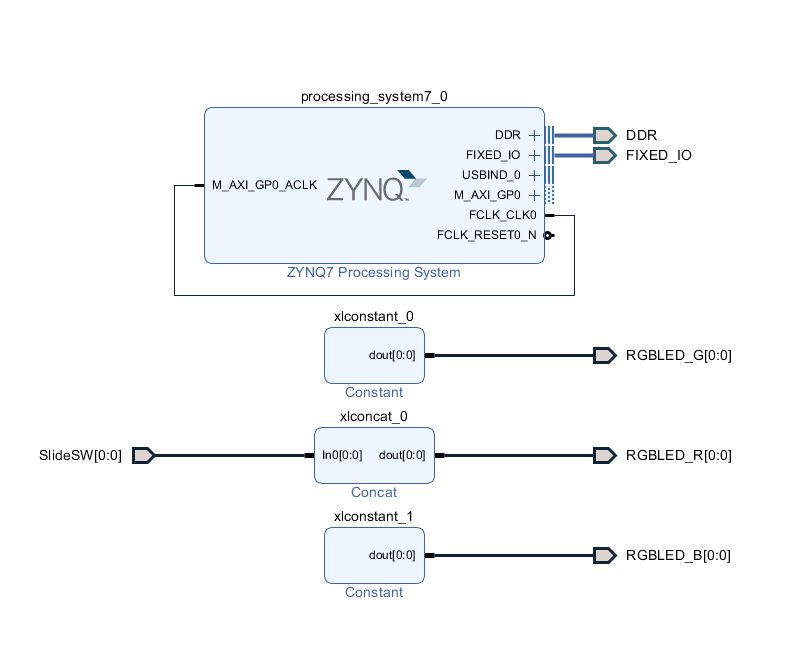

Block Design

Concat IP

Number of Portsを1に変更した。

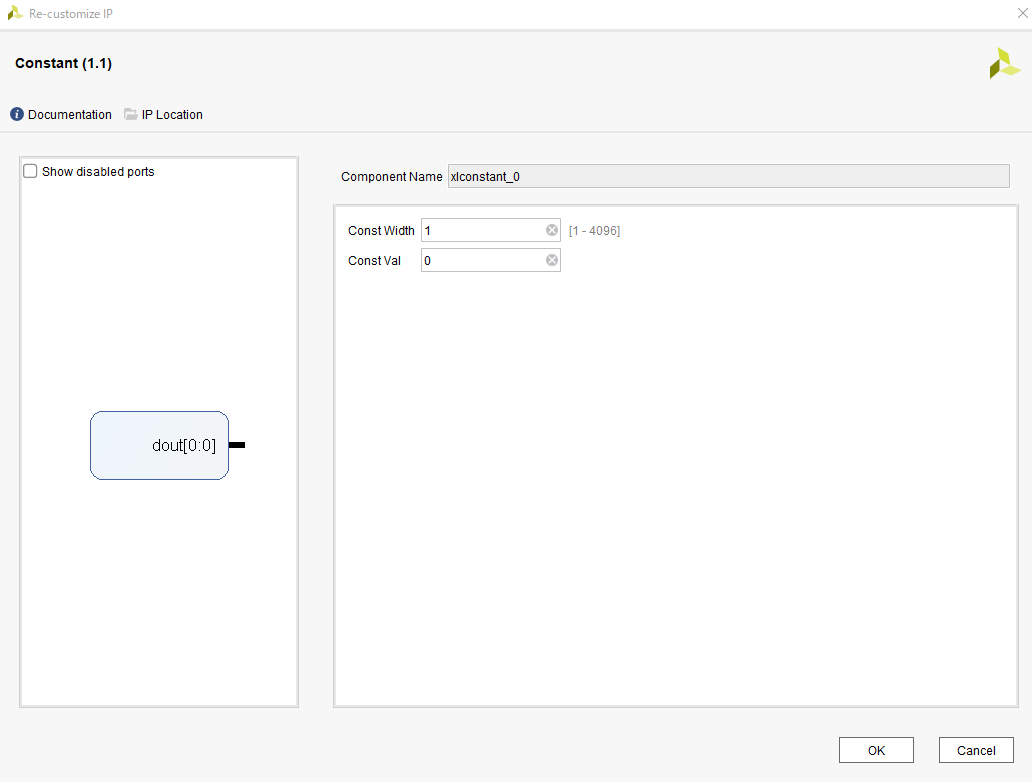

Constant IP

RGBLEDのGとBについてはConstant IPで固定。

Const Val=0としておく。

制約ファイル

Run Synthesisを実行後、I/O PortsにてSlide SWとRGBLEDのピンを指定する。

ZYNQ-Z1のプリセットファイル(PYNQ-Z1_C.xdc)にピンの記載があるので、それを参考にする

制約ファイル

set_property PACKAGE_PIN L15 [get_ports {RGBLED_B[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {RGBLED_B[0]}]

set_property PACKAGE_PIN G17 [get_ports {RGBLED_G[0]}]

set_property PACKAGE_PIN N15 [get_ports {RGBLED_R[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {RGBLED_G[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {RGBLED_R[0]}]

set_property PACKAGE_PIN M20 [get_ports {SlideSW[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {SlideSW[0]}]

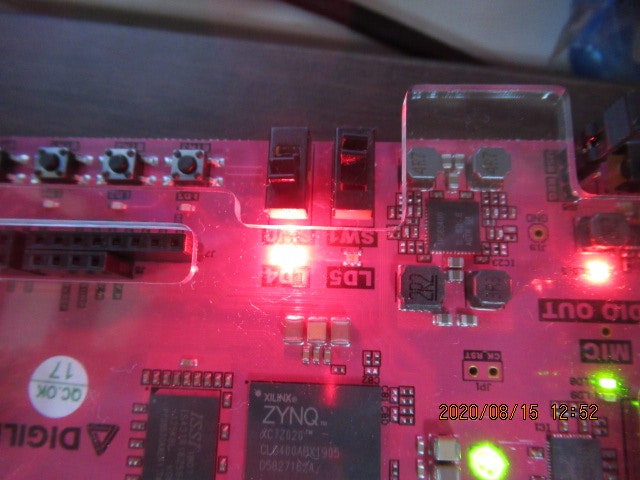

動作確認

上記にてbitstreamを生成した。

.tclファイルと.bitファイルをZYNQ-Z1のフォルダ(\\pynq\xilinx\jupyter_notebooks\base)にコピーした (Explorerで\\pynqに接続してフォルダ選択)。

Python

Jupyter Notebookにて下記を実行した。

from pynq import Overlay

ol = Overlay("/home/xilinx/jupyter_notebooks/base/slideSW_RGBLed_200815.bit")

その他

- Concatの代わりにSliceを使おうともしたが、Sliceだと1bit inputは設定できなかった

補足

Slide SWのON/OFFによる処理の開始(PL)は別にConcat IPを使わないで、直接対象のIPのピンにMake Externalすればいいかな。

RGBLED_Rへの出力と、別のRTLのenableと結線するのはするかもしれない。