この記事は何か

この記事はLSIにおけるCMOSプロセスの構造について多少なりとも知見がある人向けです。

尚、間違いを発見したら教えていただけると幸いです。

それなりに電子工作をしたことがある人はMOSFET使って回路を組んだことがあるかと思います。

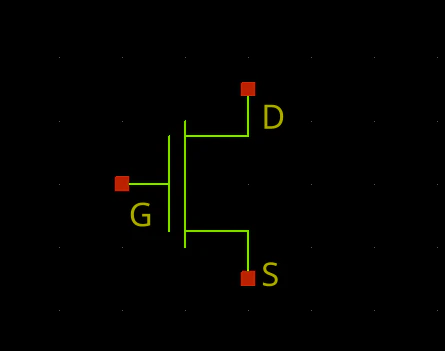

世間一般のMOSFETはドレイン・ソース・ゲートの3端子で構成されます。

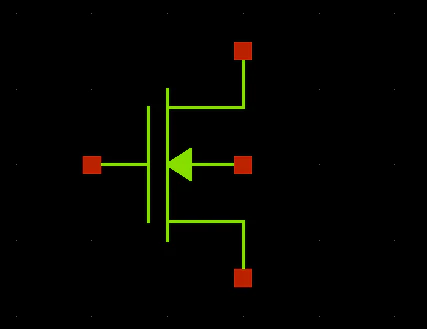

ところがCMOSプロセスのIC設計ではドレイン・ソース・ゲートに加えて謎の4端子目が出現します。

このドレインとソースの間にある矢印つきの端子が4端子目で、ボディとかバルクとかバックゲートとか基板とかサブストレートとかウェルなど…様々な呼び名があります。著者の周りではバックゲートという呼び名が主流なのでこの記事ではバックゲートと呼ぶことにします。

このバックゲートが何者かについて調べてみても正直よくわからないというか、お茶を濁されているというか、イマイチよくわかりません。「バックゲートのバイアス電圧によってIdsが変わる」以上の理解がなかなか難しく、しかし市販のMOSFETはバックゲートとソースがくっついていて実験できません。

そんな皆様に朗報です。

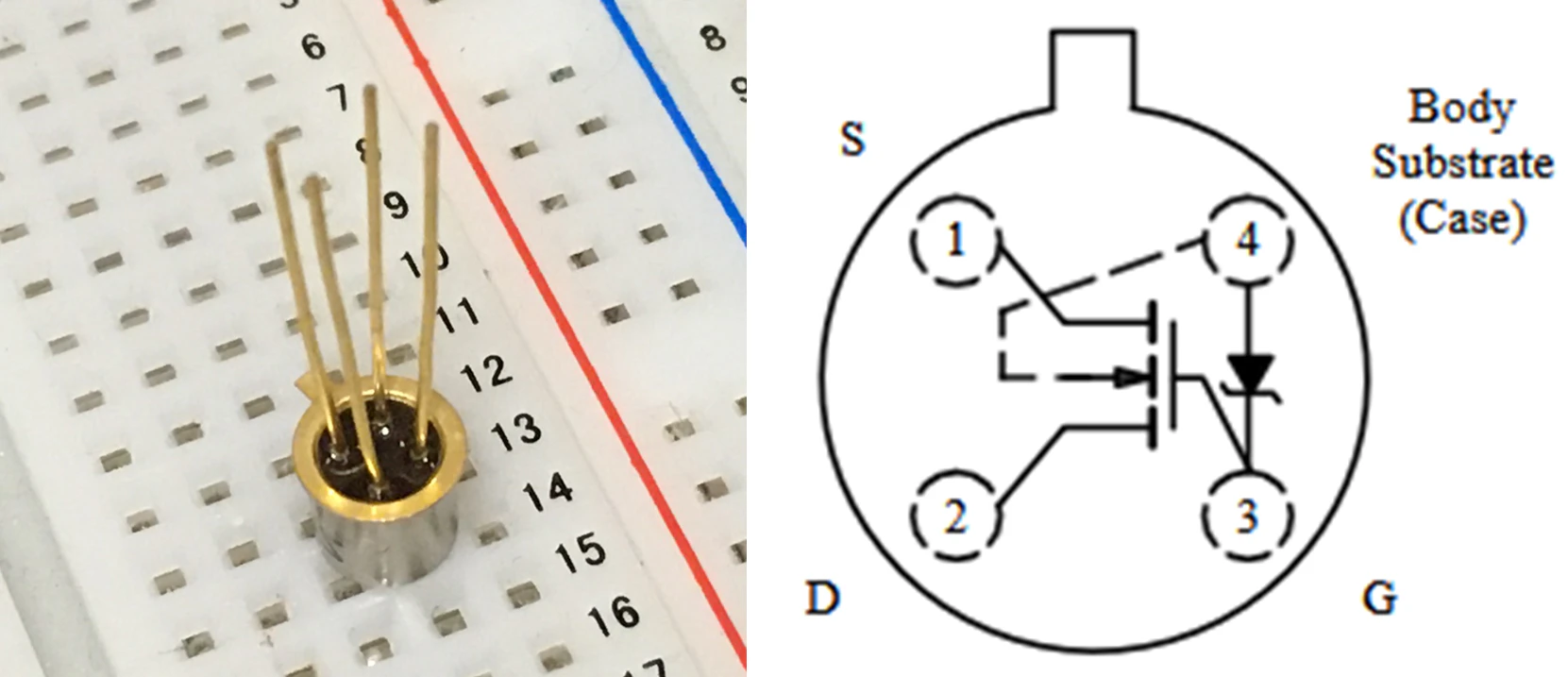

バックゲートとソースが分離した4端子のディスクリートNch MOSFETを入手しました。

※ヤフオクで2個550円でした。

いろいろ実験してデータを取ってみたので記事にしました。

今回手に入れたMOSFETはLDMOSと呼ばれる構造の素子です。LDMOSはドレインとソースが非対称構造となっているためIdsとIsdの両方を測定しています。詳しくは補遺にて。

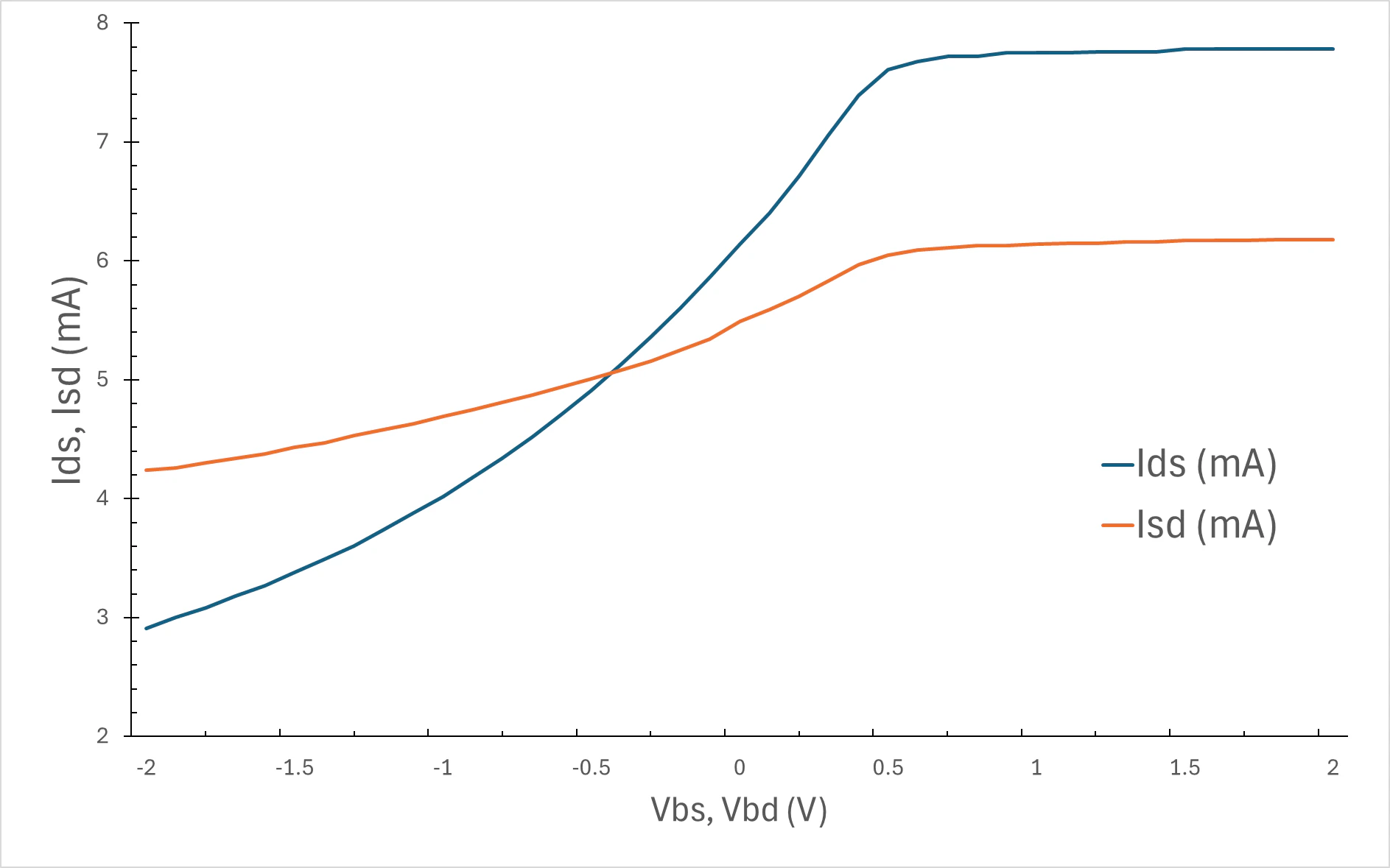

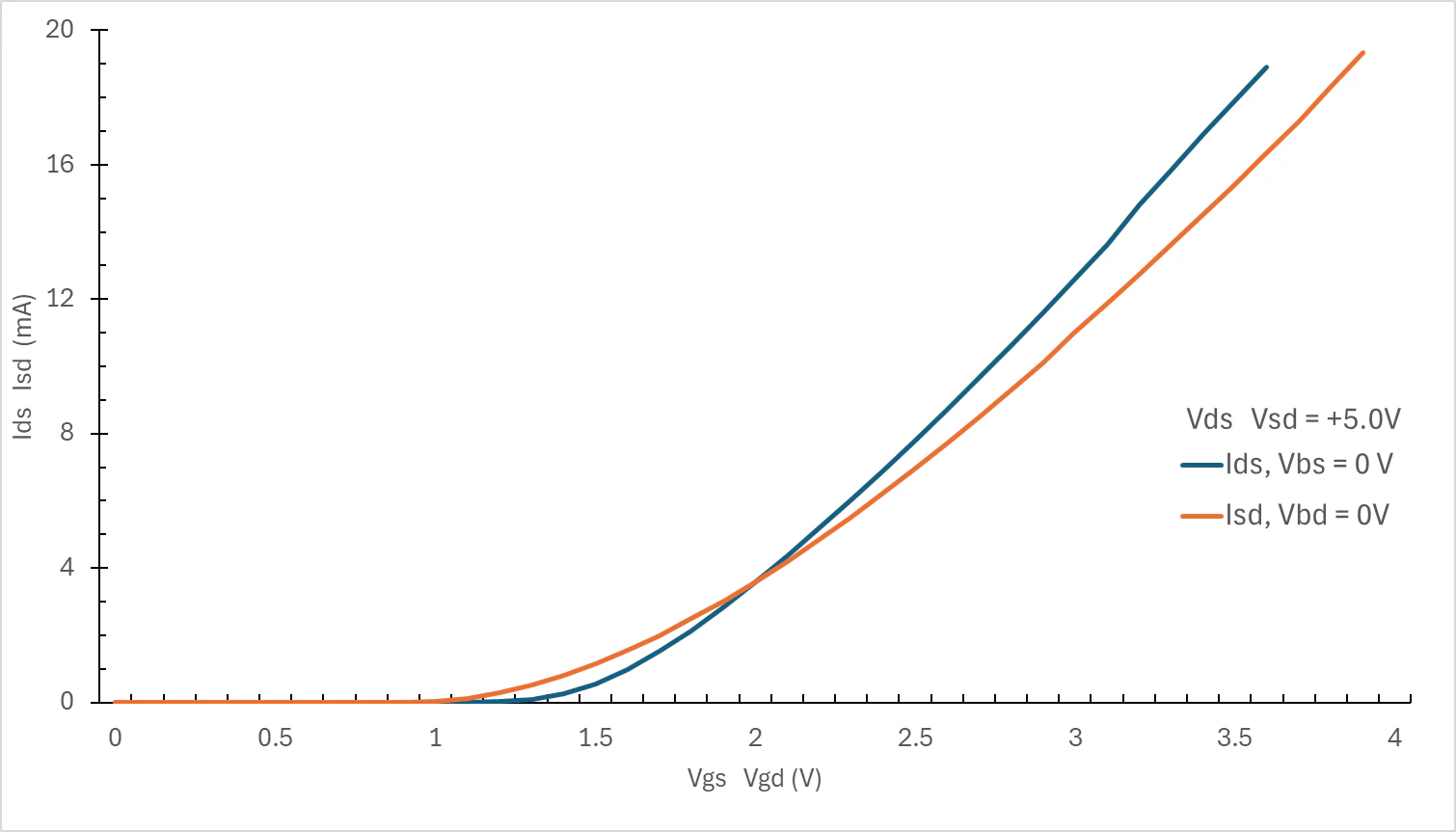

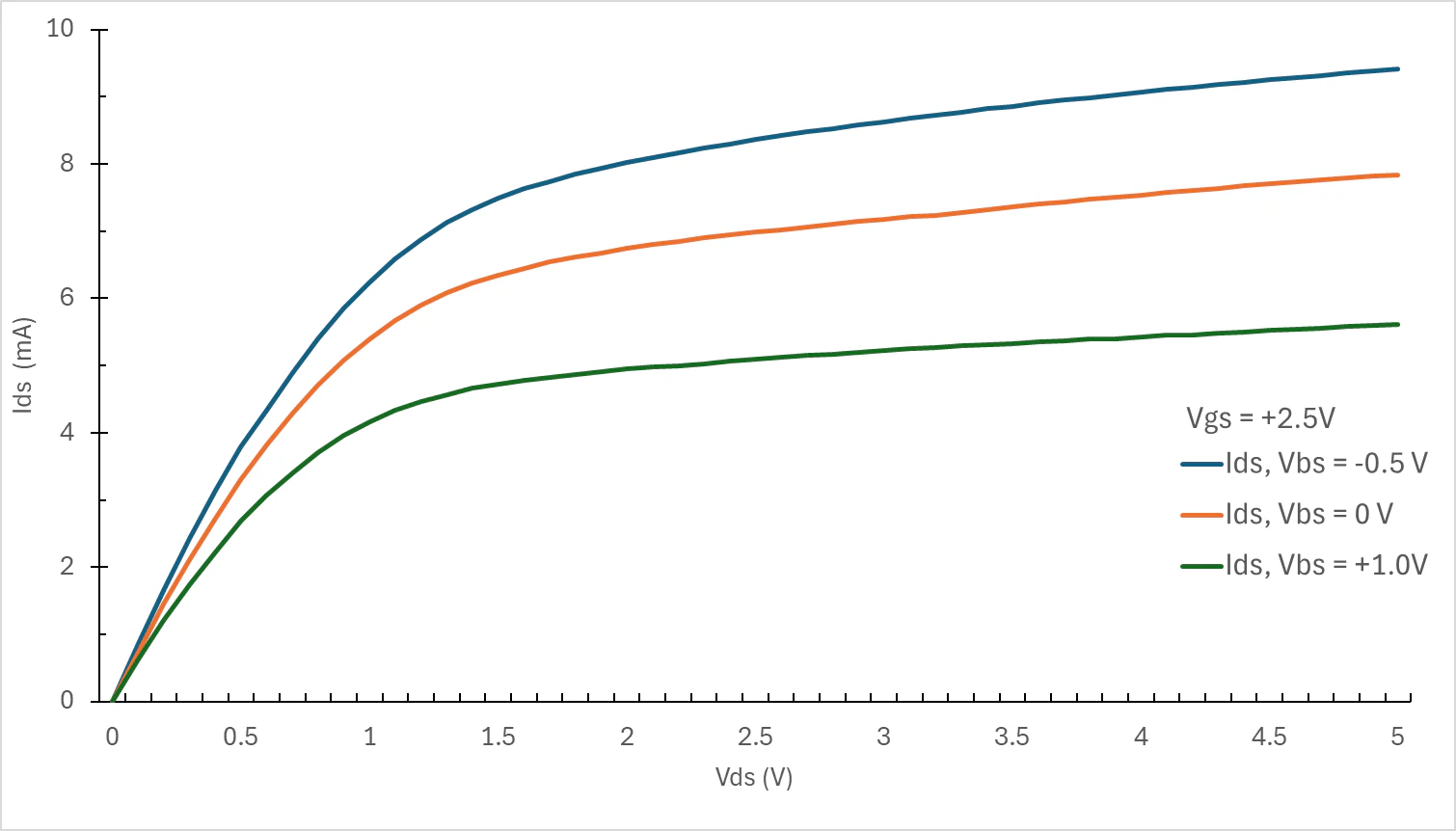

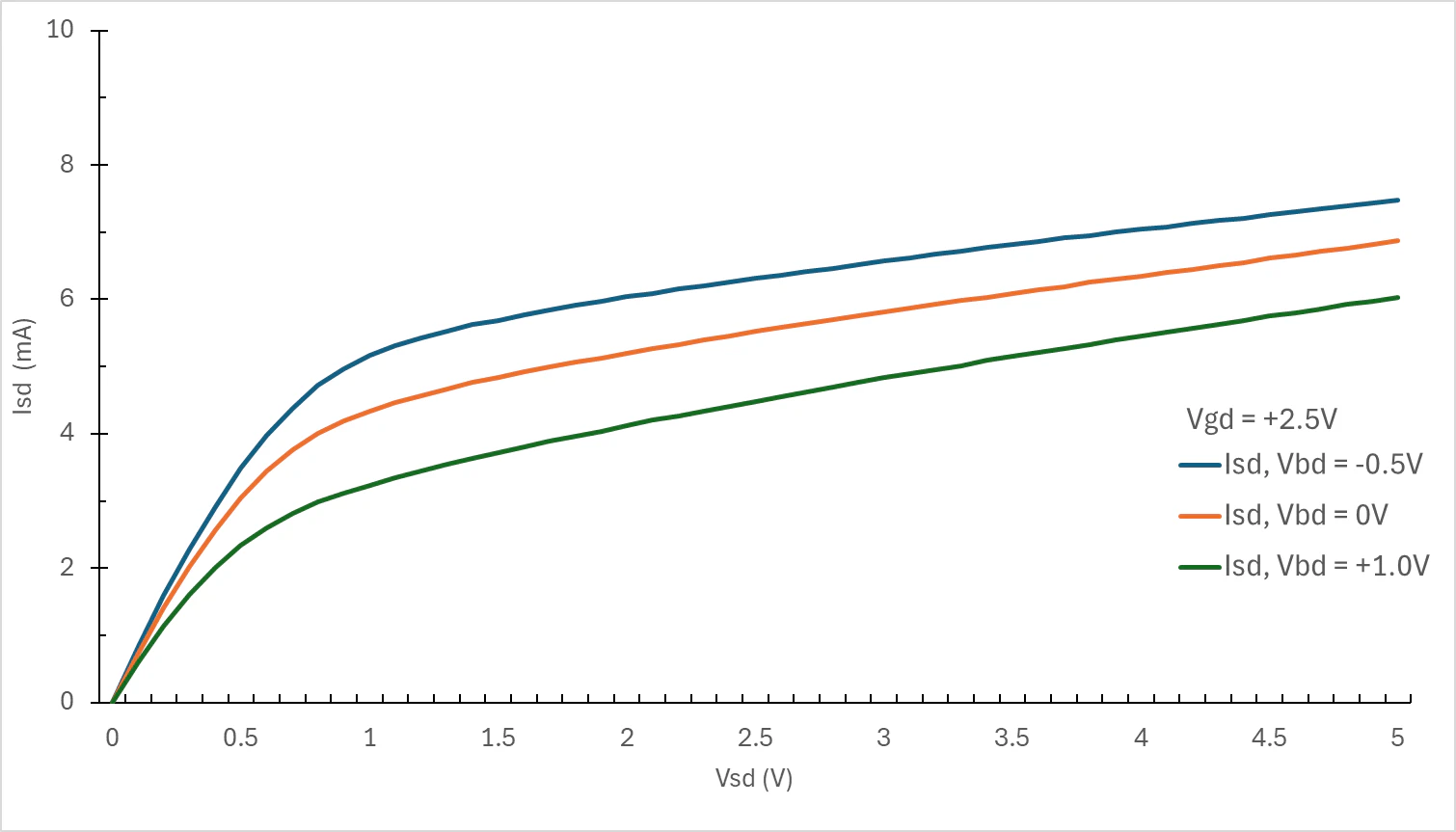

Nch LDMOS: Vbs-Ids, Vbd-Isdカーブ

世にも珍しい実測値によるVbs-Idsカーブです。Vgs-Idsカーブ、Vds-Idsカーブは見た事あってもVbs-Idsカーブを見た事ある人は殆どいないのではないでしょうか。

Vbs-Ids測定条件は Vds=5V, Vgs=2.5Vです。Vbd-Isdカーブはソースとドレインが入れ替わっており、Vds=-5V (Vsd=5V)、Vgd=2.5Vとなっています。測定したカーブがなだらかでないのは電圧を0.1Vステップで測定していたためプロットが少ないのと放熱が間に合わなかったことに起因しています。尚、Vbs(Vbd)が0.5V以上の領域ではバックゲート・ソース(ドレイン)間が導通して大電流が流れているためデバイスはアチアチからめちゃんこアチアチになりました。このような測定する際は電圧をパルス入力にすることが望ましいです。

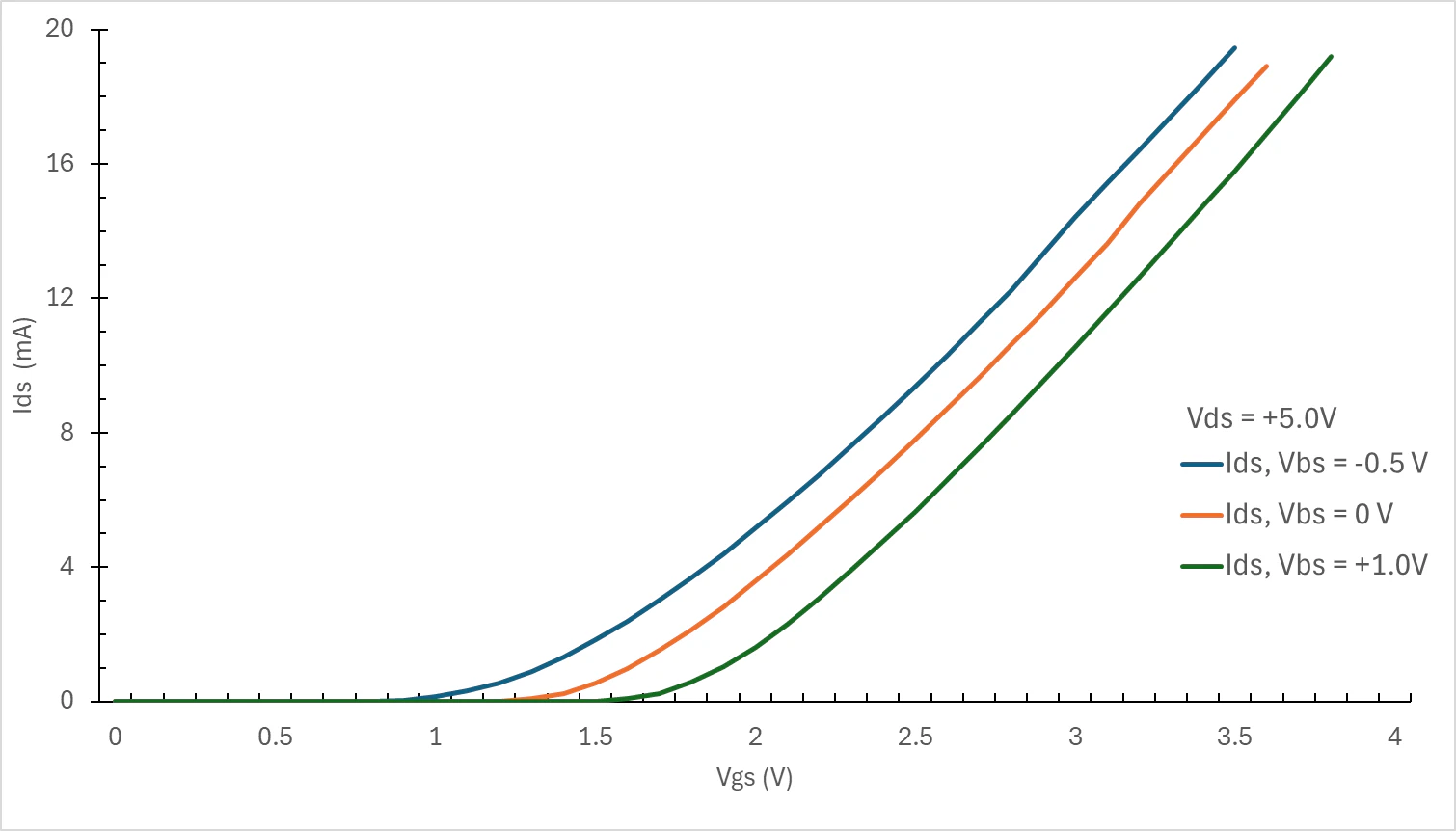

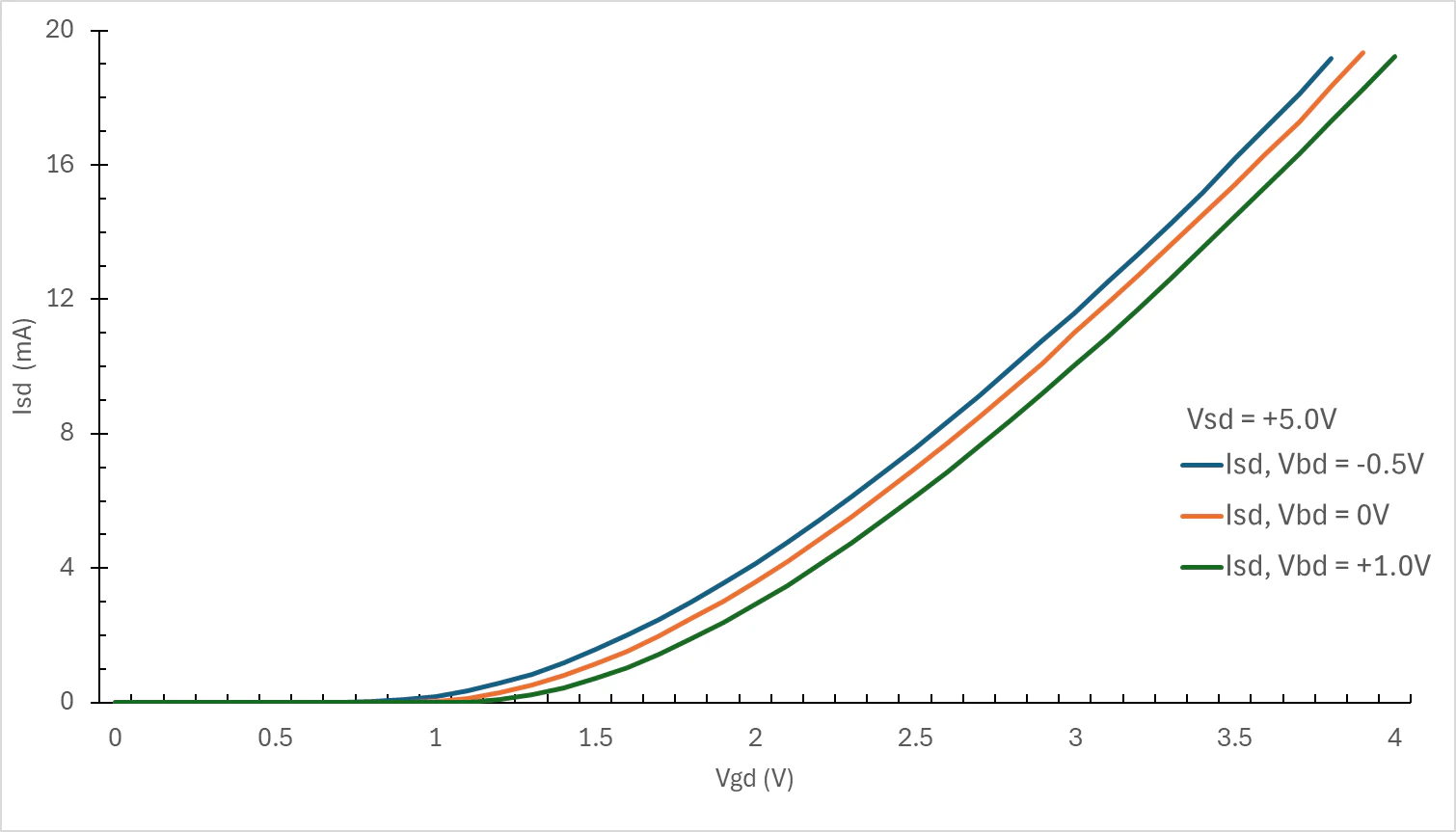

Nch LDMOS: Vgs-Ids, Vgd-Isdカーブ

バックゲートの動作を理解するだけならVbs-Idsカーブがあれば充分ではありますが、せっかくなので測定してみました。

グラフからだと非常に読み取りにくいのですが、バックゲートのバイアス電圧は負の方向に増加するにつれてわずかにトランスコンダクタンスgmを減少させています。ただこれはプロットの少なさと放熱の弱さに起因している可能性があるので考察は保留ということで…。

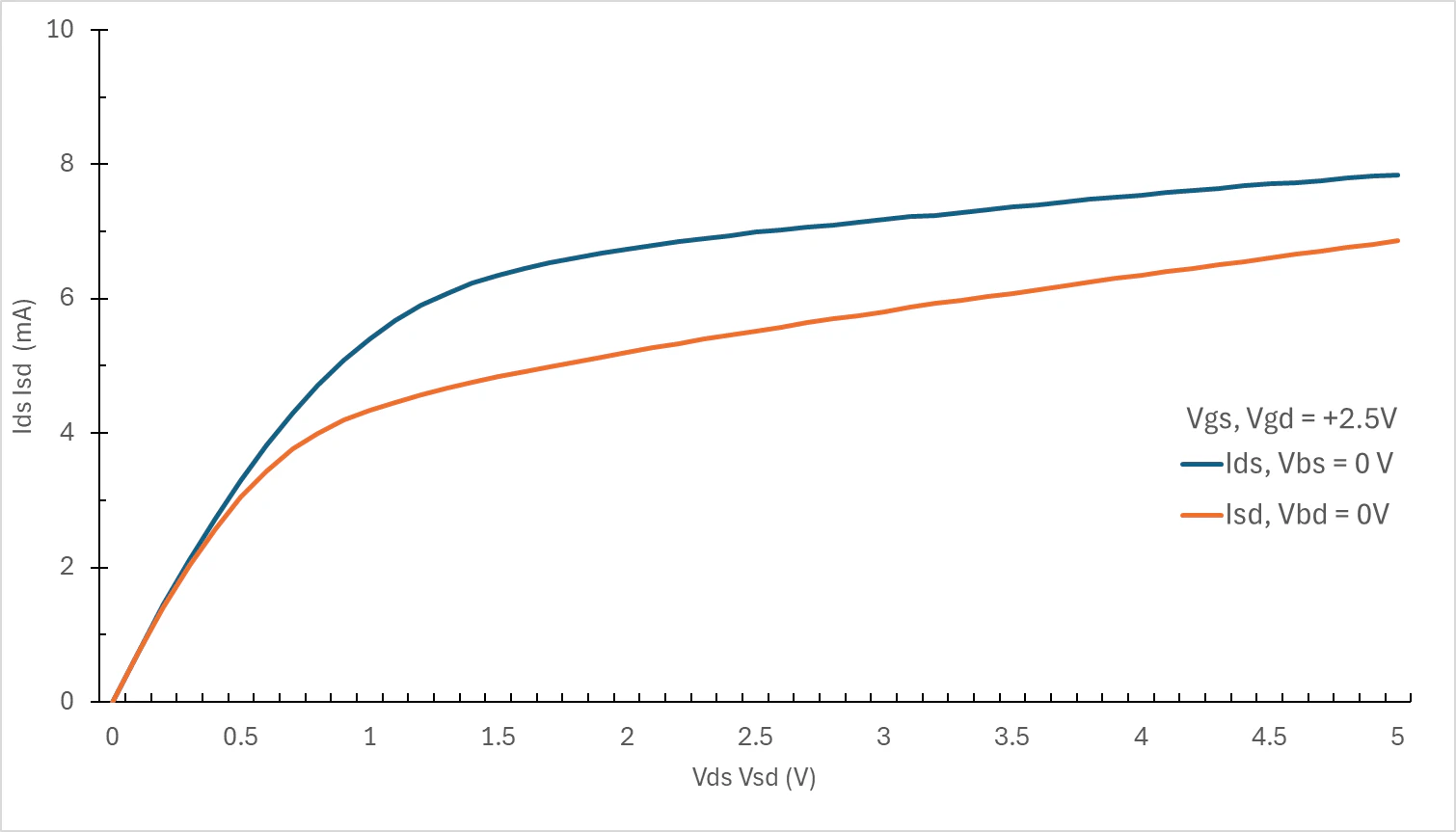

Nch LDMOS: Vds-Ids, Vsd-Isdカーブ

こちらも一応計測しました。

どうやらチャネル長変調の影響を大きく受けるタイプのデバイスのようです。

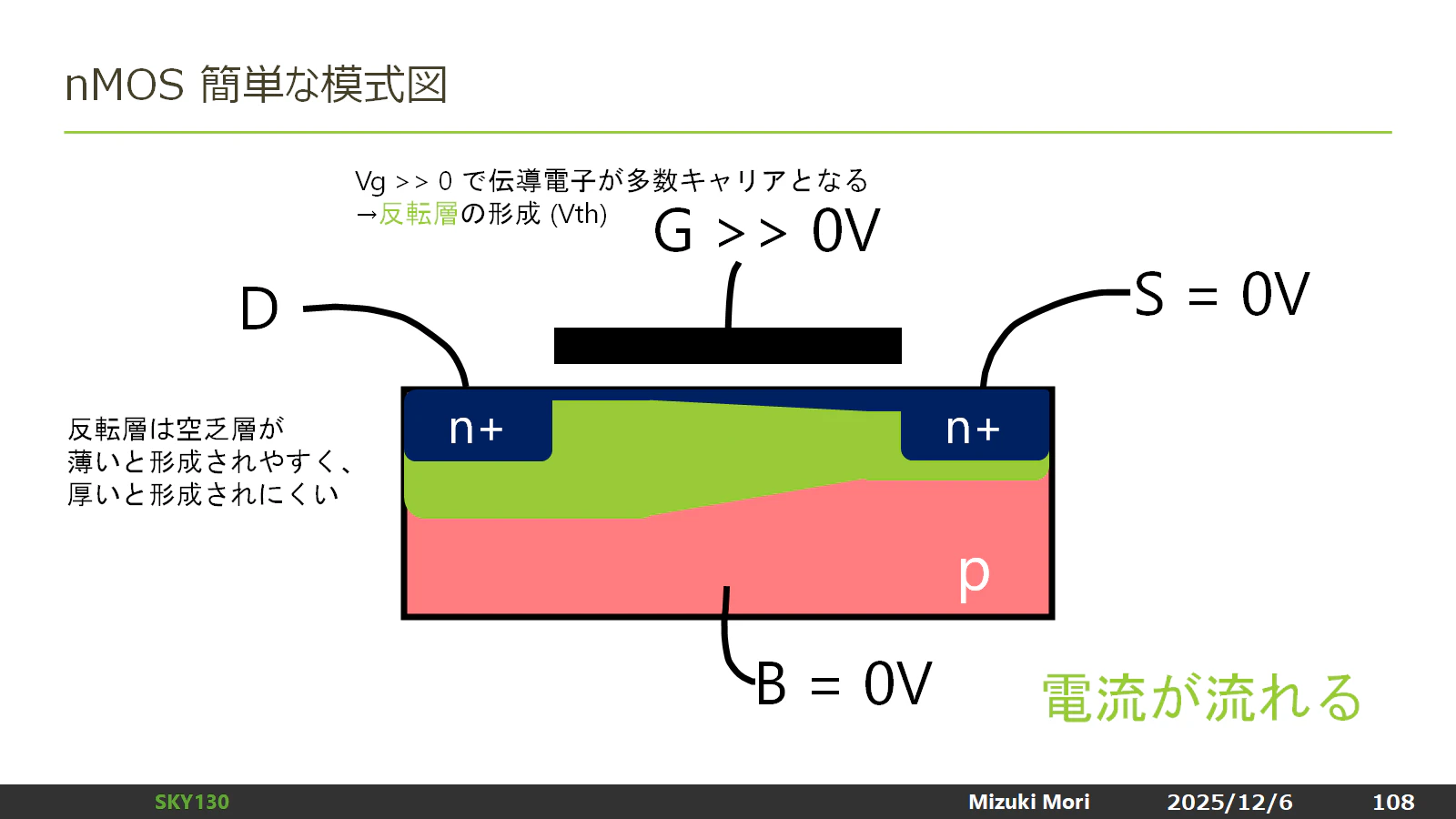

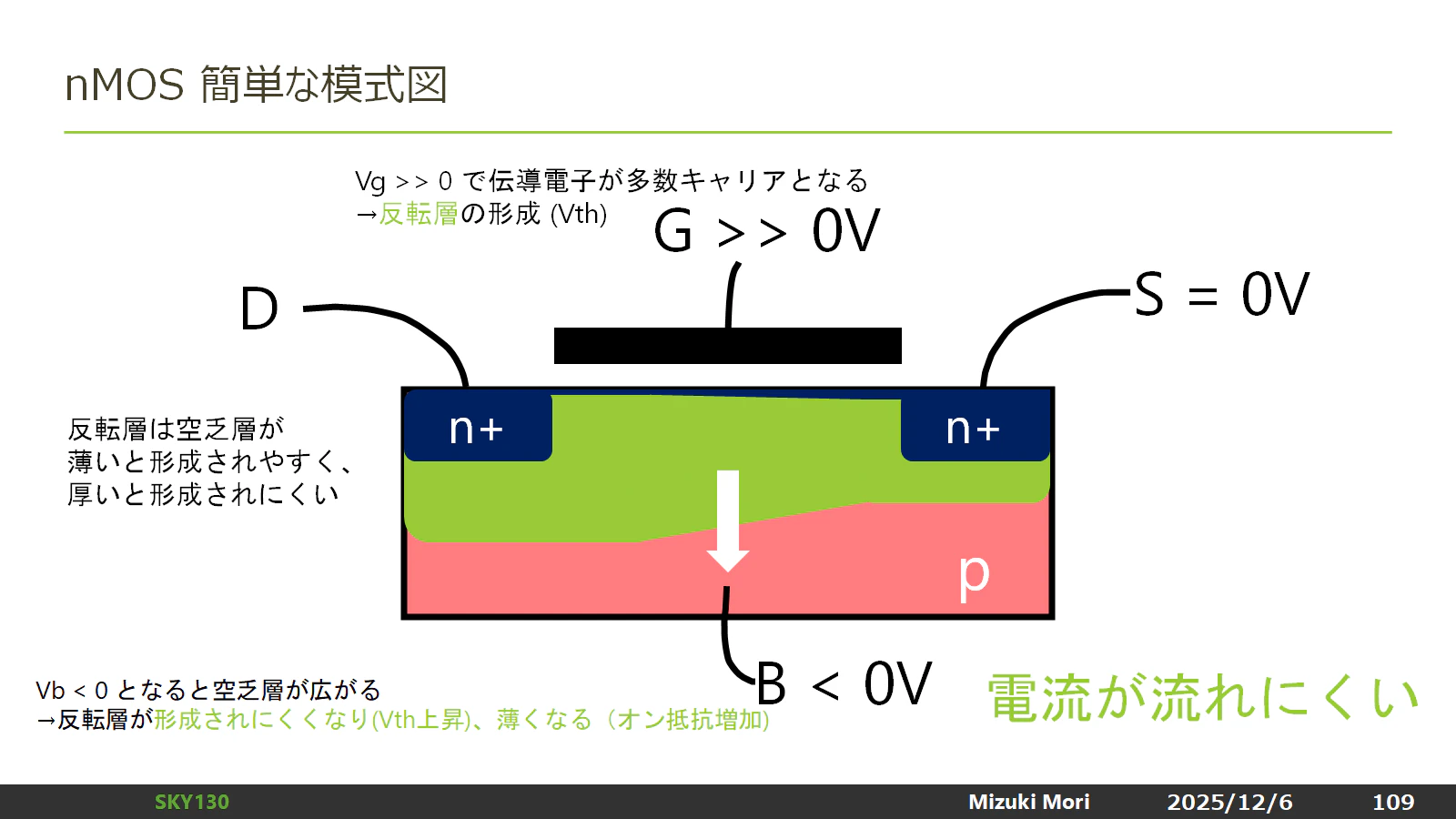

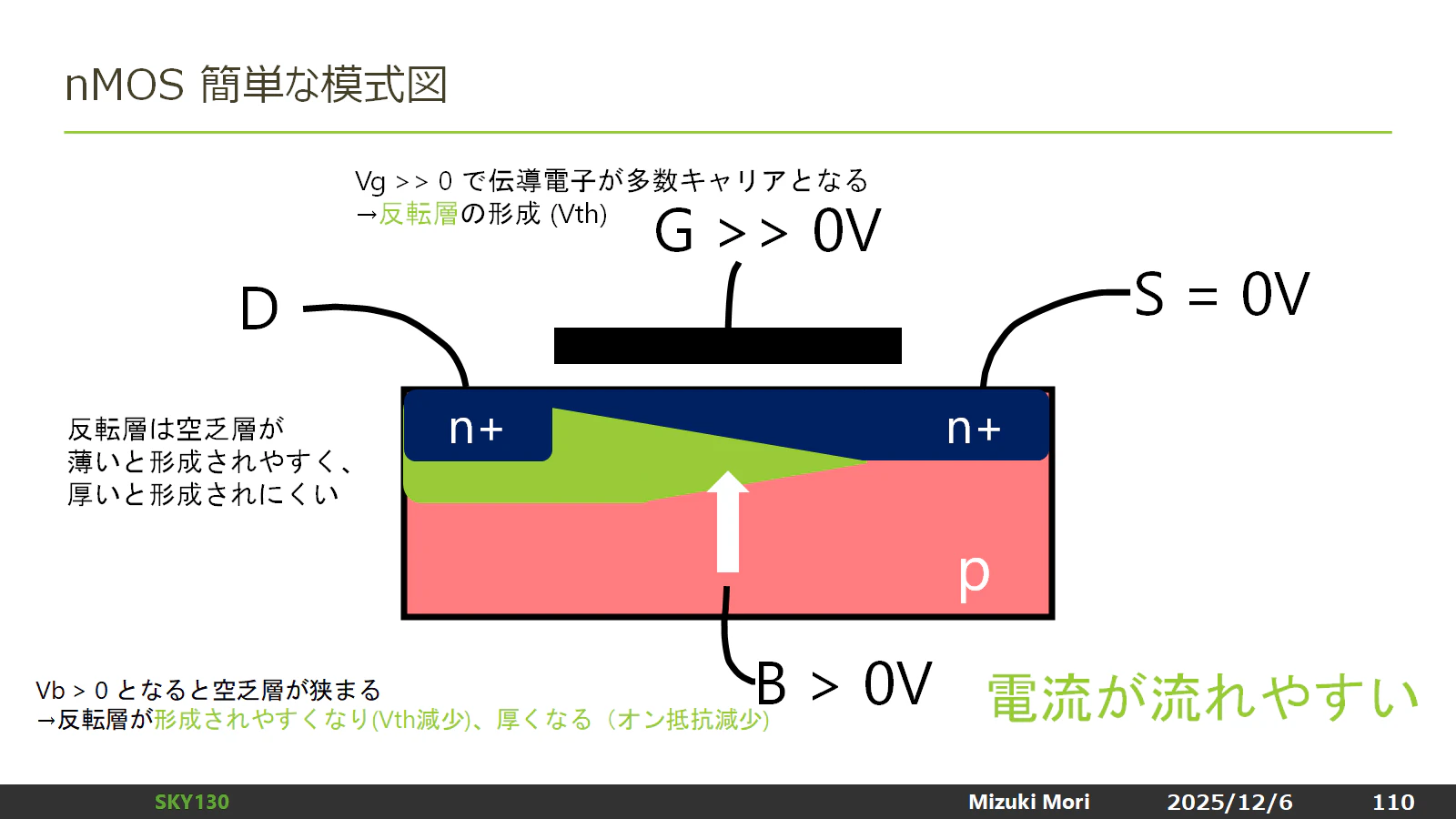

結果の見方と基板バイアス効果

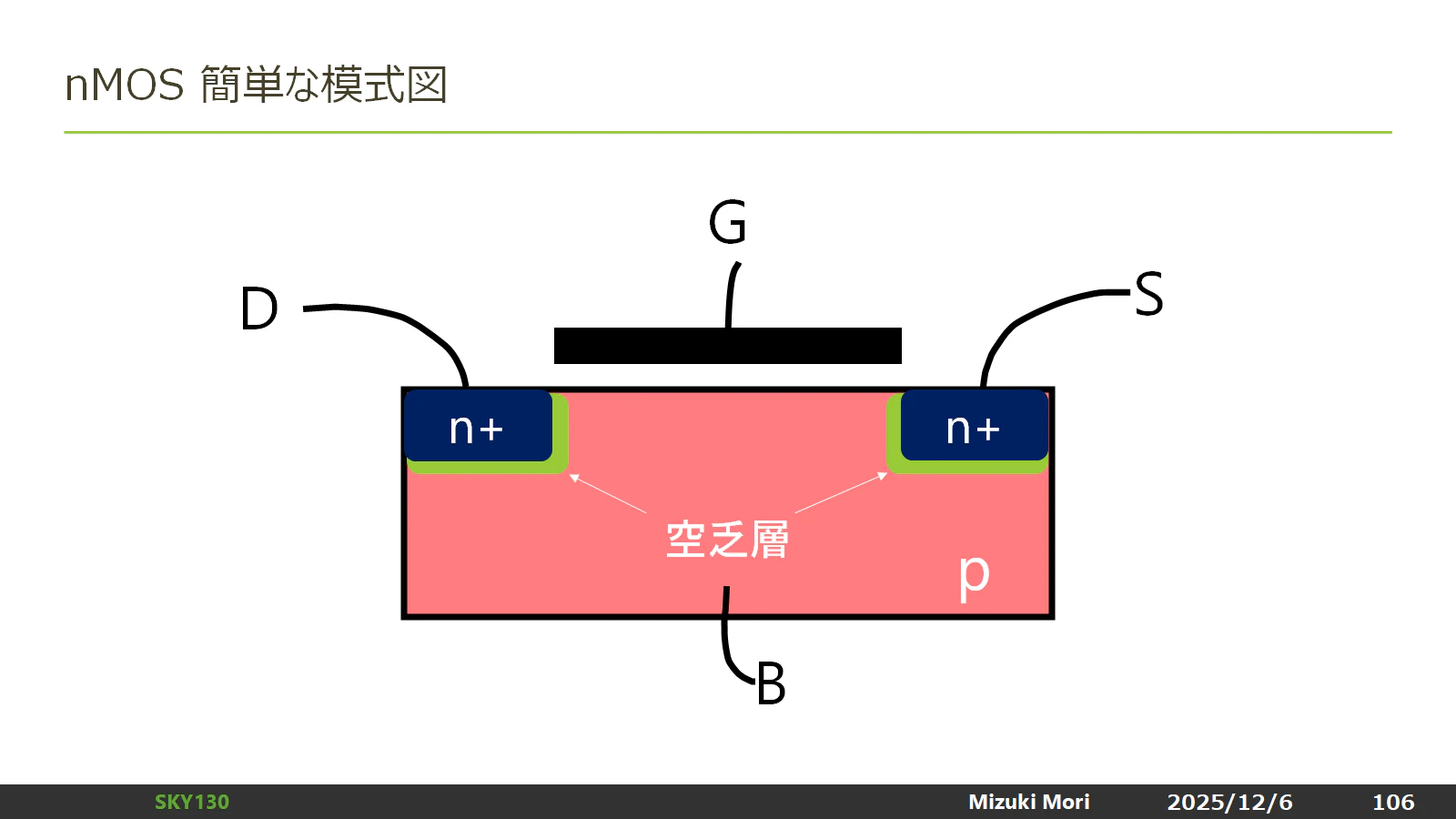

バックゲートの電位を変動させると基板バイアス効果によりIdsが変動します。今回測定したLDMOSではない、LSI設計者にとっては見慣れた(?)左右対称のNch MOSFETの構造図ではありますが、過去の勉強ノートに作図した資料があるのでそれを使ってVbsを変動させた時のトランジスタの挙動について説明します。

青はn+インプラ、黄緑は空乏層、薄赤はp基板です。ICプロセスにおける左右対称のMOSFETではドレインとソースの構造上の違いがなく、拡散領域(n+)に印加される電圧の大小によってドレインとソースが決まるため常にVd>Vsの関係が成り立ちます。回路の動作によってはドレインとソースが入れ替わる事もあります。

LDMOSでは構造の違いからドレインとソースが定義されるため、Vd<Vsがあり得ます。この章ではICプロセスにおける左右対称のMOSFETについて言及しているので一旦LDMOSについては忘れてください。

Vd>Vsなのでバックゲート・ドレイン間の電位差Vbd>バックゲート・ソース間の電位差Vbsとなり、ドレイン側の空乏層がソース側の空乏層よりも厚く形成されていることが推測できます。

ドレインとソースの空乏層の厚みの差についてピンとこない方はPN接合(ダイオード)において逆電圧を印加した時の空乏層のふるまいを調べてみてください。

ここでは説明を簡略化するため、ソースはGND(0V)が印加されているものとして説明を進めます。

バックゲートに負電圧を印加した場合

バックゲートに負電圧を印加して、バックゲート・ドレイン間、バックゲート・ソース間の電位差を広げてみます。pn接合間の逆電圧バイアスが強くなると空乏層はより広がり、反転層は形成されにくくなる、つまり反転層は薄くなります。反転層が薄くなるということはIdsの通り道が狭くなることを意味してますから、Idsは減少します。このことはVbs-IdsカーブにおいてVbsに負電位を与えた時の挙動と一致します。

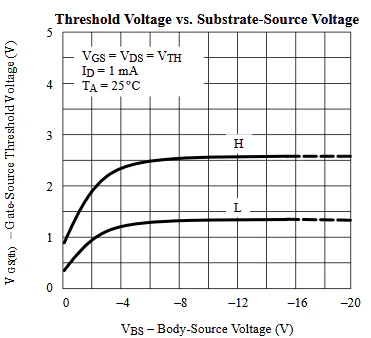

負電圧を印加すると空乏層は広がると書きましたが、負電圧を印加すればするだけ空乏層が厚くなるかというとそうでもなく、成長限界があります。負電圧バイアスが大きくなるにつれて次第に成長速度はゆるやかになっていくため、Idsの減少もゆるくなっていきます。今回測定できた電圧レンジでは飽和が見られなかったので、データシートに記載のVbs-Vgs(th)グラフを引用してお茶を濁しておきます。

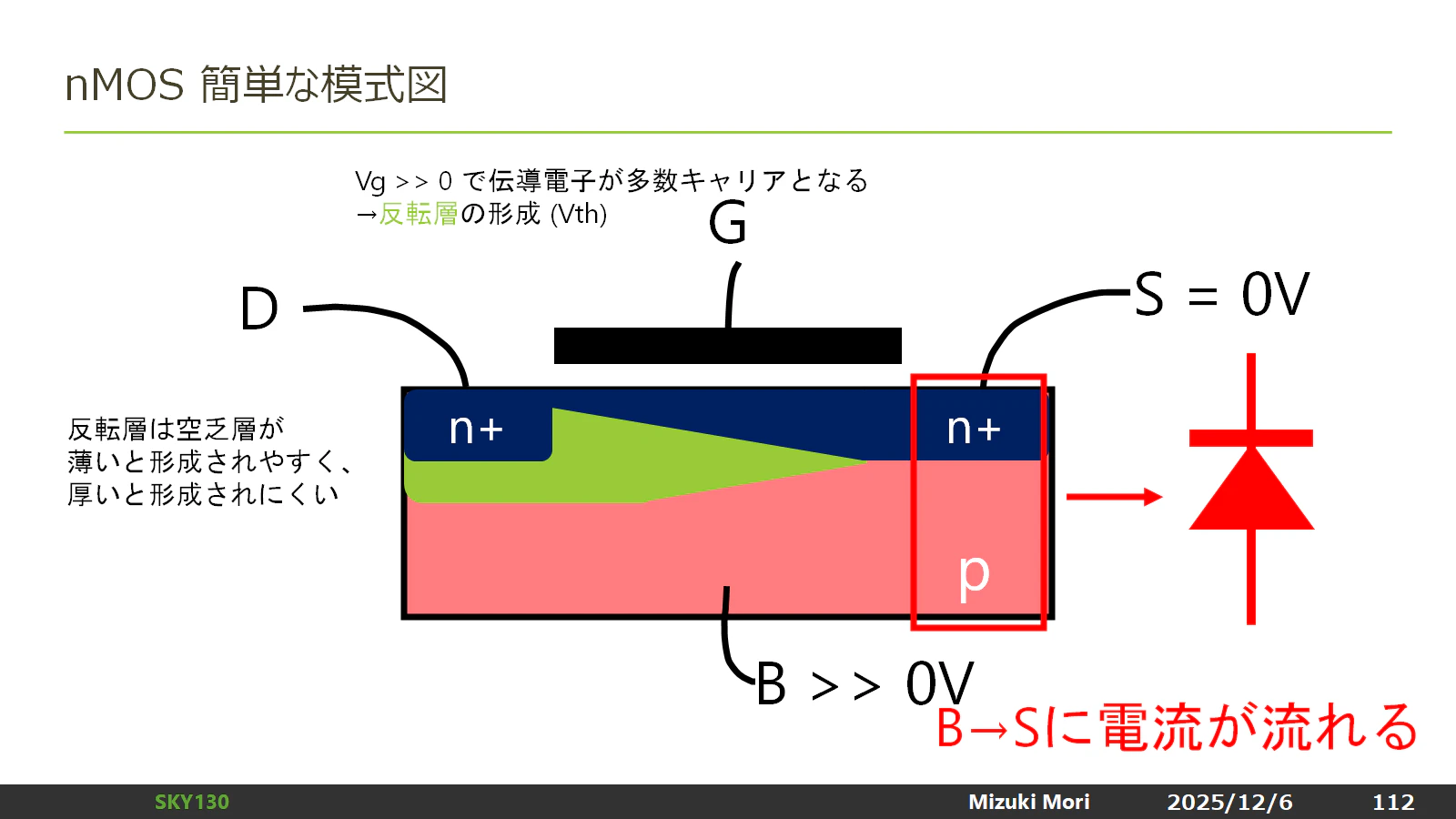

バックゲートに順電圧を印加した場合

ではバックゲートに順電圧を印加した場合はどうでしょうか。バックゲート・ドレイン間の逆電圧バイアスは小さくなり、バックゲート・ソース間は極性が変わって順電圧バイアスとなります。pn接合間には順電圧バイアスが印加されるため整定状態で形成されている空乏層は狭くなり、反転層は形成されやすくなる、つまり反転層は厚くなります。反転層が厚くなるということはIdsの通り道が広くなることを意味してますから、Idsは増加します。このことはVbs-IdsカーブにおいてVbsに順電位を与えた時の挙動と一致します。

バックゲート・ソース間の順電圧バイアスを増加させるとどこかのタイミングで空乏層の厚さはほぼ無視できるほど薄い厚さになります。空乏層はマイナスの厚さにならないためこれ以上バックゲート・ソース間の順電圧バイアスを広げてもソース近傍の空乏層にはほとんど影響がなく、Vbsの増分ΔVbsに対するIdsの増分ΔIdsは小さくなります。ただしバックゲート・チャネル間の空乏層とバックゲート・ドレイン間の空乏層には引き続き寄与するためIdsはゆるやかに増加します。

ただしバックゲート・ソース間はpn接合であるため寄生ダイオードが形成されています。「空乏層の厚さはほぼ無視できるほど薄い厚さ」になったというのは寄生ダイオードにおける閾値電圧Vbs(th)を超えた事を意味しており、寄生ダイオードのVbs(th)を超える電位差を与えるとバックゲートからソースの方向に大電流が流れます。このような状況が起きるとふつうデバイスは熱で壊れるため、バックゲート・ソース間に順電圧バイアスを加える事はしません。

まとめ

バックゲート・ソース間に逆方向電位を与えるとIdsは減少する

バックゲート・ソース間に順方向電位を与えるとIdsは増加するが、寄生ダイオードのVthを超えるとデバイスは壊れる。危ないのでしてはいけない。

冒頭で「バックゲートのバイアス電圧によってIdsが変わる」以上の理解が難しいと書きましたが、「バックゲートのバイアス電圧によってIdsが変わる」ということを知っていればそれで充分というお話でした。

補遺: DMOSとは?

今回入手した素子はNch LDMOS(Lateral Double-diffused MOS)と呼ばれるタイプのMOSFETです。LSIプロセスにおけるMOSFETも横型(Lateral)であるという点で特徴が一致しており、またプロセスによってはLDMOSオプションがあります。バイポーラトランジスタ、CMOS、(L)DMOSが一枚のウエハ上で製造できるプロセスはそれぞれ頭文字をとってBCDなんて呼んだりします。プロセスにおけるBCDは10進法ではないのでご注意!

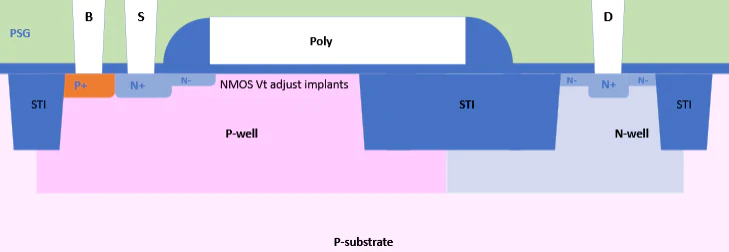

オープンソースPDKでおなじみのSkywater 130nmにもLDMOSオプションがあり、20V耐圧のNch LDMOSがあります。ドキュメントに構造図が掲載されているので、これを使って一般的なCMOSとの違いを少し見てみたいと思います。

本来、ドレインのN+インプラ領域の下はバックゲートであるP-well/P-substrateのはずですが、LDMOSではN-wellです。これはN+とP-well/P-substrateとの界面にインプラ濃度の低い「N-」の領域があるという認識をしてもらえると良いかと思います。

またNwellとPwellの界面にはSTIが彫られていますが、これはドレイン側のゲート酸化膜厚がめっっっっちゃ分厚くなっているという認識をしてもらえると良いかと思います。

要約すると、ドレインとソースが非対称です。

この構造はドレイン側の耐圧を上げるために施されています。MOSFETの耐圧はバックゲートを理解する上で大変重要な要素なのでちょっと深堀してみます。

CMOSにおける「耐圧」の考え方

ここではDMOSではない、一般的な左右対称のNch MOSFETを使ってCMOSの耐圧とは具体的に何かを考えます。

以下、勉強ノートより引用

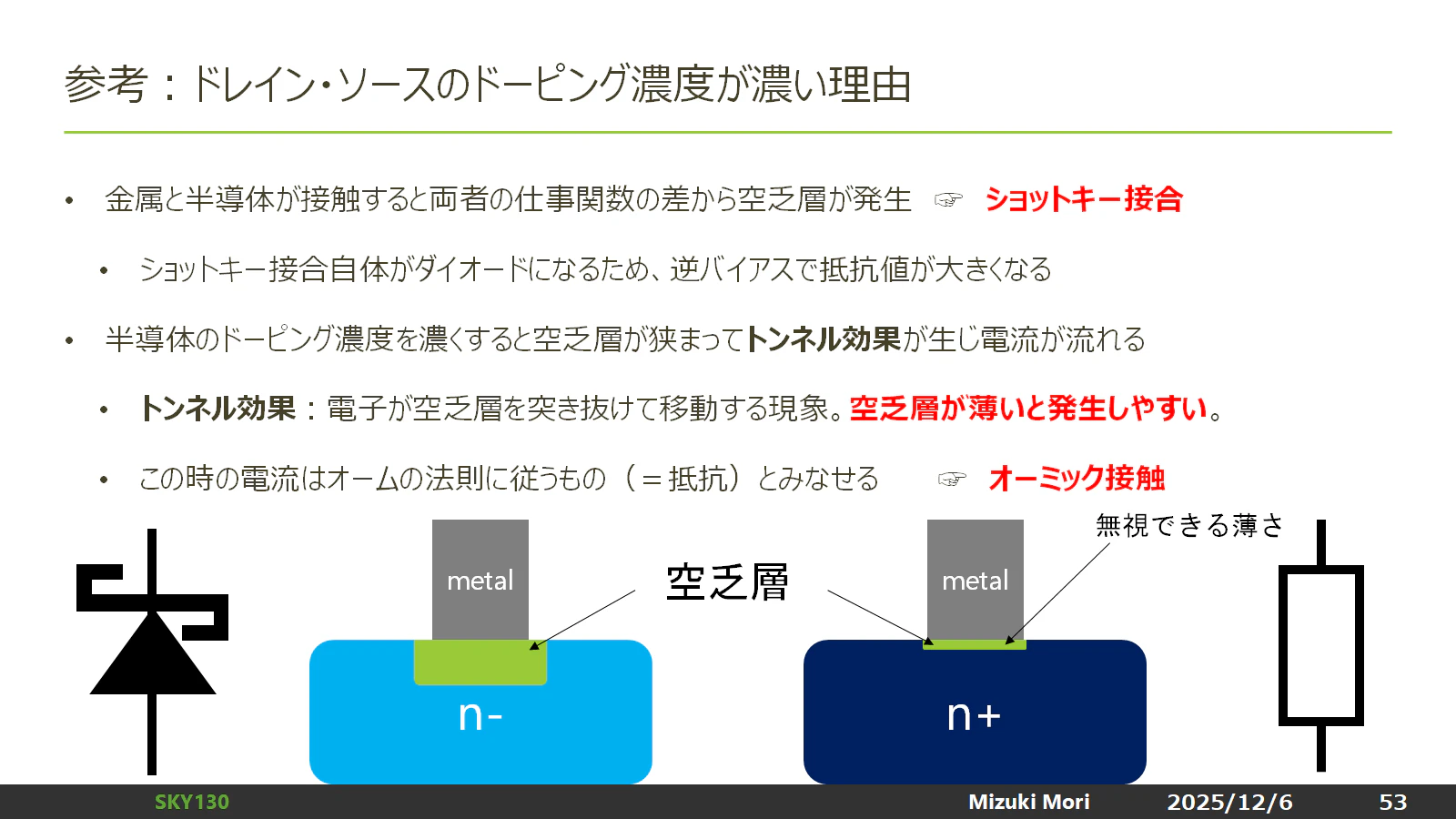

p.106はNch MOSFETの構造。バックゲート・ドレイン間とバックゲート・ソース間はpn接合になっており界面は空乏層を形成する。ドレイン・ソース領域のインプラ濃度が濃い理由はショットキー接合を回避するため。p.53を参照。

MOSFETの耐圧と聞いてまず思い浮かべるのはゲート酸化膜のブレークダウン(破壊)電圧でしょうか。これはゲートと基板の極板間電圧を指標としており、ゲート・ドレイン間電圧Vgd、ゲート・ソース間電圧Vgs、そしてゲート・バックゲート間電圧Vgbそれぞれで絶対定格が定められています。定格を大きく超えるとゲート酸化膜が破壊して使い物にならなくなります。少し超えたところで直ちに破壊されることはありませんが、ゲート酸化膜の劣化速度は早まります。

MOSFETの耐圧としてはもう一つ、ドレイン・ソース間の耐圧Vdsmaxがあります。ここで注目したいのは バックゲート・ドレイン間とバックゲート・ソース間がpn接合である という点。通常pn接合はp→nの方向に電流が流れ、n→pの方向には電流が流れないという整流作用があると習いますが、n→pに高電圧を与えるとどうでしょうか。

n→pに高電位差が生じると電圧によって加速される電子の速度は非常に速くなります。この電子がSi結晶格子中の原子に衝突すると原子は電離し電子と正孔になります。この電離した電子は他の結晶格子中の原子に衝突し、また電離を引き起こすという連鎖反応が発生します。これをアバランシェ降伏と呼び、逆電圧降伏が起きるとn→pの方向であっても電流が急激に流れ出します。非常に大きな電流が流れるので対策をしていなければ熱によってデバイスは壊れます。

ここではアバランシェ降伏について言及しましたが、逆電圧降伏にはもう一つ、ツェナー降伏によるものもあることを注記しておきます。現実ではそれぞれの降伏電圧のうち低い方が作用します。DMOSではドレイン・バックゲート間におけるpn接合界面の不純物濃度が低いためアバランシェ降伏による逆電圧降伏が妥当と筆者は考えました。

従って、ドレイン・ソース間の耐圧を超えるとショートモードになります。ただし今回は4端子CMOSなので、ドレイン・バックゲート間の耐圧Vdbmax、もしくはソース・バックゲート間の耐圧Vsbmaxと表現するのがより正しいです。バックゲート→ドレイン(とバックゲート→ソース)はp→nで順方向なので、一度逆電圧降伏が起きるとソースの電圧がどうであれドレイン・ソース間は導通しますし、なによりドレイン・バックゲート間が導通した時点で電源間ショートとなります。

バックゲート電位>ソース電位だとドレイン・ソース間は導通しないかもしれませんが、そもそもバックゲート→ソースがp→nなので寄生ダイオードの順方向電圧を超えるとバックゲート→ソース間に大きな電流が流れる事になります。ゆえにこのシチュエーションを考える必要はまずありません。

この章のポイント

- ゲート電圧Vgd,Vgs,Vdbはゲート酸化膜のブレークダウンに寄与する

- ドレイン・バックゲート間電圧Vdbはドレイン・ソース間の耐圧に寄与する

DMOSにおける耐圧

DMOSにおける耐圧を見てみます。話を単純にするためバックゲートはソースとショートしていてかつソースはGNDにつながっているとして、オフ状態(つまりVgs=0V -> Vg=GND)を考えます。この条件でドレイン・ソース間に高電圧を加えるとどうでしょうか。

ゲート酸化膜のブレークダウンという視点では、Vgs,Vgbの電位差は0Vで問題なさそうです。怖いのはVgdでVdsに高電圧がかかっているということはゲート・ドレイン間の電位差Vgdもまた高い事を意味します。DMOSではゲート酸化膜ブレークダウンを防ぐために、ドレイン近傍の酸化膜を厚くしたり、酸化膜と基板間を更に別の素材で絶縁したりします。

また当然ですが、ドレイン・バックゲート間の逆電圧降伏もケアしなければなりません。逆電圧降伏を起こりにくくするにはどうすればよいかというと、空乏層を厚くすればよいです。詳細は省きますが逆電圧降伏は空乏層における電界強度が閾値を超えると発生し、この電界強度は空乏層が薄いと高くなります。では空乏層を厚くするにはどうすればよいかというと、pn接合のドーピング濃度を薄くすれば空乏層は厚くなります。こちらも詳細は省きますがドーピング濃度が濃いと自由電子・自由正孔と結合する「対の存在」が近場にあるので空乏層は広がらずに済み、逆にドーピング濃度が薄いと自由電子・自由正孔と結合する「対の存在」を遠くから持ってこなければならないため空乏層が広がってしまいます。以上より、LDMOSではドレイン・バックゲート間の逆電圧降伏をケアするため、ドレイン・バックゲート間はドリフト領域とよばれるドーピング濃度の薄い領域が間に挟まります。冒頭に挙げたSkywater 130nmのNch LDMOS (nfet_20v0)におけるドリフト領域がまさにN-wellです。

この章のポイント

- ゲート・ドレイン間の電位差起因によるゲート酸化膜ブレークダウンを防ぐため、ドレイン近傍の酸化膜は厚くなっている

- ドレイン・バックゲート間の電位差起因による逆電圧降伏を防ぐため、ドレイン・バックゲート界面のドーピング濃度は薄くなっている(ドリフト領域=Nwell)

ドレインとソースを逆にした場合は?

ここまで読み進めてきた方ならお察しかと思いますが、通常、LDMOSはソース→ドレイン方向の耐圧、すなわちソース・バックゲート間の耐圧とゲート・ソース間の耐圧に関しては低オン抵抗を確保するため耐圧について何ら対策はされていません。LDMOSを用いたLSI設計においてはソース・バックゲート間の電位差を常にケアしなければならず、3電源系アプリケーションにおいてはGNDレベルをNMOSのソースに繋げるとソース・バックゲート間の耐圧違反になるなど扱いに大変苦労した経験があります。ここ、めちゃくちゃ大事なポイントなので強調しておきます

LDMOSは通常、ドレイン側のみ高電圧対策がされており、ソース側は対策がされていない(低耐圧MOSと同じスペック)

今回LDMOSを入手した経緯は「DMOSのドレインとソースを逆に接続すると特性は変わるのか」というのが最たる動機です。大半のディスクリート素子においてバックゲートはソースに繋がっているのでソース→ドレインの方向はつまりバックゲート→ドレインでp→nになるのでゲート電圧に関係なく導通となります。しかし今回手に入れたバックゲート独立型の4端子MOSFETやLSI設計においてLDMOSはどのような電気特性となるのか? バックゲートとドレインをつなげて逆側から電流を流したらどうなるのか? という疑問を解決するためIdsカーブを測定したのでした。

おわり。