ネットで探すと以下のような参考になるページがあります。

受信のロジックは以下のような方法が考えられます。

- データはBMCで1ビットを2パルスで送ってくる

- 1サンプルを32ビットのサブフレームでLRで64ビットの1フレームにしてる

- データは2パルス以上のH/L信号はなくフレームの先頭だけがHかLの長い3パルスの信号なので、そこを見つける

- 1秒間の先頭の数を数えるとサンプリング周波数が確認できる

- 先頭から32ビットのBMCのデータをデコードする

- 32ビットのサブフレームにはV,U,Cのそれぞれ1ビットの属性情報があり192フレームの1ブロックで一塊の24バイト(32bit x 6)のデータになる

- 属性情報のCデータにもサンプリング周波数が入っている

FPGAやCPLDで論理実装するときはなんか良い方法があるのかもしれません。売り物のIPもあるようです。

githubを探したらverilogのコードがありました。

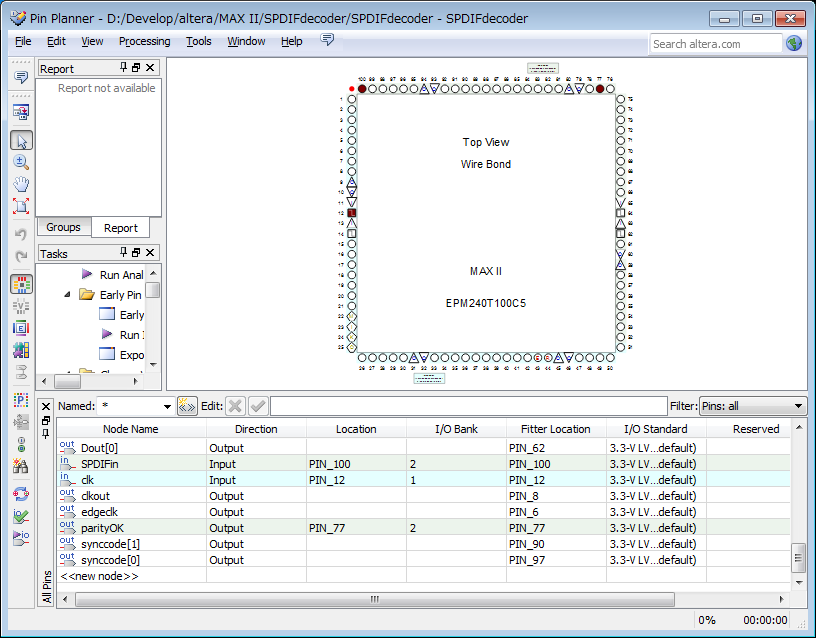

ピンが足りなかったので減らして、MAX IIに焼いて試してみました。

再生するとparityOKが1になるので、ちゃんと動いてそうです。

エラーは以下のようなケースが考えられる

- パリティが不正

- 1フレームが64bitじゃない

- ヘッダーが見つからない

- などなど