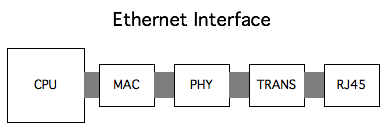

100BaseTなどのEhternetデバイスはMACとPHYが主要な部品となります。

この構成は2000年くらいの100BaseTからの仕様で、10BaseTのころはMACとPHYが一体化した状態でした。

LSIのL80225というチップで2000年くらいのもの。PLCC 44Pinで結構大きいです。

PCIインターフェースのEthercatdでMACとPHYが別の部品なっていたのは、初期の一時期でMACとPHYが同一チップ内に入るようになりました。

MACからPHYへの接続はMIIと呼ばれデーターの送受信用の接続とコントロール用の接続があります。FreeBSDのethernetドライバ当初通信用とコントロール用のコードをすべてドライバに入れていましたが、NetBSDから導入したコントロール用の接続をmiibusとして扱いPHYを任意に選択できるようにしました。

1000M(1G)のものはGMIIと呼ばれ、信号線を減らしたものがRGMIIになります。SGMIIという仕様もあります。

miibusというのですが、実際はコントロール用のmdio/mdcの制御により実現されていmdbusといったほうが良かったのかもしれません。

mdioでは32個のアドレスに32個のレジスタがアクセスできます。レジスタは16ビットになります。アドレスは固定だったり、PINコンフィグレーションで設定されていたりします。

MACは接続が100Baseでも10Baseでも同じように処理していて、PHYが調整をおこないます。MACからmdioでPHYにつながれている接続があるかないかや、種類を問い合わせする事ができます。

この仕組みはFreeBSD 3.3から採用されたため、これより古いドライバでメンテナンスされていないものは、miibusが実装されていないものもあります。もし実装したとしてももはや確認できる環境がなかったりするかもしれません。

PHY用のFreeBSDのコードはsys/dev/miiにあります。

PHYの認識については、MIIでレジスタを確認する事で可能です。MIIのRegister 2と3がIDになっていてIEEEで管理された値があり、この値でPHYの種別を識別する事ができます。こに一覧が上記のディレクトリにmiidevsというファイルであります。

カーネルオプションのmiibusは全てのphyコードを入れて自動認識するためのオプションで、miiと必要なphyのオプションでもビルドする事ができます。ar531x/mipsで試したところ後者のコンフィグレーションの方が4%くらいカーネルが小さくなりました。

swtichチップにもphyが入っていて、etherswitchフレームワークではこのphy(miibus)の仕組みを再利用しています。

ar531xのネットワークインターフェースareではPHYやswitchのサポートため以下のようなオプションがあります。

| オプション | 内容 |

|---|---|

| ARE_MII | PHYが接続されているケース |

| ARE_MDIO | スイッチが接続されていてサポートがあるかukswitchで利用可能なケース |

| 無し | スイッチが接続されているがサポートコードがなく、設定せずに使うケース |

i386/amd64などのPC系では、標準でより多くのデバイスをサポートしたいということで自動認識で対応したいという考えで開発されていますが、arm/mipsなどのEnbead環境でリソースが少ないケースではconfで最小限の構成にしたいとい場合もあります。

追記

areで以前はmiibusでビルドして問題なかったモジュールが、何故かクラッシュするようになりmii+rlphyでカーネルをビルドして試してみたところ問題なくなりました。謎です。。。

are1: <AR531x Ethernet interface> at mem 0x18200000-0x182fffff irq 2 on nexus0

miibus0: <MII bus> on are1

Trap cause = 2 (TLB miss (load or instr. fetch) - kernel mode)

[ thread pid 0 tid 100000 ]

Stopped at 0