PIC32MXでDAIを作ってみたのですが、このコードではPLLでマスタークロックを作っていたのですが、一般の製品の場合どうしているか確認してみました。

再生系のI2Sでは、マスタークロックを出力するか、外部からマスタークロックをもらって、3本の信号を出すかのどちらかになり、一般的には前者が多いです。

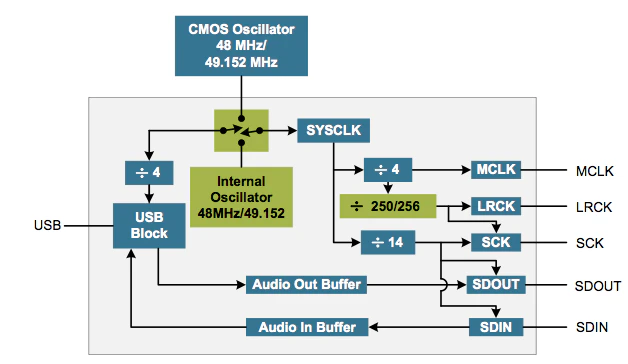

CP2114の場合

この製品は発振回路が内蔵されていますが、USBのクロックも必要なため外部発振回路をつけないかぎり48MHzでの使用する事になります。この場合48KHzで利用すると250fsでのマスタークロックになり、通常のDACだと、かなりはっきりノイズになってしまいます。

48KHzの256fsは12.288MHzとなります。データシートには内蔵クロックだけで使う場合には12MHzに対応したDACとありますが、すなわち250fsでも使えるDACということになります。

このチップで最高のクオリティーを出すためには内部発振を48MHzでUSB用にして、外部発振を49.152MHzにしてI2S用にする必要があります。この場合Audio Configuration Stringという内部設定をチップのOTP EPROMというワンタイムROMに設定を書き込んで、それを使用する必要があります。ワンタイムROMには複数コンフィグレーションを保存できるので一回しか書けないというわけではないようです。

このチップは48KHz固定で、外部クロックをつけないと250fsとなる結構思い切った設計な気がします。

49.152をつけた場合、分周でオーディオ用のクロックが作れ、PLLで作るより安定度が良く、音にも影響が出るかもしれません。

256fs固定のようです。

コストを考えてかPLLを入れないというポリシーのようです。Silicon Labsはちょっと変わっています。

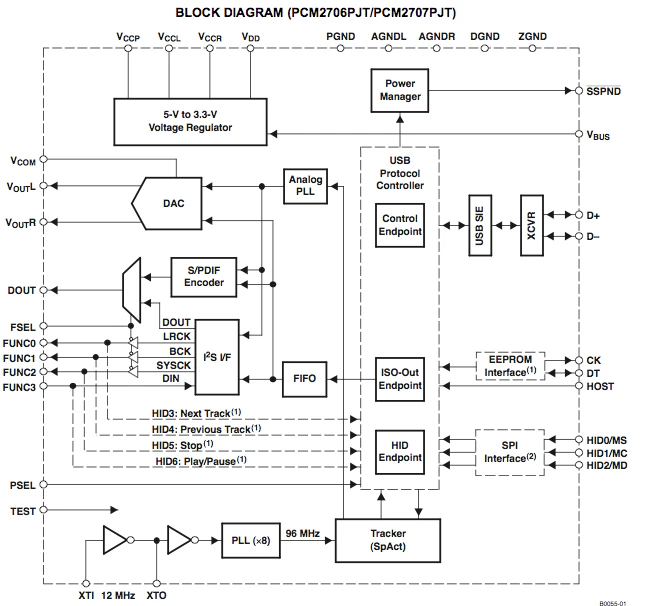

PCM2706の場合

このチップはUSB用の12MHzの発振回路から生成された96MHzを内部のAnalog PLLでI2S用のマスタークロックを作成しています。このチップのマスタークロックは256fs固定のようです。

PIC32MXでの方法と似ています。

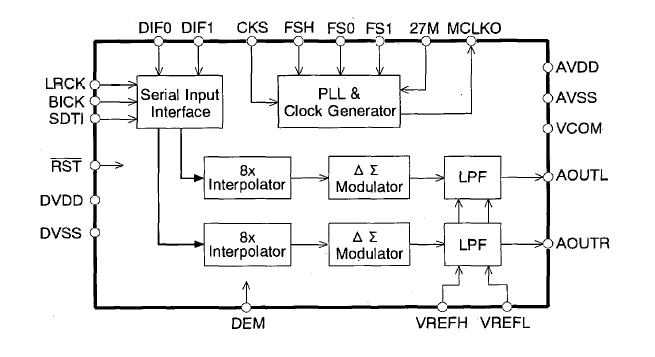

AK4323の場合

1998年くらいのCSチューナにAK4323というDACが入っていました。このチップにはPLLが入っていて27MHzのクロックからマスタークロックを作れるようです。MPEG系のチップは27MHzを使うことが多く、それを直接入れられるようです。

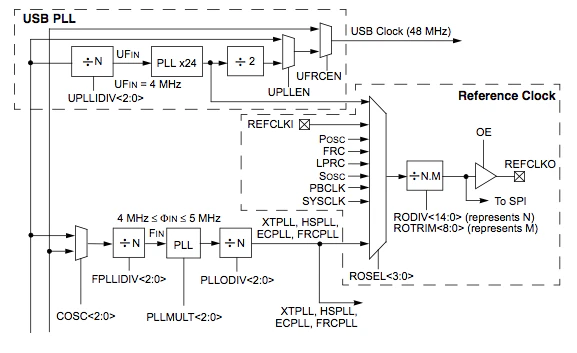

PIC32MX2xxの場合

これはAN1422にある通りUSB用の96MHzのクロックからRODIV/ROTRIMで適当なREFCLKOを作ってマスタークロックにしています。

ビットクロックはマスタークロックとSPIxBRGで設定されます。

片チャン32Bitの場合64fsで48KHzx64=3072KHzになります。これで256fsの場合は3072*256/64=12288KHzです。

誤差はあるようですが、256fs以外にも設定できます。

32Kと48Kの256fsと512fsはPLLで誤差なく作れるみたいです。

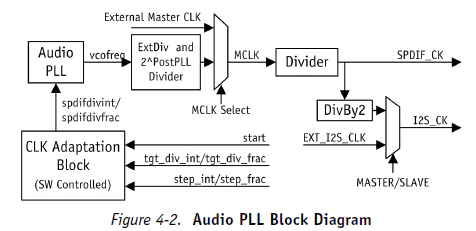

AR9341の場合

ルーターなどで使われているAtherosのAR9341でもI2SとSPDIFがサポートされています。クロックは以下のようです。

図ではSPDIFのクロックの半分をI2Sのクロックとしてますが、逆のような気がします。48Kの256fsのMCLKは12.2880MHzで、SPDIFのクロックは6.1440MHzになります。

なぜか24K初期のAR7242には似た図があるのですが、AR9341の一つ前の世代のAR9331のデーターシートには図がなくPLLの設定項目もありません。AtherosのSOCはmips 24KになったAR71xx以降からI2Sのサポートがあり、AR933xでPLLをいじったようなのですが、どうも失敗したようでAR934xではそれ以前の仕様に戻して拡張したようです。拡張した部分はDPLLと呼ばれているようです。

このSOCは25Mか40Mの外部発信器が使えます。Qualcommのオープンソースを見るとそれぞれの、PLLの設定が構造体にあります。おそらく32k,48k,98Kはのマスタークロックは12.288M固定で384fs,256fs,128fsになるのではないかと思われます。PLLの設定値を変えれば24.576MHzなども作れるような気がするのですが、データーシートを見てもよくわかりません。

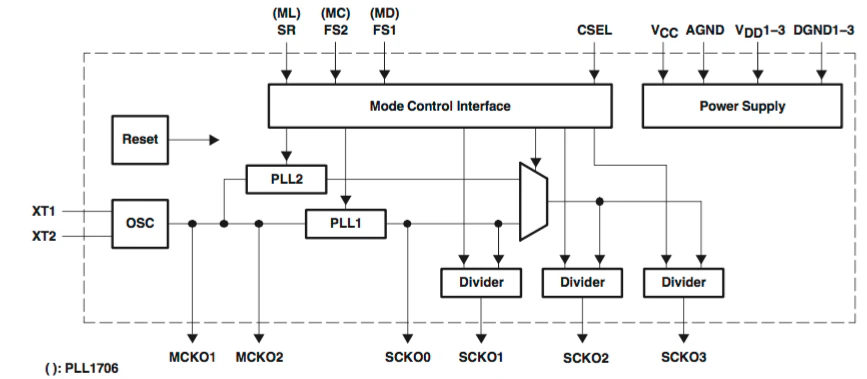

PLL1706

DAIではないのですが、マスタークロック生成用のチップがとあるジャンクに乗っているに気がつきました。このチップは27MHzの水晶発信からPLLでマスタークロックを作るようです。このチップはPLL1705というチップもあって、こちらはピン(SR,FS1,FS2)でサンプリング周波数などを設定できて、PLL1706はマイコンなどからのシリアルデータ(ML,MC,MD)で設定できます。

PLL1700という製品もあるようだ。

マイコンのI2Sサポートではスレーブモードをサポートしていることがあり、この場合は外部からのマスタークロックで出力が可能なようです。

一般的に水晶発信子とコンデンサーによる発信回路より、発信器の方が音がよいとされていて発振器も温度補償なTCXOが良いようです。

FN1241は384fs,512fsだけみたいなんで、CP2114などでは使えないようです。

PCM5102,TDA1543などのDACはマスタークロックがなくても使用できるようです。

ラズパイのI2Sにはマスタークロックが無いようですが、手元にないので確認していません。

ESP32のI2Sサポートもマスタークロックが無いようです。

いろいろ調べていたところ、マスタークロックが無い3線の仕様はAC 97由来なようです。

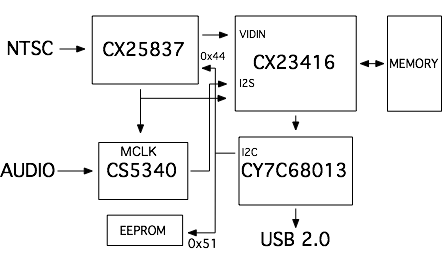

マスタークロックは本来、映像と音声の同期を行うことが主たる利用方法でした。mpegエンコーダーではマスタークロックはビデオのデコーダーが生成して、AudioのADCやMPEGエンコーダーに送っています。44.1KHzや48KHzというサンプリング周波数はビデオフレームレートの29.97からと整合が取れる数字だったはずです。

32Kの256倍のマスタークロックはどうにか設定できたのですが、他のサンプリングレートはうまく動きません。

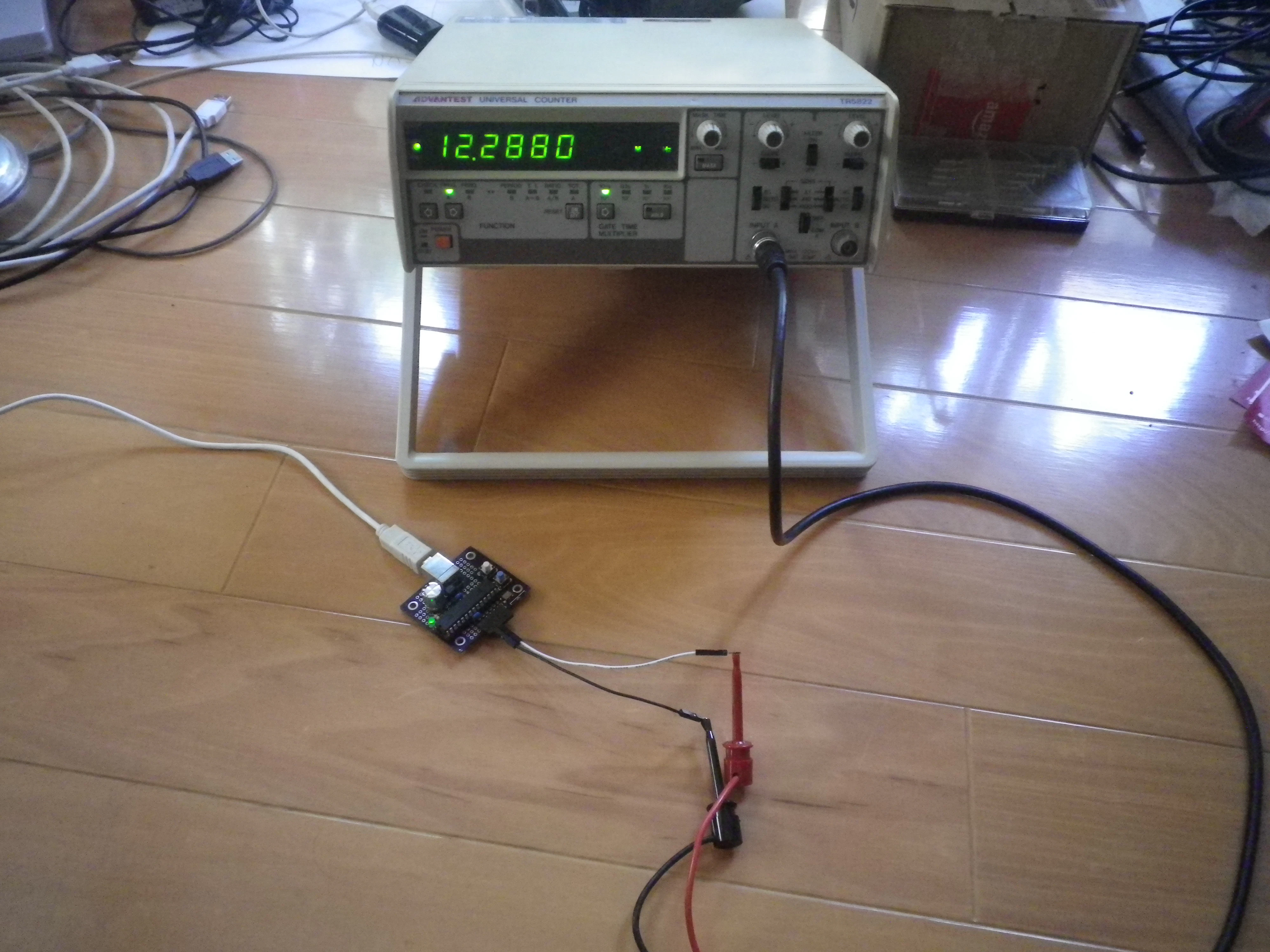

Macにつないで、周波数カウンターで調べてみました。

| チップ | SCLK |

|---|---|

| CP2114 | 11.99 |

| PCM2706 | 12.2882 |

| SN11122 | 12.2882 |

| PIC32MX | 12.2 |

| PLL1700 | 12.28656 |

| AR9341 | 12.287 |

変動がない桁を記入してみました。PLL1700は12.288にはなってませんが、安定度は一桁違います。

PIC32MXを水晶発信子ではなくFOXのTCXO 12Mの発信器にしたところ、むちゃ安定しました。手元のDAIでは一番安定しているような気がします。 測ってみたら残念な結果でした。

昔真空管のアンプはあったまるまで、ちゃんとした音が出ないって言われてましたが、デジタルオーディオの肝の発振回路も電源入れてからしばらくしないと安定しません。

MasterClockが無い場合、ICS512MLFのような逓倍チップで、BCLKを4倍にして256fsを作ることもできるとおもわれます。いつか試してみたいです。