結論を先に

Questa Intel Starterの制限5,000インスタンスは、自分で書いたモジュールの実インスタンス数の合計です。

モジュールのサイズ(行数)は関係ありません。

VHDL・Verilog共にfor-generateによるループでのインスタンスもカウント対象です。

初期インストールされるライブラリ(altera_mf, lpm等)はこのカウントに含まれません。

VHDLのパッケージはカウントに含まれません。

Questa Intel Starterについて

Quartus Lite 21.1から、添付されるHDLシミュレータがModelSimからQuesta 64bitに変更されました。

従来のModelSim Intel Starterはライセンス不要でしたが、Questa Intel Starterはライセンス設定が必要です。

設定方法はマクニカの下記のページを参照して下さい。

っていうか、IntelのWebにこの辺りの説明が全然無いけど、マクニカのページ無かったら誰も分からないヨ。

ModelSim Intel Starterとの違い

細かい機能の違いは製品情報を見てもらうとして、最大の違いは規模の制限。

どちらもVHDL,Verilog,SystemVerilog混合シミュレーションが可能。

ModelSimより速くなってるらしい、当然ながら有償版に比べて相当な速度制限が掛けられてますが、体感ではVivadoシミュレータより速いです。

| 項目 | ModelSim | Questa |

|---|---|---|

| 性能 | 1.0 | 1.25-2.5 |

| 規模の制限 | 10,000ステートメント | 5,000インスタンス |

| 制限にはソフトと同時にインストールされるプリコンパイル済みのライブラリ(altera_mf, lpm等)は含まれません。 | ||

| 大きな違いとして、制限の数え方が**ModelSimの「10,000ステートメント」からQuestaは「5000インスタンス」**に変わってます。 |

ModelSimのステートメント数

「ステートメント数」の単位は単純なソースの有効行数とは違うようですが、ソースが大きければステートメント数も多くなります。

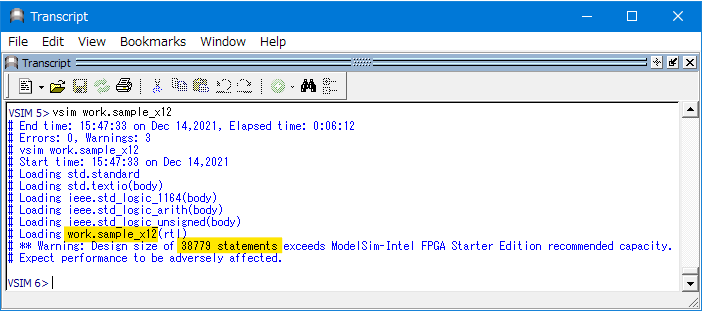

手元にある「配列もループもgenerateも知らない人が書いた12倍コピペ」という15,000行の恐ろしいVHDLモジュールsample_x12をModelSimでロードすると**38,779 statements**と表示され、速度制限がかかるようになります。

ログを見るとwork.sample_x12以外のモジュールはロードされていないので、この15,000行のモジュールはModelSimでは38,779ステートメントに相当し、ModelSim Intel Starterの制限10,000ステートメントを遙かに超えている事が分かります。

このソースから1行ずつコメントアウトしていくと、おおよそ3ステートメントずつ減っていきます。

元の38,779ステートメントを1/3で換算すると約13,000行になりますので、全体の15,000行に対してまあまあ妥当な数字に見えます。

という事は、ModelSimの10,000ステートメント制限はソースの有効行3,333行に相当すると想定されます。

自分で書いたソースの合計が3,333行という事で、小さなFPGAでも全体をロードすると簡単に到達しそうですね。

初期インストールされるライブラリはカウントされないので、例えばRAM・ROMをHDLから推論させるようなコードはステートメント数を消費するので不利になり、altera_mf等のライブラリをインスタンスした方がお得と言えます。

ループでインスタンスした場合のステートメント数

先の15,000行のVHDLsample_x12をループと配列を使って書き直したsampleはたったの400行になり、もちろん10,000ステートメントの制限はクリアできます。(FPGA実機へのフィット結果は同等)

ステートメント数は制限を超えないと表示されないので、どれだけ小さくなったのかこれでは分かりません。

そこで、モジュールsampleを以下のようにtopでfor-generateを使って50個インスタンスすると、11,800ステートメントと表示されましたので、sampleは236ステートメントと考えられます。

38,779→236ステートメントと、1%未満になってしまったので大丈夫か不安ですが、先述の通りFPGA実機へのフィット結果が同じなので機能は満たせています。

gen_loop: for I in 1 to 50 generate

sample_i: entity work.sample

port map (...);

end generate;

この事から、ModelSimのステートメント数はコンパイルしたユニークな行数ではなく、実際にインスタンス化した行数の合計という事が分かります。

Questaのインスタンス数

ModelSimでは38,779ステートメントで制限を超えたsample_x12をQuestaでロードしてみると、制限に関するメッセージは表示されず通常の速度で実行可能です。

Questaでは本当にソースの行数は関係ない事が分かります。

今度はtopで5,000回ループでインスタンスしてみます。

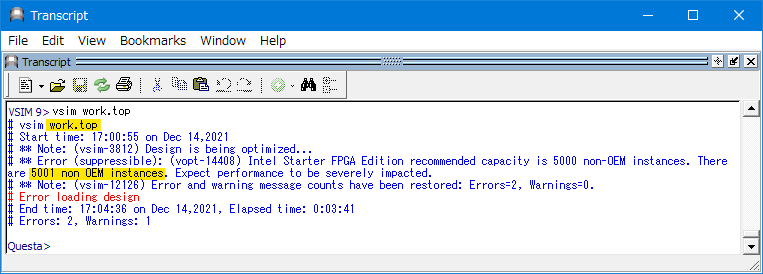

すると、5001 non OEM instancesと表示されエラーになりました。

topが1個、topでsample_x12を5,000個インスタンスするので合計5,001個ですので、計算通りです。

ModelSimとは違い、Questaではエラーなので実行できません。

topでのループ回数を4,999に変更して合計がちょうど5,000個になるようにすると、正常にロードされ実行も出来ます。

計算すると、**38,779ステートメント×4,999個=193Megaステートメント!!**でもQuestaでは実行可能です。

次はsample_x12を5,000個に戻し、topに追加でOEM instanceであるlpm_invのインスタンスを5,000個追加してみます。

結果は5001インスタンスのまま変わりませんでした。当然ですね。

gen_loop: for I in 1 to 5000 generate --5000個インスタンスする

inv_i: entity lpm.lpm_inv --lpm_invはOEMインスタンスなのでカウントされないはず

generic map (...)

port map (...);

sample_x12_i: entity work.sample_x12 --自分のモジュールはカウント対象

port map (...);

end generate;

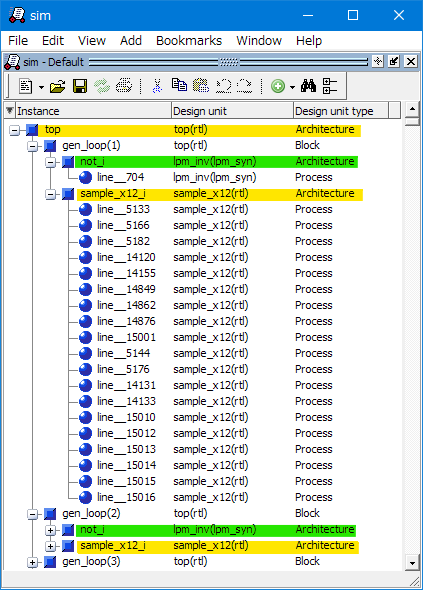

ちょうど5,000インスタンスのsimウインドウの表示

黄色マーカーがカウント対象インスタンス

緑色はOEMインスタンスなのでカウントの対象外

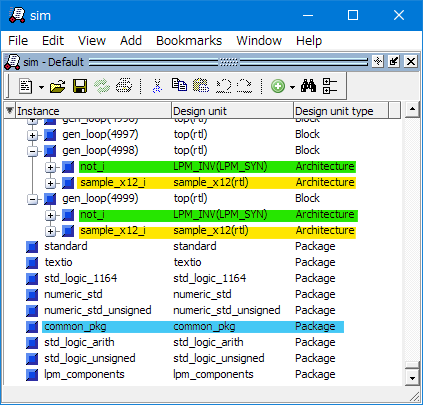

4998~4999番目のインスタンス表示

水色のOEMでないVHDLパッケージcommon_pkgもロードされているが、パッケージは対象外

まとめ

Questa Intel Starterの5,000インスタンス制限は、自分で書いたモジュールを実際にインスタンス化した数の合計です。

モジュールの行数は関係ありません。

という訳で、無償版でも相当大きなデザインがシミュレーションできる事になります。

自分で書いたモジュール合計が5000個って、ちょっと想像できないな…1

これまでQuartusの無償版では、ModelSimの10,000ステートメント制限がシミュレーションの懸案事項だったのですが、完全に解消されましたね。

これは非常に嬉しい。なんと言っても、ただでQuestaが使えるなんて、夢のようだわ。

Xilinxが混合言語に対応したVivadoシミュレータを無償版でも機能制限無し2で出しているので、これに対抗したのかもしれません。