1.背景

ここ最近FPGAを扱う以外に、Arduino関連のマイコンやネットワーク・ファイルシステムをサポートしているM5Stack、M5Stickなどのesp32系マイコンを扱う機会が多くなってきました。多くのネットや書籍の情報などを見ると、開発環境はArduino IDEを用いている場合が多いのが現状です。それらの情報でも指摘されていますが、ちょっと大きめのプログラムを書いたり、デバッグを行おうとすると、Arduino IDEの環境ではなかなか辛いものがあります。そこでそんな時は、Microsoft社が提供しているVSCodeでPlatformIOの拡張機能を使うと大変に便利です。

ところでVSCodeの拡張機能にはVerilog-HDLとVHDLをサポートしており、この機能を使ってHDLのコーディングを行い、VSCodeのターミナルからIntel FPGAの開発環境が使えると、何を(FPGA or マイコン or Raspberry Piなど)開発するかによって、その開発環境で提供しているエディタなどにいちいち変更する必要が無いので、とっても便利だと思います。また。ソフトウェア開発のエンジニアの方々は、VSCodeを使用する機会も多いと思うので、万が一FPGA開発を行うハードウェア設計に携わることになった時に、VSCodeが使用できると多少なりとも開発し易いのではないかと思います。

このような背景から今回のことをやってみようと思ったのがそもそものきっかけです。かなり力づくな所はありますが、とりあえず”できる”ことを目標にチャレンジ(そんな大げさなものではありませんが.....)してみたので、ここにその備忘録を記すことに致します。

2.準備

2.1. ダウンロード先

まずは、必要なソフトウェアを以下のサイトからダウンロードします。

【VSCode】

Download Visual Studio Code

*該当するOS(Windows, Linux)のインストールプログラムをダウンロード

【Intel FPGA開発環境(Quartus Lite:無償版)】

FPGAs ダウンロード・センター

*ダウンロードの際にユーザー登録が必要

*該当するOS(Windows, Linux)のインストールプログラムをダウンロード

2.2. インストール(Windows版)

VSCodeはダウンロードしてきたファイル(VSCodeUserSetup-x64-1.51.1.exe:2020年12月1日現在)を、そのまま実行してインストールします。

Quartus Lite はダウンロードしてきたファイルがtarファイル(Quartus-lite-20.1.1.720-windows.tar:2020年12月1日現在)になっているので、圧縮解凍ソフト(7zipなど)で解凍し、生成されたファイル「setup.bat」を実行してインストールします。(デフォルトでインストールすれば「C:\intelFPGA_lite」の下にインストールされます)

2.3. インストール(Linux版)

ここでのLinuxのディストリビューションはubuntu(18.04)を前提としています。(恐らくubuntu 20.04でもやり方はそれほど変わりないと思います)

VSCodeは、まずダウンロードしてきたファイル(code_1.51.1-1605051630_amd64.deb:2020年12月1日現在)の存在するディレクトリまで移動し、

sudo dpkg -i code_1.51.1-1605051630_amd64.deb

などと実行してインストールを行います。

Quartus Lite はダウンロードしてきたファイルがtarファイル(Quartus-lite-20.1.1.720-linux.tar:2020年12月1日現在)になっているので、圧縮解凍コマンド(tarコマンド)で解凍し、生成されたファイルを実行「./setup.sh」してインストールします。この時、今回手元の環境では、sudoを付けずに一般ユーザーの権限で「/tools」の下にインストールしました。(sudoを付けてインストールしたところ、Modelsimの起動が一般ユーザーで上手く行かなかったため)

tar xvf Quartus-lite-20.1.1.720-linux.tar

./setup.sh

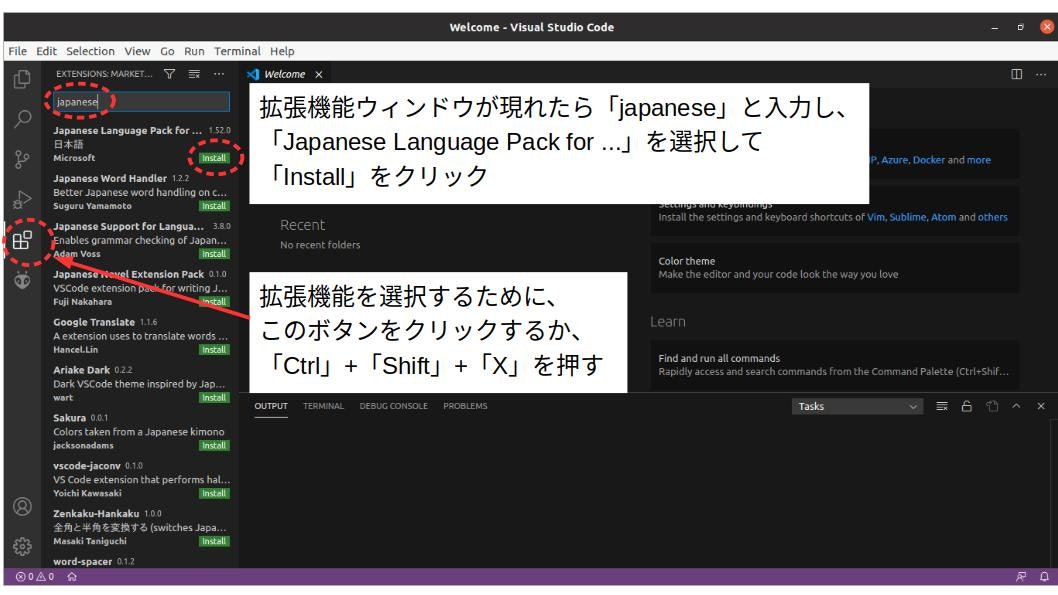

2.4. VSCodeの拡張機能の設定

VSCodeを起動(Widowsではアイコンをダブルクリック、Linuxではシェルから「code」と実行します)し、拡張機能のウィンドウを出力します。以下のようにVSCodeの画面の左側にあるボタンをクリックするか、「Ctrl」+「Shift」+「X」をVSCodeの画面上で押すと、拡張機能のウィンドウが出力されます。

まず、やらなくても良いのですが、日本語の環境を整えるために検索機能の入力ボックスに「japanese」と入力します。検索されると「Japanese Language Pack for.....」と現れてくる部分があるので、その右横にある緑色の「Install」ボタンをクリックしてインストールします。

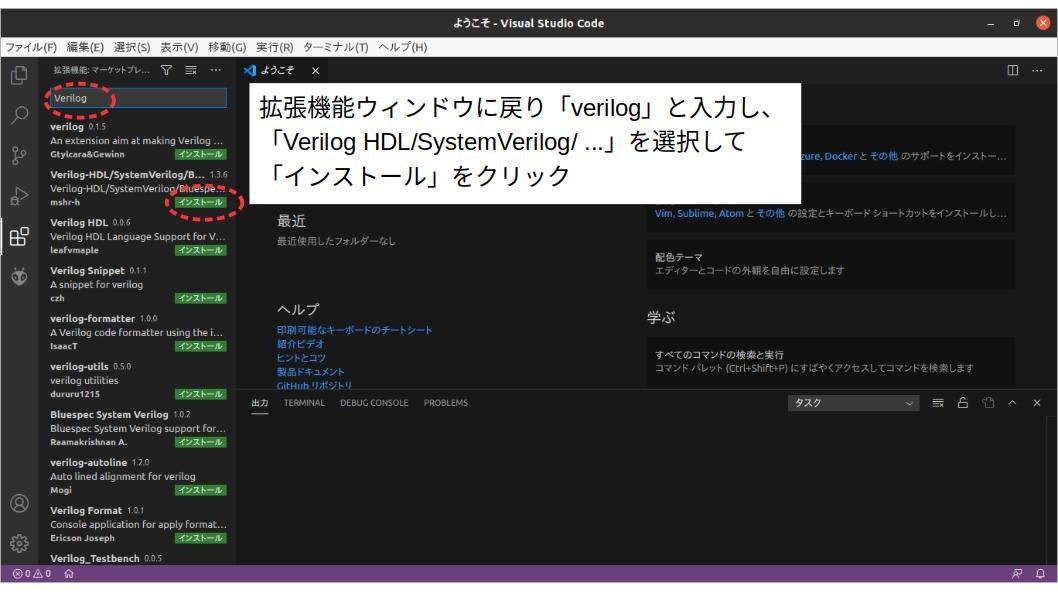

次にHDL(Verilog-HDLとVHDL)の言語サポート機能をインストールします。

まず、Verilog-HDLは上記の検索機能の入力ボックスに「Verilog」と入力します。いろいろ出てきますので試してみると良いと思いますが、今回は「Verilog-HDL/SystemVerilog/Bluespec.....」をインストールしました。日本語になっていれば緑色の「インストール」ボタンをクリックしてインストールします。

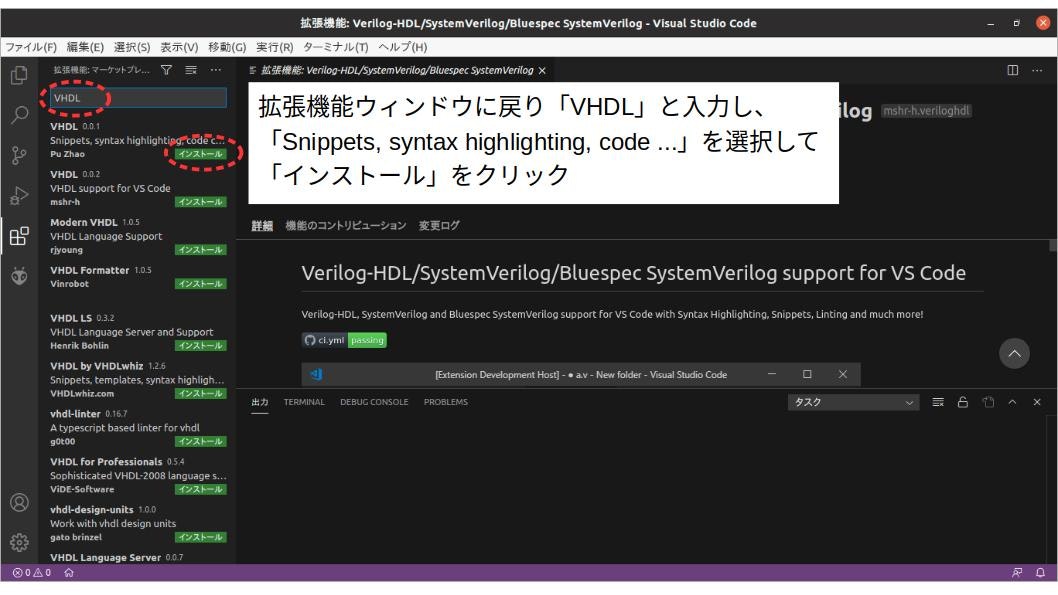

次にVHDLの機能をインストールするために、上記の検索機能の入力ボックスに「VHDL」と入力します。こちらも様々なものがあるので試してみると良いと思いますが、今回は1番先頭に出てくる「VHDL」の中に「Snippets, syntax highlighting, code.....」と記されたものをインストールしました。日本語になっていれば緑色の「インストール」ボタンをクリックしてインストールします。

以上でHDLの言語サポート機能の準備は終了です。

3.HDLソースコード

VSCodeのエディタ上でHDLのソース(RTLとテストベンチ)を作成してみます。ここでは1秒ごとに動作する4ビットのカウンタを作成してみます。作業フォルダはどこでも良いのですが、Windows上では、

【Windows:Verilog-HDLの場合】

C:\Temp\Quartus\Verilog-HDL\COUNT4

【Windows:VHDLの場合】

C:\Temp\Quartus\VHDL\COUNT4

の下に作成しています。

Linux上ではホームディレクトリ(ここでは/home/tori)の下を使う事にして、

【Linux:Verilog-HDLの場合】

/home/tori/Quartus/Verilog-HDL/COUNT4

【Linux:VHDLの場合】

/home/tori/Quartus/VHDL/COUNT4

としました。

3.1. Verilog-HDLの作成

VSCode上で「ファイル」-「新規ファイル」を選択します。いきなりエディタが出力されますので、「ファイル」-「名前を付けて保存」を選択し、「C:\Temp\Quartus\Verilog-HDL\COUNT4」(Windows)または「/home/tori/Quartus/Verilog-HDL/COUNT4」(Linux)に移動して、「COUNT4.v」として保存し、RTLファイルを作成します。

module COUNT4 (input CLK, RESET, output reg [3:0] COUNT);

parameter SEC1_MAX = 50000000; //50 MHz

reg [25:0] tmp_count; // 1秒のカウンタ

wire ENABLE;

always @(posedge CLK or negedge RESET)

begin

if (RESET == 1'b0) // RESETボタンは負論理

tmp_count <= 26'h0;

else if (ENABLE == 1'b1)

tmp_count <= 26'h0;

else

tmp_count <= tmp_count + 26'h1;

end

assign ENABLE = (tmp_count == (SEC1_MAX - 1))? 1'b1 : 1'b0;

always @(posedge CLK or negedge RESET)

begin

if (RESET == 1'b0) // RESETボタンは負論理

COUNT <= 4'h0;

else if (ENABLE == 1'b1) begin

COUNT <= COUNT + 4'h1;

end

end

endmodule

次に「T_COUNT4.v」として保存し、テストベンチを作成します。

`timescale 1 ns / 100 ps

module T_COUNT4;

reg CLK = 1'b0, RESET;

wire [3:0] COUNT;

parameter SIM_SEC1_MAX=4; // シミュレーション時4クロックに1回ENABLEを生成

parameter CYCLE = 20;

COUNT4 #(.SEC1_MAX(SIM_SEC1_MAX)) i0(.CLK(CLK), .RESET(RESET), .COUNT(COUNT));

always #(CYCLE/2)

CLK = ~CLK;

initial

begin

RESET = 1'b0; // RESETボタンは負論理

#CYCLE RESET = 1'b1;

#(CYCLE*SIM_SEC1_MAX*20) $stop;

end

endmodule

3.2. VHDLの作成

VSCode上で「ファイル」-「新規ファイル」を選択します。いきなりエディタが出力されますので、「ファイル」-「名前を付けて保存」を選択し、「C:\Temp\Quartus\VHDL\COUNT4」(Windows)または「/home/tori/Quartus/VHDL/COUNT4」(Linux)に移動して、「** COUNT4.vhd **」として保存し、RTLファイルを作成します。

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity COUNT4 is

generic (SEC1_MAX : integer := 50000000); -- 50 MHz

port (CLK, RESET : in std_logic;

COUNT : out std_logic_vector(3 downto 0));

end entity;

architecture RTL of COUNT4 is

signal tmp_count : std_logic_vector(25 downto 0); -- 1秒のカウンタ

signal ENABLE : std_logic;

signal COUNT_TMP : std_logic_vector(3 downto 0);

begin

COUNT <= COUNT_TMP;

process(CLK, RESET)

begin

if (RESET = '0') then -- RESETボタンは負論理

tmp_count <= (others => '0');

elsif (CLK'event and CLK = '1') then

if (ENABLE = '1') then

tmp_count <= (others => '0');

else

tmp_count <= tmp_count + '1';

end if;

end if;

end process;

ENABLE <= '1' when (tmp_count = (SEC1_MAX - 1)) else '0';

process(CLK, RESET)

begin

if (RESET = '0') then -- RESETボタンは負論理

COUNT_TMP <= X"0";

elsif (CLK'event and CLK = '1') then

if (ENABLE = '1') then

COUNT_TMP <= COUNT_TMP + '1';

end if;

end if;

end process;

end RTL;

次に「** T_COUNT4.vhd **」として保存し、テストベンチを作成します。

library IEEE;

use IEEE.std_logic_1164.all;

entity T_COUNT4 is

end entity;

architecture SIM of T_COUNT4 is

signal CLK : std_logic := '0';

signal RESET : std_logic;

signal COUNT : std_logic_vector(3 downto 0);

component COUNT4 is

generic (SEC1_MAX : integer := 50000000);

port (CLK, RESET : in std_logic;

COUNT : out std_logic_vector(3 downto 0));

end component;

constant SIM_SEC1_MAX : integer := 4; -- シミュレーション時4クロックに1回ENABLEを生成

constant CYCLE : time := 20 ns;

begin

I0 : COUNT4 generic map(SEC1_MAX => SIM_SEC1_MAX)

port map(CLK => CLK, RESET => RESET, COUNT => COUNT);

process

begin

wait for (CYCLE/2);

CLK <= not CLK;

end process;

process

begin

RESET <= '0'; -- RESETボタンは負論理

wait for CYCLE;

RESET <= '1';

wait for (CYCLE*SIM_SEC1_MAX*20);

assert false

report "Simuletion Complete!!"

severity Failure;

wait;

end process;

end SIM;

各ソースを入力する際にキーワードがハイライトされたり、使用している信号やキーワードの候補が出てきたりと、いろいろソースを入力する際に補助してくれる機能が嬉しいです。これらの機能はQuartusの機能にもありますが、普段使用しているVSCodeのエディタからできるというのがとても便利だと思います。あと使っている感触としては、VSCode自体FPGAのツールよりも”軽い”気がするのも個人的には気に入っているところです。(FPGA関連のツールは、多かれ少なかれ様々な機能が搭載されているためエディタの入力までたどり着くのにも、プログラムを起動してからそれなりに時間がかかるので)入力してみて使い難ければ、別の拡張機能を試したりすると良いでしょう。

4. VSCodeによるIntel FPGAツールの起動

ツールの実行にあたってターミナルを起動します。WindowsではPowerShellが、Linuxではbashのシェルが立ち上がります。VSCodeのプルダウンメニューの「ターミナル」-「新しいターミナル」を選択して立ち上げます。

ターミナルが立ち上がったら、HDLのソースが存在するフォルダ、ディレクトリに移動します。

【Windows:Verilog-HDLの場合】

cd C:\Temp\Quartus\Verilog-HDL\COUNT4

【Windows:VHDLの場合】

cd C:\Temp\Quartus\VHDL\COUNT4

【Linux:Verilog-HDLの場合】

cd ~/Quartus/Verilog-HDL/COUNT4

【Linux:VHDLの場合】

cd ~/Quartus/VHDL/COUNT4

移動に際してはフォルダ名やディレクトリ名をある程度打ったところで「Tab」キーを押すと、該当するフォルダ名やディレクトリ名が存在すれば、その名前を自動的に拡張してくれます。こうすることでフォルダ名,ディレクトリ名の打ち間違いを防ぐことが出来ます。

4.1. Modelsimによるシミュレーション

移動出来たら、まずModelsimのコマンドが存在するフォルダ名,ディレクトリ名を、以下のコマンドでコマンドパスを通します。(既に通っている場合には以下の操作を行う必要はありません)

【Windowsの場合】

$ENV:Path="C:\intelFPGA_lite\20.1\modelsim_ase\win32aloem;"+$ENV:Path

【Linuxの場合】

export PATH=/tools/intelFPGA_lite/20.1/modelsim_ase/bin:$PATH

次にModelsimのシミュレーションをバッチで行うための「doファイル:COUNT4.do」を、作業フォルダ,ディレクトリ直下に以下のように作成します。

【Windows:Verilog-HDLの場合】

quit -sim

cd c:/temp/Quartus/Verilog-HDL/COUNT4

vlib work

vlog -reportprogress 300 -work work C:/Temp/Quartus/Verilog-HDL/COUNT4/COUNT4.v

vlog -reportprogress 300 -work work C:/Temp/Quartus/Verilog-HDL/COUNT4/T_COUNT4.v

vsim -gui work.T_COUNT4

add wave -position insertpoint \

sim:/T_COUNT4/SIM_SEC1_MAX \

sim:/T_COUNT4/CYCLE \

sim:/T_COUNT4/CLK \

sim:/T_COUNT4/RESET \

sim:/T_COUNT4/i0/ENABLE

add wave -position insertpoint -radix hex \

sim:/T_COUNT4/COUNT

add wave -position insertpoint -radix decimal \

sim:/T_COUNT4/i0/tmp_count

run -all

【Windows:VHDLの場合】

quit -sim

cd c:/temp/Quartus/VHDL/COUNT4

vlib work

vlog -reportprogress 300 -work work C:/Temp/Quartus/VHDL/COUNT4/COUNT4.vhd

vlog -reportprogress 300 -work work C:/Temp/Quartus/VHDL/COUNT4/T_COUNT4.vhd

vsim -gui work.T_COUNT4

add wave -position insertpoint \

sim:/T_COUNT4/SIM_SEC1_MAX \

sim:/T_COUNT4/CYCLE \

sim:/T_COUNT4/CLK \

sim:/T_COUNT4/RESET \

sim:/T_COUNT4/i0/ENABLE

add wave -position insertpoint -radix hex \

sim:/T_COUNT4/COUNT

add wave -position insertpoint -radix decimal \

sim:/T_COUNT4/i0/tmp_count

run -all

【Linux:Verilog-HDLの場合】

quit -sim

cd /home/tori/Quartus/Verilog-HDL/COUNT4

vlib work

vlog -reportprogress 300 -work work /home/tori/Quartus/Verilog-HDL/COUNT4/COUNT4.v

vlog -reportprogress 300 -work work /home/tori/Quartus/Verilog-HDL/COUNT4/T_COUNT4.v

vsim -gui work.T_COUNT4

add wave -position insertpoint \

sim:/T_COUNT4/SIM_SEC1_MAX \

sim:/T_COUNT4/CYCLE \

sim:/T_COUNT4/CLK \

sim:/T_COUNT4/RESET \

sim:/T_COUNT4/i0/ENABLE

add wave -position insertpoint -radix hex \

sim:/T_COUNT4/COUNT

add wave -position insertpoint -radix decimal \

sim:/T_COUNT4/i0/tmp_count

run -all

【Linux:VHDLの場合】

quit -sim

cd /home/tori/Quartus/VHDL/COUNT4

vlib work

vlog -reportprogress 300 -work work /home/tori/Quartus/VHDL/COUNT4/COUNT4.vhd

vlog -reportprogress 300 -work work /home/tori/Quartus/VHDL/COUNT4/T_COUNT4.vhd

vsim -gui work.T_COUNT4

add wave -position insertpoint \

sim:/T_COUNT4/SIM_SEC1_MAX \

sim:/T_COUNT4/CYCLE \

sim:/T_COUNT4/CLK \

sim:/T_COUNT4/RESET \

sim:/T_COUNT4/i0/ENABLE

add wave -position insertpoint -radix hex \

sim:/T_COUNT4/COUNT

add wave -position insertpoint -radix decimal \

sim:/T_COUNT4/i0/tmp_count

run -all

上記のdoファイル作成にあたってはModelSim Command Reference Manualを参考にしました。

作成出来たら、ターミナル上で以下のコマンドを実行します。

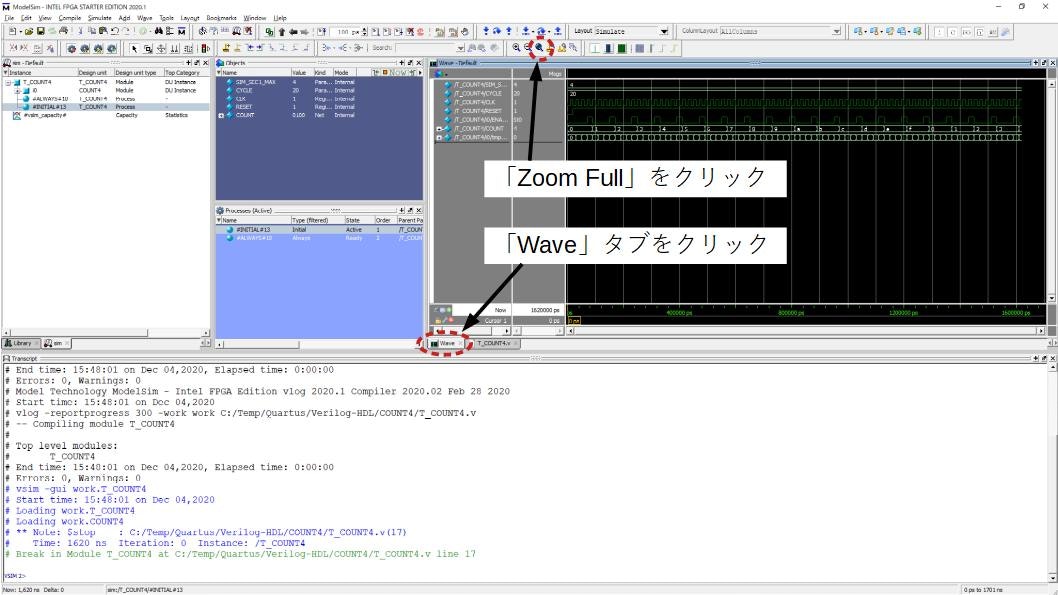

vsim -do COUNT4.do

実行してコンパイルなど全てが成功すると、以下のようなウィンドウが立ち上がり、波形表示のタブ(Wave)を選択して、「Zoom Full」のアイコンをクリックすると、全体の波形を観測することが出来ます。

なお、上記のコマンドに「-c」を付けると、GUIのウィンドウは立ち上がらずにシミュレーションを実行してくれます。

vsim -c -do COUNT4.do

4.2. Quartusによるコンパイル

まずQuartusのコマンドが存在するフォルダ名,ディレクトリ名を、以下のコマンドでコマンドパスを通します。(既に通っている場合には以下の操作を行う必要はありません)

【Windowsの場合】

$ENV:Path="C:\intelFPGA_lite\20.1\quartus\bin64;"+$ENV:Path

【Linuxの場合】

export PATH=/tools/intelFPGA_lite/20.1/quartus/bin:$PATH

次にQuartusを使用してRTLファイル(COUNT4.v, COUNT4.vhd)をバッチでコンパイルします。コンパイルする前に以下の2つのファイル「.qpf:Quartusのプロジェクトファイル、.qsf:ピンアサイン等を行う制約ファイル」を作成します。なおFPGAのデバイス名や各信号のピンへのアサインなどの設定などは、手元にDE0-Nano-SoC Kit/Atlas-SoC KitというFPGAボードがあったので、ここではこのFPGAボードをターゲットにしています。お手元の環境に合わせて作成して下さい。

【Verilog-HDLの場合】

QUARTUS_VERSION = "20.1"

DATE = "22:39:03 November 29, 2020"

PROJECT_REVISION = "COUNT4"

set_global_assignment -name FAMILY "Cyclone V"

set_global_assignment -name DEVICE 5CSEMA4U23C6

set_global_assignment -name TOP_LEVEL_ENTITY COUNT4

set_global_assignment -name ORIGINAL_QUARTUS_VERSION 20.1.0

set_global_assignment -name PROJECT_CREATION_TIME_DATE "22:39:03 NOVEMBER 29, 2020"

set_global_assignment -name LAST_QUARTUS_VERSION "20.1.1 Lite Edition"

set_global_assignment -name VERILOG_FILE count4.v

set_global_assignment -name PROJECT_OUTPUT_DIRECTORY output_files

set_global_assignment -name MIN_CORE_JUNCTION_TEMP 0

set_global_assignment -name MAX_CORE_JUNCTION_TEMP 85

set_global_assignment -name ERROR_CHECK_FREQUENCY_DIVISOR 256

set_location_assignment PIN_V11 -to CLK

set_location_assignment PIN_AH17 -to RESET

set_location_assignment PIN_W15 -to COUNT[0]

set_location_assignment PIN_AA24 -to COUNT[1]

set_location_assignment PIN_V16 -to COUNT[2]

set_location_assignment PIN_V15 -to COUNT[3]

【VHDLの場合】

QUARTUS_VERSION = "20.1"

DATE = "22:39:03 November 29, 2020"

PROJECT_REVISION = "COUNT4"

set_global_assignment -name FAMILY "Cyclone V"

set_global_assignment -name DEVICE 5CSEMA4U23C6

set_global_assignment -name TOP_LEVEL_ENTITY COUNT4

set_global_assignment -name ORIGINAL_QUARTUS_VERSION 20.1.0

set_global_assignment -name PROJECT_CREATION_TIME_DATE "22:39:03 NOVEMBER 29, 2020"

set_global_assignment -name LAST_QUARTUS_VERSION "20.1.1 Lite Edition"

set_global_assignment -name VHDL_FILE count4.vhd

set_global_assignment -name PROJECT_OUTPUT_DIRECTORY output_files

set_global_assignment -name MIN_CORE_JUNCTION_TEMP 0

set_global_assignment -name MAX_CORE_JUNCTION_TEMP 85

set_global_assignment -name ERROR_CHECK_FREQUENCY_DIVISOR 256

set_location_assignment PIN_V11 -to CLK

set_location_assignment PIN_AH17 -to RESET

set_location_assignment PIN_W15 -to COUNT[0]

set_location_assignment PIN_AA24 -to COUNT[1]

set_location_assignment PIN_V16 -to COUNT[2]

set_location_assignment PIN_V15 -to COUNT[3]

作成出来たらターミナル上で以下のコマンドを実行します。

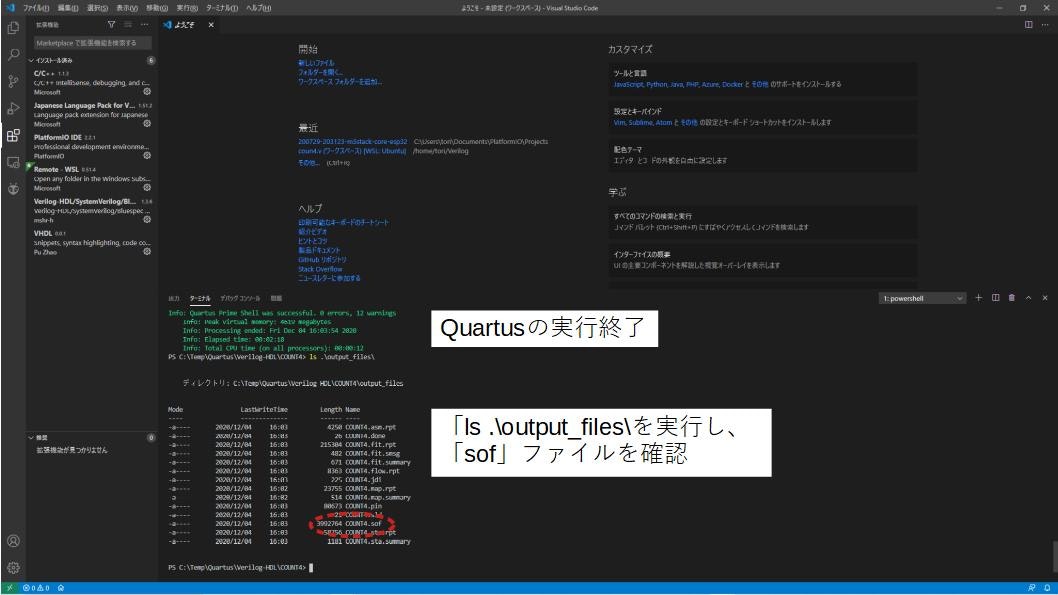

quartus_sh --flow compile COUNT4

エラーなく終了すると、実行しているフォルダ、ディレクトリの直下に「output_files」という名前でフォルダ、ディレクトリが作成されているはずです。この「output_files」の直下にFPGAをプログラムするための「COUNT4.sof」ファイルが出力されています。

4.3. QuartusによるFPGAのプログラム

次に、FPGAボード「DE0-Nano-SoC Kit/Atlas-SoC Kit」とPCをUSB ケーブルで接続し、FPGAボードの電源を入れます。既にコマンドパスが通っているので、準備が出来たら以下のコマンドでFPGAにダウンロードします。

【Windowsの場合】

quartus_pgm -c DE-SOC[USB-1] -m jtag -o "p;output_files/COUNT4.sof@2"

【Linuxの場合】

quartus_pgm -c DE-SOC[3-1] -m jtag -o "p;output_files/COUNT4.sof@2"

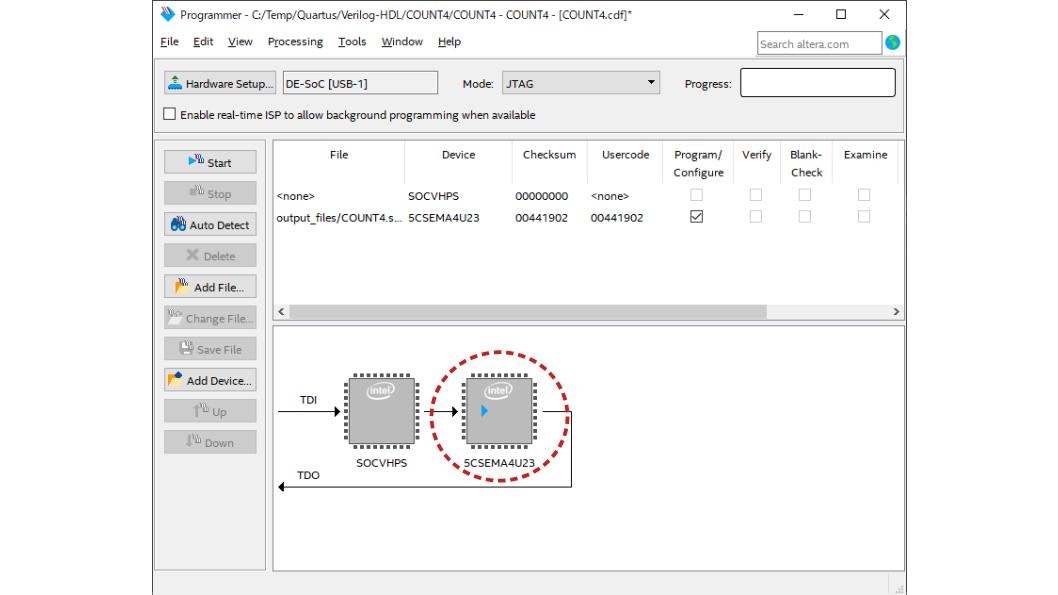

上記のコマンドの中で「p」はプログラムの意味で、プログラム、消去、ベリファイを行いたい場合には、「pev」と指定します。また最後の「@2」は、使用している「DE0-Nano-SoC Kit/Atlas-SoC Kit」のFPGAにはプロセッサも搭載されているので、FPGAデバイスの順番が2番目のためです。実際に使用しているFPGAボードのデバイスの接続状況に合わせて、この部分を変更する必要があります。(以下にQuartusのProgrammerのツールをGUIで実行した時の様子を示します)

またWindowsのPowerShellやLinuxのbashでは「p」に続く「;」がコマンドの区切りとみなされるので、-oに続く部分は「"p;output_files/COUNT4.sof@2"」のように「" "」で囲む必要がありましたので注意が必要です。(Windowsのコマンドプロント上では囲まなくてもOKでした)

quartus_pgmコマンドの詳細は、Quartus II Scripting Reference Manual「2-50」ページ辺りを参照すると良いでしょう。

ボード上で4つのLEDがカウントの値を表示して1秒ごとに動作していれば成功です。動作している様子の動画はこちらから。

4.4. Linux上(ubuntu)でIntel FPGAボードを認識させる設定について

Linux上(ここでの説明はubuntuのディストリビューションについてです)でFPGAボードを認識させるためには、以下の設定が施されている必要があります。/etc/udev/rules.dの下に「51-usbblaster.rules」というファイル名で、以下の内容で記述されている必要があります。この情報はUsing USB Blaster / USB Blaster II under Linuxを参照しました。

# USB Blaster

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6001", MODE="0666", NAME="bus/usb/$env{BUSNUM}/$env{DEVNUM}", RUN+="/bin/chmod 0666 %c"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6002", MODE="0666", NAME="bus/usb/$env{BUSNUM}/$env{DEVNUM}", RUN+="/bin/chmod 0666 %c"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6003", MODE="0666", NAME="bus/usb/$env{BUSNUM}/$env{DEVNUM}", RUN+="/bin/chmod 0666 %c"

# USB Blaster II

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6010", MODE="0666", NAME="bus/usb/$env{BUSNUM}/$env{DEVNUM}", RUN+="/bin/chmod 0666 %c"

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTR{idVendor}=="09fb", ATTR{idProduct}=="6810", MODE="0666", NAME="bus/usb/$env{BUSNUM}/$env{DEVNUM}", RUN+="/bin/chmod 0666 %c"

このファイルを作成して保存した後、以下のコマンドでudevを再起動します。

sudo /etc/init.d/udev restart

VSCodeのターミナルから

quartus_pgm -l

と実行し、デバイス名(手元の環境では「DE-SOC[3-1]」などと表示される)が出力されればFPGAボードが、Linux側から認識されています。

5. jsonファイルによるタスクの実行

VSCodeではtask.jsonファイルを作成することによって、「Ctrl」+「Shift」+「B」などと入力して、現れるメニューから該当するものを選択してコマンドを実行できます。ここではこの仕組みを作成してみます。

5.1. 実行するプログラムのコマンドファイルの作成(Windows版)

もっと良い方法があると思いますが、とりあえず”できる”ことを目標にしているので、以下のようなコマンドファイル(「vsim.bat」、「quartus_sh.bat」、「quartus_pgm.bat」)を、「C:\Temp\Quartus\Verilog-HDL\COUNT4」と「C:\Temp\Quartus\VHDL\COUNT4」の直下に作成しました。

set CMD_NAME=C:\intelFPGA_lite\20.1\modelsim_ase\win32aloem\vsim

%CMD_NAME% -do COUNT4.do

set CMD_NAME=C:\intelFPGA_lite\20.1\quartus\bin64\quartus_sh

%CMD_NAME% --flow compile COUNT4

set CMD_NAME=C:\intelFPGA_lite\20.1\quartus\bin64\quartus_pgm

%CMD_NAME% -c DE-SOC[USB-1] -m jtag -o "p;output_files/COUNT4.sof@2"

これらのコマンドファイルをtask.jsonから呼び出すことにします。

5.2. 実行するプログラム用のMakefileの作成(Linux版)

Windowsと同じようにコマンドファイルを作成してもできますが、せっかくLinuxにはmakeの環境があるので、Makefileを作成することにより、makeで実行できるようにしました。以下のような「Makefile」を、「/home/tori/Quartus/Verilog-HDL/COUNT4」と「/home/tori/Quartus/VHDL/COUNT4」の直下に作成しました。

QUARTUS_INSTALL_DIR=/tools/intelFPGA_lite/20.1/

PROJECT_NAME=COUNT4

PROG_SIM=$(QUARTUS_INSTALL_DIR)/modelsim_ase/bin/vsim

PROG_SYNTH=$(QUARTUS_INSTALL_DIR)/quartus/bin/quartus_sh

PROG_PROGRAMMER=$(QUARTUS_INSTALL_DIR)/quartus/bin/quartus_pgm

all:

make SIM

make SYNTH

make PROG

SIM :

$(PROG_SIM) -do $(PROJECT_NAME).do

SYNTH :

$(PROG_SYNTH) --flow compile $(PROJECT_NAME)

PROG :

$(PROG_PROGRAMMER) -c DE-SoC[3-1] -m jtag -o "P;output_files/$(PROJECT_NAME).sof@2"

このMakefileをmakeコマンドで、task.jsonから呼び出すことにします。

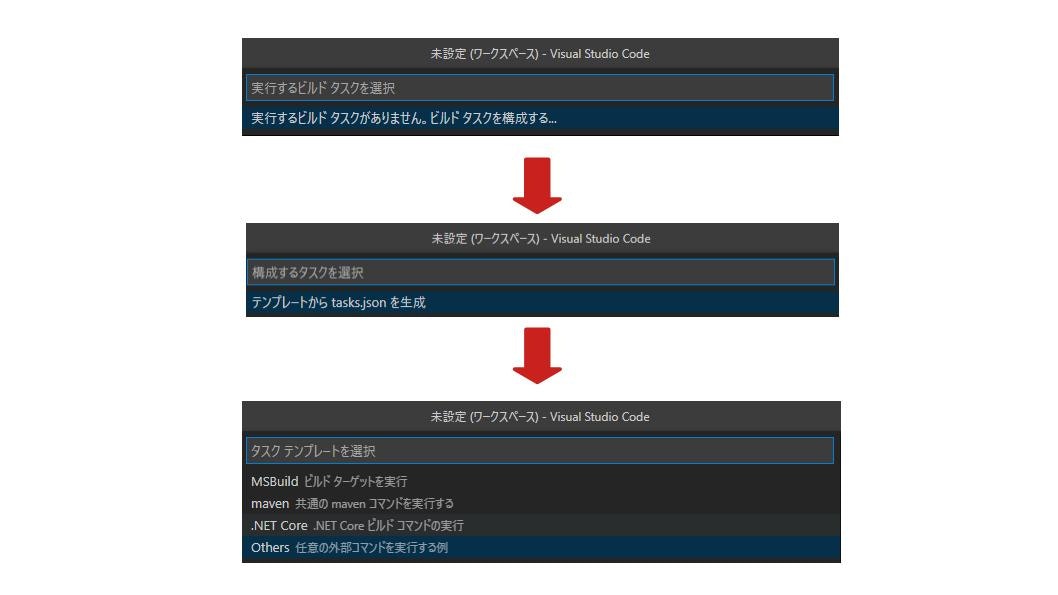

5.3. task.jsonファイルのテンプレートの作成

まず該当するフォルダをワークスペースに追加します。VSCode上で「ファイル」-「フォルダをワークスペースに追加」を選択し、該当する作業フォルダ(例えば「C:\Temp\Quartus\Verilog-HDL\COUNT4」)を選択します。左側のウィンドウに追加したフォルダの中身が現れます。

次に「Ctrl」+「Shift」+「B」を入力し、上部に現れたウィンドウに、

実行するビルドタスクを選択

実行するビルドがありません。ビルドタスクを構成する...

と現れますので、「ビルドタスクを構成する...」部分をクリックします。次に、

構成するタスクを選択

テンプレートからtask.jsonを生成

と現れますので、「テンプレートからtask.jsonを生成」をクリックします。次に、

タスクテンプレートを選択

MSBuild ビルド ターゲットを実行

maven 共通の maven コマンドを実行する

.NET Core .NET Core ビルド コマンドを実行

Others 任意の外部コマンドを実行する例

と現れますので、「Others 任意の外部コマンドを実行する例」をクリックします。

この操作により作業フォルダに「.vscode」が生成され、その直下に「task.json」が生成されます。ウィンドウにtask.jsonのテンプレートの中身が表示されます。

5.4. task.jsonファイルの編集(Windows)

以下のようにtask.jsonファイルを書き換えます。以下の例はVerilog-HDL版です。必要に応じて、「"command":」部分のフォルダの名前を環境に合わせて変更して下さい。

{

// See https://go.microsoft.com/fwlink/?LinkId=733558

// for the documentation about the tasks.json format

"version": "2.0.0",

"tasks": [

{

"label": "All",

"type": "shell",

"command": "cd C:/Temp/Quartus/Verilog-HDL/COUNT4; ./vsim.bat; ./quartus_sh.bat; ./quartus_pgm.bat",

"problemMatcher": [],

"group": {

"kind": "build",

"isDefault": true

}

},

{

"label": "Simulation",

"type": "shell",

"command": "C:/Temp/Quartus/Verilog-HDL/COUNT4/vsim.bat",

"problemMatcher": [],

"group": {

"kind": "build",

"isDefault": true

}

},

{

"label": "Synthesize",

"type": "shell",

"command": "C:/temp/Quartus/Verilog-HDL/COUNT4/quartus_sh.bat",

"problemMatcher": [],

"group": {

"kind": "build",

"isDefault": true

}

},

{

"label": "Download",

"type": "shell",

"command": "C:/temp/Quartus/Verilog-HDL/COUNT4/quartus_pgm.bat",

"problemMatcher": [],

"group": {

"kind": "build",

"isDefault": true

}

}

]

}

5.5. task.jsonファイルの編集(Linux)

以下のようにtask.jsonファイルを書き換えます。

{

// See https://go.microsoft.com/fwlink/?LinkId=733558

// for the documentation about the tasks.json format

"version": "2.0.0",

"tasks": [

{

"label": "All",

"type": "shell",

"command": "make",

"problemMatcher": [],

"group": {

"kind": "build",

"isDefault": true

}

},

{

"label": "Simulation",

"type": "shell",

"command": "make SIM",

"problemMatcher": [],

"group": {

"kind": "build",

"isDefault": true

}

},

{

"label": "Synthesize",

"type": "shell",

"command": "make SYNTH",

"problemMatcher": [],

"group": {

"kind": "build",

"isDefault": true

}

},

{

"label": "Download",

"type": "shell",

"command": "make PROG",

"problemMatcher": [],

"group": {

"kind": "build",

"isDefault": true

}

}

]

}

5.6. task.jsonファイルの実行

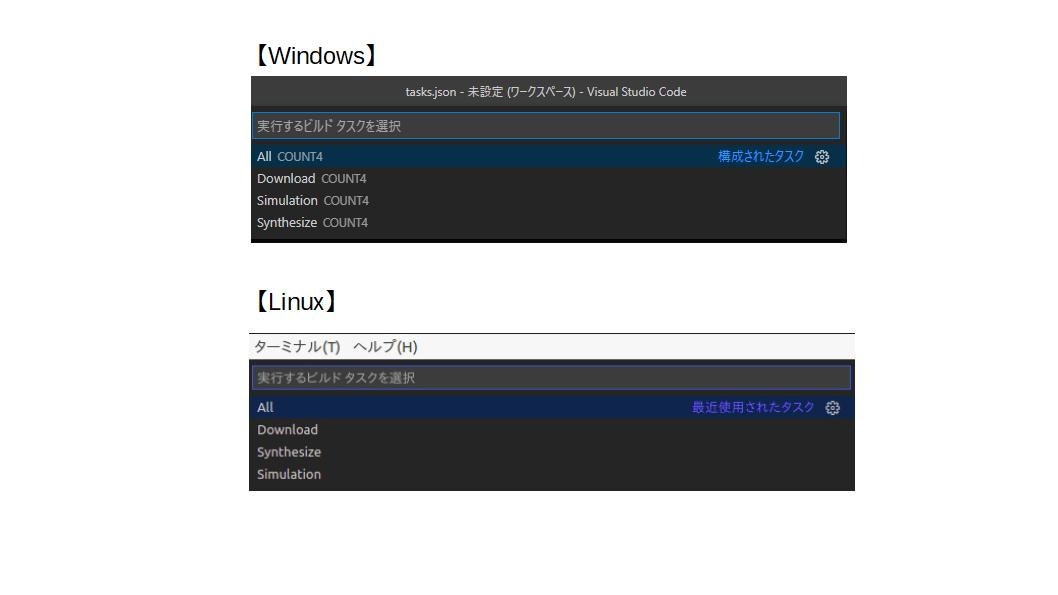

ファイルの編集が完了したら、「Ctrl」+「Shift」+「B」を押すと、VSCodeの上部の方に、

【Windowsの場合】

ALL COUNT4

Simulation COUNT4

Synthesize COUNT4

Download COUNT4

【Linuxの場合】

ALL

Simulation

Synthesize

Download

などと現れますので、該当する部分を選択してコマンドが実行できればOKです。

6. まとめ

今回、VSCodeでHDLのソースコードを書いて、VSCode上のターミナルからバッチで各ツールのコマンドを実行して、最終的にFPGAへのダウンロードまで行うことが出来ました。途中、シミュレーションのための「doファイル」やQuartusを実行するためのプロジェクトファイルなどの作成が必要でしたが、慣れてくれば今回のそれぞれのファイルをひな形にして、変更すべき箇所(フォルダ・ディレクトリ名やファイル名等)を変更するだけで実行できると思います。(それほど修正量は多くないと思います)

ここまでの内容が、多少なりともお役に立つことがあれば幸いです。