こんにちは。メインエディタは恋に落ちるエディタSublime Text 2な@tethys_seesaaです。

どれくらい恋に落ちるかはこの辺りをご参照下さい。

はじめに。

SystemVerilogってOOPですよね。面倒ですよね。怖いですよね。

某社の人はオブジェクト指向を恐れるなかれ!とおっしゃいますが、SystemVerilogでOOPは面倒です、怖いです、はい。

とはいえ、OOPなSystemVerilogのコードジャンプぐらいはSublime Text 2でできるように情報をかき集めてまとめてみました。

環境はCentOS 6.5です。

コードジャンプといえば、

はい、ctagsですね。

CentOSでインストールされているctagsを打ち込むとこんな感じです。

$ ctags --list-languages

:

Tcl

Tex

Vera

Verilog

VHDL

Vim

:

ということで、SystemVerilogはありません。Veraはなぜかあります(笑)。

SystemVerilogを作ってみましょう。

ctagsプラグインのインストール

こちらを参照して下さい。

CentOSでも、ctagsプラグインは/usr/local/binを前提にしているようなので、/usr/binからctagsのシンボリックリンクを貼りました。

SystemVerilog用設定ファイル

Verification Guildのこのコードを参考にしました。参考じゃない…。

--langdef=SystemVerilog

--langmap=SystemVerilog:.sv.svh.svi

--regex-SystemVerilog=/^\s*(\b(static|local|virtual|protected)\b)*\s*\bclass\b\s*(\b\w+\b)/\3/c,class/

--regex-SystemVerilog=/^\s*(\b(static|local|virtual|protected)\b)*\s*\btask\b\s*(\b(static|automatic)\b)?\s*(\w+::)?\s*(\b\w+\b)/\6/t,task/

--regex-SystemVerilog=/^\s*(\b(static|local|virtual|protected)\b)*\s*\bfunction\b\s*(\b(static|automatic)\b)?\s*\b\w+\b(\s*\[.+\])*\s*(\w+::)?\s*(\b\w+\b)/\7/f,function/

--regex-SystemVerilog=/^\s*\bmodule\b\s*(\b\w+\b)/\1/m,module/

--regex-SystemVerilog=/^\s*\bprogram\b\s*(\b\w+\b)/\1/p,program/

--regex-SystemVerilog=/^\s*\binterface\b\s*(\b\w+\b)/\1/i,interface/

--regex-SystemVerilog=/^\s*\btypedef\b\s+.*\s+(\b\w+\b)\s*;/\1/e,typedef/

--regex-SystemVerilog=/^\s*`define\b\s*(\b\w+\b)/\1/d,define/

--regex-SystemVerilog=/}\s*(\b\w+\b)\s*;/\1/e,typedef/

--regex-SystemVerilog=/^\s*(\b(static|local|private|rand)\b)*\s*(\b(shortint|int|longint)\b)\s*(\bunsigned\b)?(\s*\[.+\])*\s*(\b\w+\b)/\7/v,variable/

--regex-SystemVerilog=/^\s*(\b(static|local|private|rand)\b)*\s*(\b(byte|bit|logic|reg|integer|time)\b)(\s*\[.+\])*\s*(\b\w+\b)/\6/v,variable/

--regex-SystemVerilog=/^\s*(\b(static|local|private)\b)*\s*(\b(real|shortreal|chandle|string|event)\b)(\s*\[.+\])*\s*(\b\w+\b)/\6/v,variable/

--regex-SystemVerilog=/(\b(input|output|inout)\b)?\s*(\[.+\])*\s*(\b(wire|reg|logic)\b)\s*(\[.+\])*\s*(#(\(.+\)|\S+)\))?\s*(\b\w+\b)/\9/v,variable/

--regex-SystemVerilog=/(\b(parameter|localparam)\b).+(\b\w+\b)\s*=/\3/a,parameter/

--SystemVerilog-kinds=+ctfmpied

こちらを、 ~/.ctags として保存します。

サンプルコード

いかにもな、OOPコードを用意してみました。

class base;

int x = -1;

function new (int a);

x = a;

endfunction

virtual function void invoke();

$display("Error!");

endfunction

endclass

class extend extends base;

function new(int a);

super.new(a);

endfunction

function void invoke();

$display("Good!");

endfunction

endclass

program tb();

base b;

extend e;

initial begin

e = new(8);

e.invoke();

b = new(5);

b.invoke();

end

endprogram

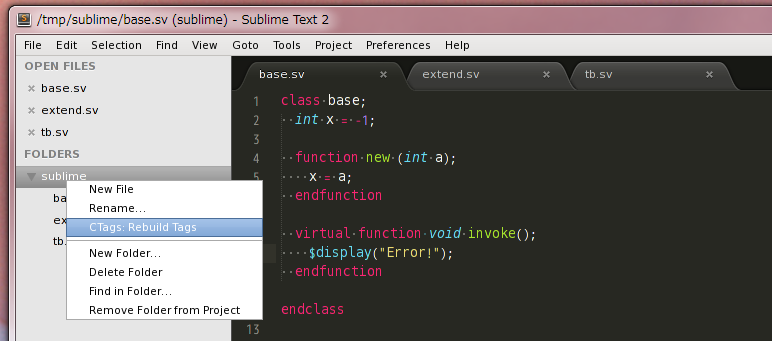

ctagsを実行する。

Linux版だとショートカットキーが割り当てられていないので、プロジェクトファイルから指定します。

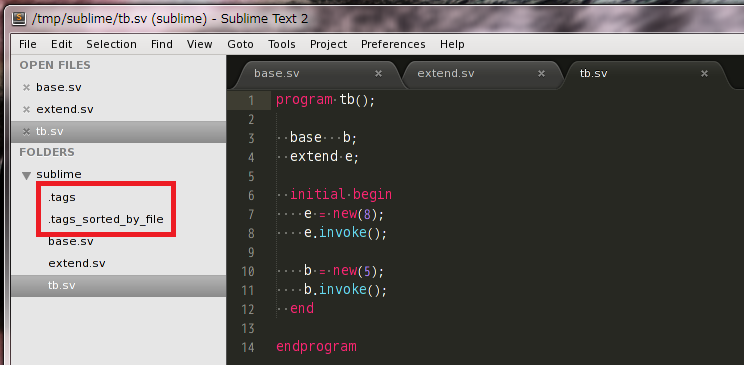

うまくいくと、以下のような二つの.tagsファイルができます。このファイルは特に編集しないので、編集無視リストに放り込んでもいいです。

あとは、

例えば、tb.svにある「base」にカーソルを合わせて、Ctrl+T, Ctrl+T を実行すると、定義しているclassのあるコードにジャンプします。元のコードに戻るには、Ctrl+T, Ctrl+Bです。classをCtrl+T, Ctrl+Tしていくと、ベースclassに戻るはずです。

で、ナニが嬉しいの?

UVMとか導入するとき?

おわりに。

vimにctagsは常識らしいですし、Sublime Textでもctagsはほぼ常識となりつつあるようです。

SystemVerilog + Sublime Text 2は無かったのでおぼえがきに記しました。

ctagsのSystemVerilogはメンテナンス誰かしてくれませんかねー。

おしまい。