はじめに。

GitHubを検索していたら、svparseいうSystemVerilog向けパーサーが、

一か月ほど前に頻繁にCommitされていたので使ってみることにした。

むろん環境はSublime Text 3で、出力されたファイルをパースして、SystemVerilogコード群を読み込ませてみる。

svparseって?

SystemVerilog 2012に準拠したパーサーらしい。

パーサー自身はJava、周りのユーティリティはPythonで実装されている。

SystemVeilogなので、対象はVerilogファイルでもオッケー。

README.mdに記述されている通り、目指すところと目指していないところが明確になっている。

目指すところは、SystemVerilogのパーサーと、シミュレーターのオプションやターゲットファイルをパースできるフォーマット(今現在はXMLのみっぽい)のテキストファイルを出力させることである。

必要な動作環境

How to Runにある情報と、実際にインストールさせた

ところ、以下の通り。

- Oracle and OpenJDK 7

- Python 2.6(2.7以降が望ましい)

中のPythonコードをちょっと覗いたら、str.format関数を使っているので、2.6以降が必須で、いろいろ調べると、2.7が無難。

こういう環境がデフォでそろっているLinuxホストって、企業のセルベースLSIの開発環境にあまりないんだよね…。

今回も、Ubuntu 14.04 LTSでやってみた。

コンパイルとインストール

コンパイルは記載されている通りに行う。

./regen.py

./gradlew installApp

./build/install/svparseにbinとlibができているので、/usr/local/bin等、PATHが通っているところにコピーすれば、インストールはオッケー。

パースするXMLファイルを作成する

tools/simshim.pyで作成することができる。

このスクリプトの中を覗くと、+incdir+とか+define+とか-fとか、Verilogシミュレーターにはおなじみのオプションがある。これらを指定すればよい。

ここでは、UVMの1.1dのサンプルコードである$UVM_HOME/examples/simple/hello_worldで作成してみる。

なお、ここで$UVM_HOMEは/tmp/svparse/uvm-1.1dに設定してある。

XML作成は以下のように実行する。

tools/simshim.py +incdir+$UVM_HOME/src \

+incdir+$UVM_HOME/examples/simple/hello_world \

$UVM_HOME/examples/simple/hello_world/hello_world.sv

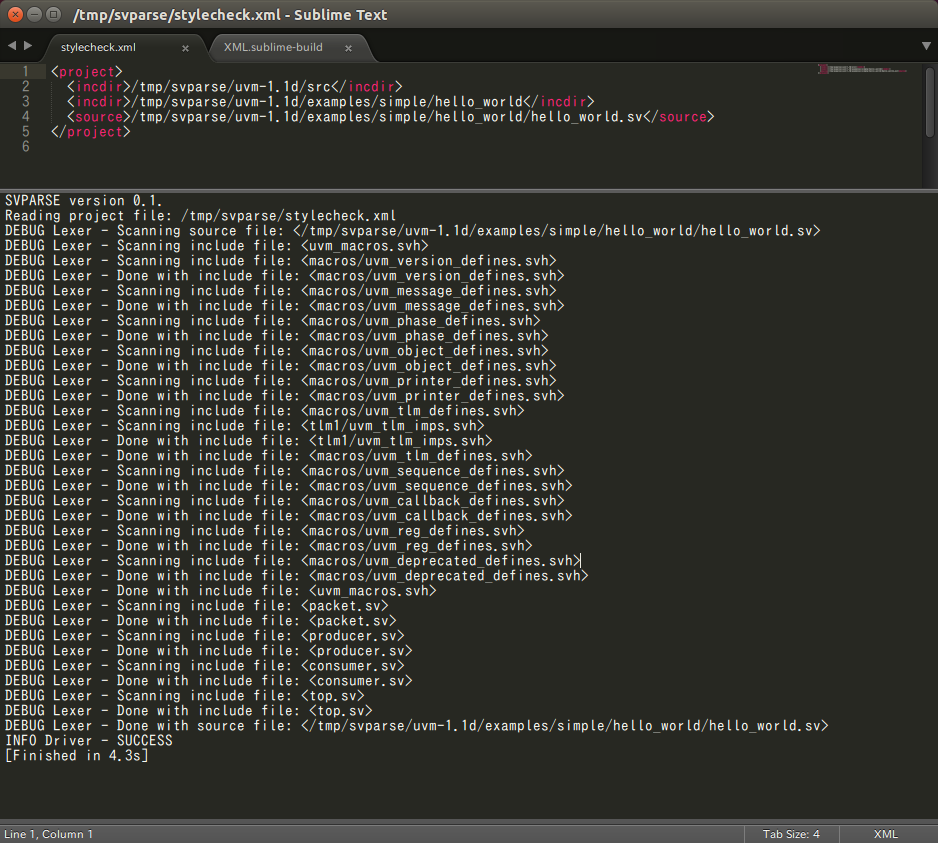

すると、カレントディレクトリに以下のようなXMLファイルが生成される。

<project>

<incdir>/tmp/svparse/uvm-1.1d/src</incdir>

<incdir>/tmp/svparse/uvm-1.1d/examples/simple/hello_world</incdir>

<source>/tmp/svparse/uvm-1.1d/examples/simple/hello_world/hello_world.sv</source>

</project>

ここからSublime Text

以前書いた感じで、XML用のビルド設定をJSONで記述し、ビルドシステムでXMLを指定する。

{

"cmd":["svparse", "${file}"]

}

そして、Sublime Textからstylecheck.xml開く。

ctrl+bを実行すると、svparserがSublime Textから呼び出され、以下のような感じでSystemVerilogファイルをパースしてくれる。

ModelSim-ASEとの違い

以前書いたModelSim-ASEと組み合わせたのと比較すると、違いは特にない (笑)。

むろん、tools/simshim.pyを使用することで、コードの依存関係をパースしてくれるXMLファイルを出力する分だけ、

Sublime Textのビルドファイルの内容はシンプルになるし、コマンドもワンステップで済むし、

大量のSystemVerilogファイルをコンパイルしていくとなると、svparseを使うメリットが出てくる。

ただし、現状のsvparseはシンタックスエラーがあった場合、メッセージがModelSim-ASEとあまり変わらない。

つまり、メッセージからシンタックス違反箇所を追うのが ちょっと大変である。

IncisiveとかVCSとか商用ツールと組み合わせるならば、Sconsでやった方がまだいいかなぁ…。

Javaは不要でPythonだけだし。

ああ、今だとそれにバージョン管理ツールのCommitと組み合わせてJenkinsですかね。

今後に期待

またそれかよ って感じだが、実際まだ開発中(0.1)だし、

手持ちのSystemVerilogコードでModelSim-ASEで通るコードがエラーになったりするので、致し方なし。

継続的にウォッチしておこうかと思う。

おわりに

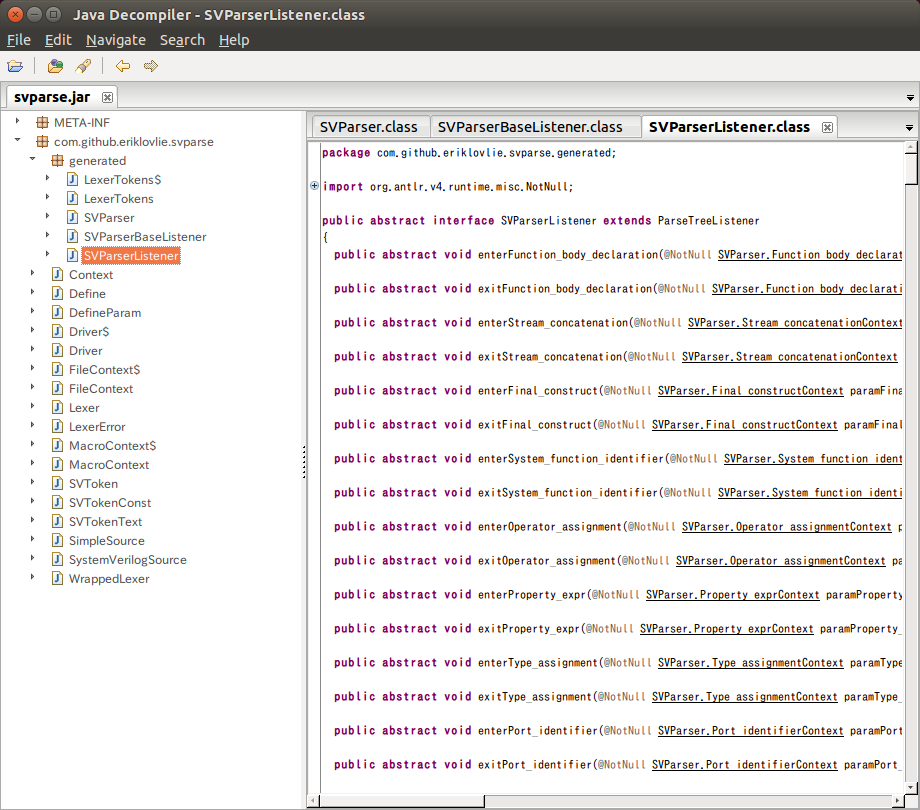

svparseのjarファイルをJD-GUIで覗いてみると、こんな感じ。

普通にANTLRをベースにしているようだ。